电子封装件及其制法的制作方法

本发明涉及一种半导体封装工艺,尤其涉及一种可提高可靠性的电子封装件及其制法。

背景技术:

1、随着电子产业的蓬勃发展,电子产品也逐渐迈向多功能、高性能的趋势。同时,目前应用于芯片封装领域的技术,包含有例如晶片级封装(wafer level packaging,简称wlp)、芯片尺寸构装(chip scale package,简称csp)、芯片直接贴附封装(direct chipattached,简称dca)或多芯片模块封装(multi-chip module,简称mcm)等封装型态的封装模块等。

2、图1a至图1e为现有半导体封装件1的制法的剖面示意图。

3、如图1a所示,形成一离形层100于一承载件10上。接着,置放多个半导体元件17于该离形层100上,其中,多个半导体元件17具有相对的作用面17a与非作用面17b,该作用面17a上具有多个电极垫170,且各该半导体元件17以其作用面17a粘着于该离形层100上。

4、如图1b所示,形成一如环氧树脂(epoxy)的包覆层18于该离形层100上,以包覆多个半导体元件17。

5、如图1c所示,通过该离形层100分离该承载件10与该半导体元件17,使该半导体元件17的作用面17a外露。

6、如图1d所示,形成一布线结构15于该包覆层18与该半导体元件17的作用面17a上,且该布线结构15包含至少一介电层150及结合该介电层150的布线层151,以令该布线层151电性连接该半导体元件17的电极垫170。接着,形成一防焊层16于该布线结构15上,且该防焊层15外露该布线层151的部分表面,以供结合如焊球的导电元件19。

7、如图1e所示,沿如图1d所示的切割路径l进行切单工艺,以获取多个半导体封装件1。

8、然而现有半导体封装件1中,由于该包覆层18采用环氧树脂,其与如铜材的金属材的结合力不佳,故于制作该布线层151前,需先于该包覆层18上制作一层如预浸材(prepreg,简称pp)的介电层150,因而大幅增加该布线结构15的制作时间与制作材料,导致制作成本难以降低。

9、再者,现有半导体封装件1中,由于该包覆层18采用环氧树脂,若需电性导通该包覆层18上下两侧,需先于该承载件10上电镀出导电柱,再以该包覆层18包覆该导电柱,之后进行研磨作业以外露出该导电柱的端面,故需进行铜柱工艺及研磨作业,因而不仅增加制作时间与制作材料,导致难以降低制作成本,且制作步骤繁琐,致使生产效率不佳。

10、另外,现有半导体封装件1中,由于该包覆层18采用环氧树脂,因而仅能采用单一个体(unit)规格或晶片级(wafer size)规格进行制作,因而难以提升效益,更无法降低生产成本,致使不利于量产。

11、因此,如何克服上述现有技术的种种问题,实已成为目前业界亟待克服的难题。

技术实现思路

1、鉴于上述现有技术的种种缺陷,本发明提供一种电子封装件及其制法,可至少部分地解决现有技术中的问题。

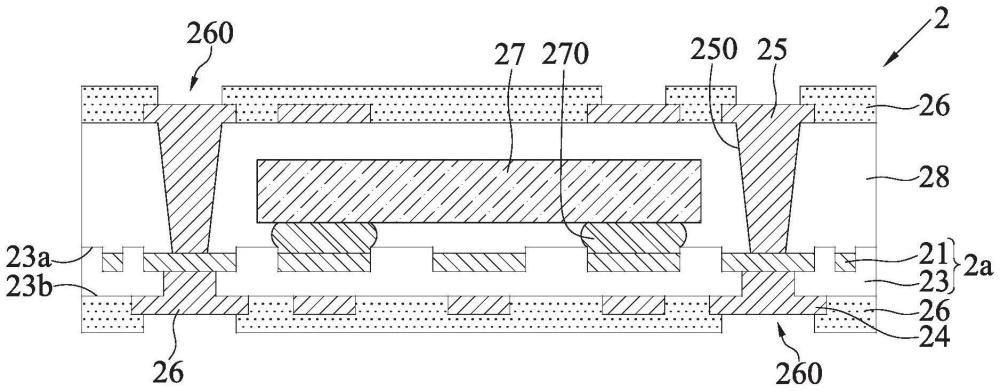

2、本发明的电子封装件,包括:线路部,其具有至少一绝缘层及结合该绝缘层的线路层,其中,该绝缘层定义有相对的第一表面与第二表面,以令该线路层外露于该绝缘层的第一表面;电子元件,其设于该线路部的绝缘层的第一表面上且电性连接该线路层;包覆层,其设于该线路部的绝缘层的第一表面上以包覆该电子元件,其中,该包覆层为味之素增层膜;以及布线层,其设于该包覆层上,其中,该布线层于该包覆层中形成有至少一电性连接该线路层的导电通孔。

3、本发明亦提供一种电子封装件的制法,包括:提供一线路部,其具有至少一绝缘层及结合该绝缘层的线路层,其中,该绝缘层定义有相对的第一表面与第二表面,以令该线路层外露于该绝缘层的第一表面;将电子元件设于该线路部的绝缘层的第一表面上,且该电子元件电性连接该线路层;形成包覆层于该线路部的绝缘层的第一表面上,以令该包覆层包覆该电子元件,其中,该包覆层为味之素增层膜;以及形成布线层于该包覆层上,且该布线层延伸至该包覆层中以形成至少一电性连接该线路层的导电通孔。

4、前述的电子封装件及其制法中,该电子元件为无源元件。

5、前述的电子封装件及其制法中,该电子元件通过多个导电凸块电性连接该线路层。

6、前述的电子封装件及其制法中,形成该包覆层的材质不同于形成该绝缘层的材质。

7、前述的电子封装件及其制法中,还包括形成另一布线层于该绝缘层的第二表面上,且于该绝缘层中形成有至少一电性连接该线路层与该另一布线层的导电盲孔。

8、由上可知,本发明的电子封装件及其制法中,主要通过abf材作为该包覆层,使该布线层能良好结合于该包覆层上,故相较于现有技术,本发明的制法可直接于该包覆层上制作布线层,而无需形成一用以结合该布线层的介电层,因而能有效节省制作时间与制作材料,以有效降低制作成本。

9、再者,本发明的制法可直接激光加工abf材,以形成导电通孔,故相较于现有技术,本发明的制法无需进行铜柱工艺及研磨作业,因而不仅能节省制作时间与制作材料以降低制作成本,且能大幅减少制作步骤,以利于提升生产效率。

10、另外,本发明的制法通过abf材作为该包覆层,因而可采用整版面(panel)规格,故相较于现有技术,本发明能大幅提升效益,并降低生产成本,以利于量产。

技术特征:

1.一种电子封装件,包括:

2.如权利要求1所述的电子封装件,其中,该电子元件为无源元件。

3.如权利要求1所述的电子封装件,其中,该电子元件通过多个导电凸块电性连接该线路层。

4.如权利要求1所述的电子封装件,其中,形成该包覆层的材质不同于形成该绝缘层的材质。

5.如权利要求1所述的电子封装件,其中,该电子封装件还包括形成于该绝缘层的第二表面上的另一布线层,且该另一布线层于该绝缘层中形成有至少一电性连接该线路层的导电盲孔。

6.一种电子封装件的制法,包括:

7.如权利要求6所述的电子封装件的制法,其中,该电子元件为无源元件。

8.如权利要求6所述的电子封装件的制法,其中,该电子元件通过多个导电凸块电性连接该线路层。

9.如权利要求6所述的电子封装件的制法,其中,形成该包覆层的材质不同于形成该绝缘层的材质。

10.如权利要求6所述的电子封装件的制法,其中,该制法还包括形成另一布线层于该绝缘层的第二表面上,且于该绝缘层中形成有至少一电性连接该线路层与该另一布线层的导电盲孔。

技术总结

本发明提出一种电子封装件及其制法。电子封装件包括于线路部上配置电子元件,且以ABF作为包覆层以包覆该电子元件,并将布线层设于该包覆层上及将导电通孔形成于该包覆层中,故通过ABF材作为该包覆层,使该布线层能良好结合于该包覆层上。

技术研发人员:赖建光,张垂弘,陈敏尧

受保护的技术使用者:芯爱科技(南京)有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!