一种片上可集成的氮化镓基雪崩光电探测器及其制备方法

1.本发明涉及半导体技术领域,具体涉及一种片上可集成的氮化镓基雪崩光电探测器及其制备方法。

背景技术:

2.紫外光是指波长在10~400nm之间的电磁波或光线的总称,人肉眼看不到,但却实实在在存在于人们生活的各个方面,例如紫外杀菌、验钞、医疗检查等,人们已能够将这看不到的紫外光应用于多个领域,进行着不同的工作,由于紫外光广泛存在于各种场所,且可作为一些重要的指标,因此人们研发出了专门探测紫外光的光电设备,紫外光电探测器,其在通信、军事、市政安全等多个领域都有着重要价值,例如紫外告警与制导、碳氢化合物燃烧火焰的探测、探测生化武器、紫外天文学的研究、短距离的通信以及皮肤病的治疗、生化基因的检测、癌症检查、辐射测量等。随着科学技术的发展,人们对紫外探测的认识逐渐加深,也渐渐意识到紫外探测器的重要性,因此对其进行了深入研究,研发出了多种结构的紫外探测器,其中紫外雪崩探测器的特点在于能对微弱的紫外信号做出快速响应,且带宽大,因此在生物检测、医疗和通信方面应用极为广泛。

3.由于氮化镓基材料具有禁带宽度大、热导率高、耐高温、抗辐射、耐酸碱、高强度和高硬度等特性,在高亮度蓝、绿、紫、紫外和白光二极管,蓝、紫色激光器以及抗辐射、耐高温、大功率微波器件等领域均有着广泛的应用潜力和良好的市场前景。在紫外探测领域中,相比起传统的真空倍增管和硅半导体探测器,氮化镓基紫外雪崩光电探测器具有体积小、重量轻、寿命长、抗震性好、工作电压低、耐高温、耐腐蚀、抗辐照、量子效率高和无需滤光片等优点,成为光电探测领域的研究热点。

4.近年来,mbe(molecular beam epitaxy,分子束外延)、mocvd(metal-organic chemical vapor deposition,金属有机化合物化学气相沉淀)和ald(atom layer deposition,原子外延)等新的半导体外延工艺技术的相继诞生,使得精确控制半导体材料生长成为可能,金属材料的沉积工艺更加成熟,材料生长更均匀,这些外延技术已经应用于

ⅲ‑ⅴ

族化合物半导体材料的生长,并在各个工艺厂有成熟的工艺制程。

5.目前,以氮化镓基材料制备的紫外雪崩光电探测器大都以蓝宝石、sic或者si为衬底进行外延生长,最终形成所需的器件结构,如公开号为cn105655437a的专利公布的一种紫外雪崩光电探测器,结构为以硅为衬底,硅为雪崩区、algan为吸收层,并以gan作为缓冲层,其具有相对较低的击穿电压;公开号为cn104051561a的专利公布了一种氮化镓基紫外雪崩光电探测器,以蓝宝石为衬底、alingan作为氮化镓基紫外雪崩光电探测器的吸收区和倍增区,吸收区和倍增区被a1组分渐变的四元化合物alingan所分离;公开号为cn102244135a的专利公布了一种pin倒置结构紫外雪崩光电探测器及其制备方法,以alingan作为器件的吸收层和雪崩区,并以p型轻掺杂gan作为保护环,实现了较高性能的氮化镓雪崩光电探测器。

6.随着微电子产业的发展和各应用领域越来越苛刻的性能需求,对光电子器件的集

成度提出了更高的要求。然而,上述方法中提到的雪崩光电探测器的集成方式为各个分立器件的chip-chip连接,降低了器件的集成度,同时还会降低其响应速度和带宽值、并增大速度适配比;其次,在硅、蓝宝石或碳化硅衬底上外延生长的制备工艺,由于衬底材料和外延材料存在晶格失配,会使得器件的关键区域产生大量的缺陷,这将严重影响器件的工作性能和寿命;虽然对可见光及近红外波段有较好的探测能力,但缺乏对深紫外光波段的探测和抗电磁干扰能力。

技术实现要素:

7.为了解决现有技术中存在的上述问题,本发明提供了一种片上可集成的氮化镓基雪崩光电探测器及其制备方法。本发明要解决的技术问题通过以下技术方案实现:

8.本发明的一个实施例提供了一种片上可集成的氮化镓基雪崩光电探测器的制备方法,所述制备方法包括:

9.制备p型掺杂的氮化镓层;

10.在所述p型掺杂的氮化镓层上制备第一n型掺杂的氮化镓层;

11.在所述第一n型掺杂的氮化镓层上制备第二n型掺杂的氮化镓层;

12.在所述第二n型掺杂的氮化镓层上沉积阴极材料形成阴极,以制备得到包括层叠设置的p型掺杂的氮化镓层、第一n型掺杂的氮化镓层、第二n型掺杂的氮化镓层和阴极的外延片;

13.通过有机键合方法将所述外延片的阴极键合在soi衬底上;

14.在所述p型掺杂的氮化镓层上沉积阳极材料形成阳极;

15.在所述p型掺杂的氮化镓层两端内制备硅局部氧化隔离层,且所述硅局部氧化隔离层的底端位于所述第一n型掺杂的氮化镓层内,完成氮化镓基雪崩光电探测器的制备。

16.在本发明的一个实施例中,所述p型掺杂的氮化镓层的掺杂浓度大于所述第二n型掺杂的氮化镓层的掺杂浓度,所述第二n型掺杂的氮化镓层的掺杂浓度大于所述第一n型掺杂的氮化镓层的掺杂浓度。

17.在本发明的一个实施例中,所述p型掺杂的氮化镓层的掺杂浓度为4

×

10

17

~5

×

10

17

cm-3

,所述第一n型掺杂的氮化镓层的掺杂浓度为1

×

10

15

~4

×

10

15

cm-3

,所述第二n型掺杂的氮化镓层的掺杂浓度为1

×

10

17

~4

×

10

17

cm-3

。

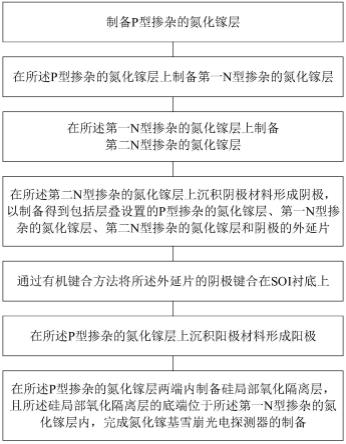

18.在本发明的一个实施例中,在所述p型掺杂的氮化镓层上制备第一n型掺杂的氮化镓层,包括:

19.将ga(ch3)3、nh3均匀扩散到所述p型掺杂的氮化镓层的表面;

20.对所述p型掺杂的氮化镓层进行加热,在所述p型掺杂的氮化镓层的表面生长出第一gan材料,并用h2se对所述第一gan材料进行掺杂,使所述第一gan材料呈n型;

21.在第一预设温度下,反复采用外延工艺使所述第一gan材料生长至第一预设厚度,然后对所述第一预设厚度的第一gan材料进行离子注入,以制备第一n型掺杂的氮化镓层。

22.在本发明的一个实施例中,在所述第一n型掺杂的氮化镓层上制备第二n型掺杂的氮化镓层,包括:

23.将ga(ch3)3、nh3均匀扩散到所述第一n型掺杂的氮化镓层的表面;

24.对所述第一n型掺杂的氮化镓层进行加热,在所述第一n型掺杂的氮化镓层的表面

生长出第二gan材料,并用h2se对所述第二gan材料进行掺杂,使所述第二gan材料呈n型;

25.在第一预设温度下,反复采用外延工艺使所述第二gan材料生长至预设厚度,然后对所述预设厚度的第一gan材料进行离子注入,以制备第一n型掺杂的氮化镓层。

26.在本发明的一个实施例中,通过有机键合方法将所述外延片的阴极键合在soi衬底上,包括:

27.将所述外延片分割成若干外延子片;

28.用热塑性粘合剂或热释胶带将所述外延子片安装在玻璃载体上;

29.对所述外延子片和所述soi衬底进行清洗;

30.在所述soi衬底上旋涂sog;

31.在第二预设温度下对旋涂sog的soi衬底进行加热,以去除sog中的液态溶剂;

32.在真空环境中,将所述外延子片的阴极键合在所述soi衬底涂覆有sog的一侧;

33.在第三预设温度下,对键合后的所述外延子片进行加热修复,以在所述soi衬底上完成所述外延子片的键合。

34.在本发明的一个实施例中,在所述p型掺杂的氮化镓层两端内制备硅局部氧化隔离层,包括:

35.使用光刻和干法刻蚀工艺对器件表面图形化后,在所述p型掺杂的氮化镓层两端沉积teos以制备硅局部氧化隔离层,且所述硅局部氧化隔离层的底端位于所述第一n型掺杂的氮化镓层内。

36.在本发明的一个实施例中,所述p型掺杂的氮化镓层的厚度小于所述第二n型掺杂的氮化镓层的厚度,所述第二n型掺杂的氮化镓层的厚度小于所述第一n型掺杂的氮化镓层的厚度。

37.在本发明的一个实施例中,所述p型掺杂的氮化镓层的厚度为0.2~1μm,所述第一n型掺杂的氮化镓层的厚度为5~9μm,所述第二n型掺杂的氮化镓层为2~5μm。

38.本发明实施例还提供一种片上可集成的氮化镓基雪崩光电探测器,所述氮化镓基雪崩光电探测器利用上述任一项实施例所述的制备方法制备而成,所述氮化镓基雪崩光电探测器包括:

39.soi衬底;

40.阴极,位于所述soi衬底上;

41.第二n型掺杂的氮化镓层,位于所述阴极上;

42.第一n型掺杂的氮化镓层,位于所述第二n型掺杂的氮化镓层上;

43.p型掺杂的氮化镓层,位于所述第一n型掺杂的氮化镓层上;

44.硅局部氧化隔离层,位于所述p型掺杂的氮化镓层的两端,且所述硅局部氧化隔离层的下表面在所述p型掺杂的氮化镓层的上表面的下方;阳极,位于所述p型掺杂的氮化镓层上。

45.与现有技术相比,本发明的有益效果在于:

46.1、本发明利用半导体键合技术,将氮化镓外延基片集成于soi衬底,从而很好的提高器件的集成度,相较于各个分立器件的chip-chip连接具有更低的速度适配比、更高的响应速率和更大的带宽值。

47.2、本发明的衬底和外延基片之间采用半导体键合工艺代替直接在衬底通过外延

生长方式制备器件的工艺,因此可以避免由衬底材料和外延生长材料之间存在较高的晶格失配及相差较大膨胀系数而导致生长出来的晶体质量差的问题,保证雪崩光电探测器的电信号向tia电路的完整传输。

48.3、本发明通过全新结构设计和

ⅲ‑ⅴ

族材料的使用,器件的雪崩区、光吸收层为氮化镓材料的n型掺杂和p型掺杂制作而成,因此可实现深紫外波段的探测能力和抗电磁干扰能力,并通过优化р型区和n型区的掺杂浓度和厚度使得器件具有较深的探测深度和较低的击穿电压;同时,soi衬底使得雪崩光电器件具有更强抗辐射特性。

49.以下将结合附图及实施例对本发明做进一步详细说明。

附图说明

50.图1是本发明实施例提供的一种片上可集成的氮化镓基雪崩光电探测器的制备方法的流程示意图;

51.图2a-图2g是本发明实施例提供的一种片上可集成的氮化镓基雪崩光电探测器的制备方法的过程示意图;

52.图3是本发明实施例提供的一种片上可集成的氮化镓基雪崩光电探测器的结构示意图。

具体实施方式

53.下面结合具体实施例对本发明做进一步详细的描述,但本发明的实施方式不限于此。

54.需要说明的是,本实施例中提到的“上”“下”“左”“右”为该雪崩光电探测器处于图示状态时的位置关系,“长”为该雪崩光电探测器处于图示状态时的横向尺寸,“厚”为该雪崩光电探测器处于图示状态时的纵向尺寸。

55.实施例一

56.目前,现有的氮化镓基雪崩光电探测器集成度低,并且速度适配比高、带宽值小、响应速度低;在硅、蓝宝石或碳化硅衬底上外延生长的制备工艺,由于衬底材料和外延材料存在晶格失配,会使得器件的关键区域产生大量的缺陷,这将严重影响器件的工作性能和寿命;对可见光及近红外波段有较好的探测能力,缺乏对深紫外光波段的探测和抗电磁干扰能力。基于此本发明提供了一种片上可集成的氮化镓基雪崩光电探测器的制备方法,具体请参见图1、图2a-图2g,图1是本发明实施例提供的一种片上可集成的氮化镓基雪崩光电探测器的制备方法的流程示意图,图2a-图2g是本发明实施例提供的一种片上可集成的氮化镓基雪崩光电探测器的制备方法的过程示意图。本发明实施例提供一种片上可集成的氮化镓基雪崩光电探测器(gan apd,gan avalanche photodetector)的制备方法,该制备方法包括:

57.步骤1、请参见图2a,制备p型掺杂的氮化镓层1。

58.具体的,采用mocvd(metal-organic chemical vapor deposition,金属有机化合物化学气相沉淀)方式、mg离子注入工艺以及高温退火工艺,得到p型掺杂的氮化镓层1。

59.步骤2、请参见图2b,在p型掺杂的氮化镓层1上制备第一n型掺杂的氮化镓层2。

60.在可选实施例中,步骤2具体可包括步骤2.1-步骤2.3,其中:

61.步骤2.1、将ga(ch3)3、nh3均匀扩散到p型掺杂的氮化镓层1的表面。

62.具体而言,将ga(ch3)3、nh3通入mocvd系统中,通过滞流层均匀扩散到p型掺杂的氮化镓层1表面。

63.步骤2.2、对p型掺杂的氮化镓层1进行加热,在p型掺杂的氮化镓层的表面生长出第一gan材料,并用h2se对第一gan材料进行掺杂,使第一gan材料呈n型。

64.步骤2.3、在第一预设温度下,反复采用外延工艺使第一gan材料生长至第一预设厚度,然后对第一预设厚度的第一gan材料进行多次离子注入和推进(drive-in),以制备第一n型掺杂的氮化镓层2。

65.可选的,第一预设温度为1100℃。

66.步骤3、请参见图2c,在第一n型掺杂的氮化镓层2上制备第二n型掺杂的氮化镓层3。

67.在可选实施例中,步骤3具体可包括步骤3.1-步骤3.3,其中:

68.步骤3.1、将ga(ch3)3、nh3均匀扩散到p型掺杂的氮化镓层1的表面。

69.具体而言,将ga(ch3)3、nh3通入mocvd系统中,通过滞流层均匀扩散到p型掺杂的氮化镓层1表面。

70.步骤3.2、对第一n型掺杂的氮化镓层2进行加热,在第一n型掺杂的氮化镓层2的表面生长出第二gan材料,并用h2se对第二gan材料进行掺杂,使第二gan材料呈n型。

71.步骤3.3、在第一预设温度下,反复采用外延工艺使第二gan材料生长至第二预设厚度,然后对第二预设厚度的第二gan材料进行多次离子注入和推进(drive-in),以制备第二n型掺杂的氮化镓层3。

72.可选的,p型掺杂的氮化镓层1的掺杂浓度大于第二n型掺杂的氮化镓层3的掺杂浓度,第二n型掺杂的氮化镓层3的掺杂浓度大于第一n型掺杂的氮化镓层2的掺杂浓度。由此,可形成pin结,其可产生雪崩光电效应。

73.优选的,p型掺杂的氮化镓层1的掺杂浓度为4

×

10

17

~5

×

10

17

cm-3

,第一n型掺杂的氮化镓层2的掺杂浓度为1

×

10

15

~4

×

10

15

cm-3

,第二n型掺杂的氮化镓层3的掺杂浓度为1

×

10

17

~4

×

10

17

cm-3

。

74.进一步优选的,p型掺杂的氮化镓层1的掺杂浓度为5

×

10

17

cm-3

,第一n型掺杂的氮化镓层2的掺杂浓度为4

×

10

15

cm-3

,第二n型掺杂的氮化镓层3的掺杂浓度为4

×

10

17

cm-3

。

75.可选的,p型掺杂的氮化镓层1的厚度小于第二n型掺杂的氮化镓层3的厚度,第二n型掺杂的氮化镓层3的厚度小于第一n型掺杂的氮化镓层2的厚度。由此可以使第一n型掺杂的氮化镓层2接近于本征掺杂,雪崩区位置更靠近第二n型掺杂的氮化镓层3,达到能够吸收对应波长的深紫外光的效果。

76.优选的,p型掺杂的氮化镓层1的厚度为0.2~1μm,第一n型掺杂的氮化镓层2的厚度为5~9μm,第二n型掺杂的氮化镓层3为2~5μm。

77.进一步优选的,p型掺杂的氮化镓层1的厚度为0.5μm,第一n型掺杂的氮化镓层2的厚度为7.5μm,第二n型掺杂的氮化镓层3为4μm。

78.因此,本实施例的氮化镓基雪崩光电探测器器件的雪崩区、光吸收层为通过氮化镓材料的n型掺杂和p型掺杂制作而成,其具有抗辐照的特性,进而具有抗电磁干扰能力,同时其对深紫外波段的吸收系数高,因此可实现深紫外波段的探测和抗电磁干扰,并通过按

照上述方式设置р型区和n型区的掺杂浓度和厚度使得器件的雪崩区范围宽,同时通过上述掺杂浓度设置形成的pn结可使其有较低的击穿电压,因此所形成的器件同时具有较深的探测深度和较低的击穿电压。

79.步骤4、请参见图2d,在第二n型掺杂的氮化镓层3上沉积阴极材料形成阴极4,以制备得到包括层叠设置的p型掺杂的氮化镓层1、第一n型掺杂的氮化镓层2、第二n型掺杂的氮化镓层3和阴极4的外延片。

80.具体的,采用cvd(chemical vapordeposition,化学气相沉积)工艺在第二n型掺杂的氮化镓层3上沉积aln形成阴极4。

81.步骤5、请参见图2e,通过有机键合方法将外延片的阴极键合在soi(silicon-on-insulator,绝缘衬底上的硅)衬底5上。

82.在可选实施例中,步骤5具体可包括步骤5.1-步骤5.7,其中:

83.步骤5.1、将外延片分割成若干外延子片。

84.步骤5.2、用热塑性粘合剂或热释胶带将外延子片安装在玻璃载体上。

85.步骤5.3、对外延子片和soi衬底进行清洗。

86.步骤5.4、在soi衬底上旋涂sog(spin on glass,旋涂玻璃)。

87.步骤5.5、在快速热处理(rtp,rapid thermal processing)设备中,在第二预设温度下对旋涂sog的soi衬底进行加热,以去除sog中的液态溶剂,在soi衬底表面留下固化后的材料。

88.可选的,第二预设温度为150℃。

89.步骤5.6、在真空环境中,将外延子片的阴极键合在soi衬底涂覆有sog的一侧。

90.步骤5.7、在第三预设温度下,对键合后的外延子片进行加热修复,以在soi衬底上完成外延子片的键合。

91.可选的,为了去除工艺中产生的缺陷和应力,因此在300℃下,对键合后的外延子片进行加热修复,由此可以获得高强度、低应力及稳定的键合。

92.因此,本实施例利用半导体键合技术,将氮化镓外延基片集成于soi衬底,从而很好的提高器件的集成度,相较于各个分立器件的chip-chip连接具有更低的速度适配比、更高的响应速率和更大的带宽值;同时,半导体键合工艺代替了直接在衬底上通过外延生长方式制备器件的工艺,可以避免由衬底材料和外延生长材料之间存在较高的晶格失配及相差较大膨胀系数而导致生长出来的晶体质量差的问题,保证雪崩光电探测器的电信号向tia电路的完整传输。。

93.需要说明的是,在步骤5.7之前,需要将玻璃载体去除。

94.步骤6、请参见图2f,在p型掺杂的氮化镓层1上沉积阳极材料形成阳极6。

95.具体的,采用cvd(chemical vapordeposition,化学气相沉积)工艺在p型掺杂的氮化镓层1上沉积aln形成阳极6。

96.步骤7、请参见图2g,在p型掺杂的氮化镓层1两端内制备硅局部氧化隔离(locos,local oxidation of silicon)层7,且硅局部氧化隔离层7的底端位于第一n型掺杂的氮化镓层2内,完成氮化镓基雪崩光电探测器的制备。

97.具体的,使用光刻和干法刻蚀工艺对器件表面图形化后,在p型掺杂的氮化镓层1两端沉积teos(硅酸乙酯)以制备硅局部氧化隔离层7,且硅局部氧化隔离层7的底端位于第

一n型掺杂的氮化镓层2内。

98.光电器件需要与控制电路集成在一起,而本发明采用的键合技术简化了现有的工艺,降低了光子集成的难度,本发明由于采用的是利于器件集成的soi衬底,soi基器件是一种平坦的多层结构,并且利用半导体键合技术直接将氮化镓外延片集成于soi衬底,由此很容易实现三维立体集成,充分利用硅片面积,实现更高密度的集成,因此,本发明的soi与gan键合技术,有效地提升了器件的集成度,实现了片上可集成gan apd,与现有的氮化镓雪崩光电探测器中各个分立器件的chip-chip连接相比,本发明的氮化镓雪崩光电探测器具有更低的速度适配比,更高的响应速率和更大的带宽值。

99.目前,在现有的氮化镓基雪崩光电探测器制造工艺中,由于衬底材料和外延材料的晶格常数不同,会出现晶格失配现象,并且两种材料的热膨胀系数相差较大,最终导致在衬底外延生长出来的外延层质量差,这会严重影响光电器件的工作性能和使用寿命,基于此,本发明在gan apd与soi衬底之间采用键合技术代替直接在衬底上外延生长的制备工艺,因此可以避免由衬底材料和外延生长材料之间存在较高的晶格失配及相差较大膨胀系数而导致生长出来的晶体质量差的问题,保证了gan apd器件电信号向衬底中tia电路的完整传输。

100.本发明所制备的雪崩光电探测器采用gan材料(即第一n型掺杂的氮化镓层和第二n型掺杂的氮化镓层)组成有源区(也即雪崩区),当深紫外光线照射在光吸收层(即p型掺杂的氮化镓层)时,位于半导体价带的电子会吸收足够多的光子能量,从而发生能级跃迁进入导带形成电子空穴对(光生载流子)。由于内部存在外加工作电压形成的电场,产生的电子空穴对将在电场作用下加速运动,在有源区内注入载流子,并与晶格共价键不断发生碰撞,激发出新的电子空穴对,这个过程将不断进行下去,最后造成载流子数目的雪崩式倍增。本发明通过这种方式,从而保证了器件在击穿电压下能够产生雪崩效应,达到将接收光信号转化为电信号的作用,电信号通过soi衬底上的si材料层传输到tia(trans-impedance amplifier,跨阻抗放大器)电路,保证雪崩光电探测器的电信号向tia电路的完整传输。因此,本发明通过全新结构设计和

ⅲ‑ⅴ

族材料的使用,即器件的雪崩区、光吸收层是通过氮化镓材料的n型掺杂和p型掺杂制作而成,因此可实现深紫外波段的探测和抗电磁干扰,并通过优化р型区和n型区的掺杂浓度和厚度使得器件具有较深的探测深度和较低的击穿电压。

101.此外,本发明采用soi衬底作为衬底材料,可以使得氮化镓雪崩光电探测器具有更强的抗辐射特性,因此也可应用于航空航天通信、量子通信等领域。

102.本发明提供了片上gan apd器件与集成电路共用soi衬底的制造解决方案,为实现与cmos工艺相兼容的大规模甚至超大规模的光子集成提供了基础,从而可以推进高可靠性、低损耗且低成本的高密度数据传输系统的发展。

103.实施例二

104.请参见图3,图3是本发明实施例提供的一种片上可集成的氮化镓基雪崩光电探测器的结构示意图。本发明在上述实施例的基础上还提供一种片上可集成的氮化镓基雪崩光电探测器,该氮化镓基雪崩光电探测器由上述实施例的制备方法制备而成,氮化镓基雪崩光电探测器具体包括:

105.soi衬底5;

106.阴极4,位于soi衬底5上;

107.第二n型掺杂的氮化镓层3,位于阴极4上;

108.第一n型掺杂的氮化镓层2,位于第二n型掺杂的氮化镓层3上;

109.p型掺杂的氮化镓层1,位于第一n型掺杂的氮化镓层2上;

110.硅局部氧化隔离层7,位于p型掺杂的氮化镓层1的两端,且硅局部氧化隔离层7的下表面在p型掺杂的氮化镓层1的上表面的下方;

111.阳极6,位于p型掺杂的氮化镓层1上。

112.其中,雪崩区即有源区由第一n型掺杂的氮化镓层2和第二n型掺杂的氮化镓层3构成,p型掺杂的氮化镓层1为光吸收层,工作在深紫外波段200-365nm下,具有非常好的雪崩效应。

113.优选的,第一n型掺杂的氮化镓层2和第二n型掺杂的氮化镓层3的厚度分别为7.5和4μm,掺杂浓度分别为4

×

10

15

和4

×

10

17

cm-3

;p型掺杂的氮化镓层1的厚度为0.5μm,掺杂浓度为5

×

10

17

cm-3

,硅局部氧化隔离层7的厚度为1μm;soi衬底的厚度为725μm。氮化镓基雪崩光电探测器的雪崩区主要位于第一n型掺杂的氮化镓层2和第二n型掺杂的氮化镓层3两层中的下部分,因此本发明设计的氮化镓基雪崩光电探测器可以保证雪崩区主要集中在第一n型掺杂的氮化镓层2和第二n型掺杂的氮化镓层3。

114.在本发明的描述中,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

115.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。此外,本领域的技术人员可以将本说明书中描述的不同实施例或示例进行接合和组合。

116.尽管在此结合各实施例对本发明进行了描述,然而,在实施所要求保护的本发明过程中,本领域技术人员通过查看所述附图、公开内容、以及所附权利要求书,可理解并实现所述公开实施例的其他变化。在权利要求中,“包括”(comprising)一词不排除其他组成部分或步骤,“一”或“一个”不排除多个的情况。单个处理器或其他单元可以实现权利要求中列举的若干项功能。相互不同的从属权利要求中记载了某些措施,但这并不表示这些措施不能组合起来产生良好的效果。

117.以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下所进行的修改都应当视为属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1