碳化硅半导体元件的制作方法

本发明是关于一种碳化硅半导体元件,且特别关于一种碳化硅功率半导体元件。

背景技术:

1、碳化硅(sic)肖特基整流器(或肖特基二极管(schottky barrier diodes,sbd))是单极元件,与传统双极硅pin整流器相比,在开关模式电源(switch-mode powersupplies,smps)、逆变器以及转换器等许多电力电子的应用中可提供更低的损耗并提高效率。然而,由于碳化硅的能隙为3.2ev,高于硅的1.1ev能隙,因此碳化硅肖特基二极管(sicsbd)的典型切入电压(整流器开始传导电流的位置)约为0.9v~1v,高于硅移相开关二极管(si pin diodes)的典型切入电压(约0.7v)。与硅移相开关二极管相比,碳化硅肖特基二极管较高的切入电压会增加碳化硅肖特基二极管的传导损耗,并且对轻载效率(light-loadefficiency)产生不利影响。

技术实现思路

1、根据本发明一实施例的碳化硅半导体元件,包括:一碳化硅基板,具有一第一导电类型;一漂移层,具有该第一导电类型且设置于该碳化硅基板上;多个第一掺杂区,具有一第二导电类型,该第一掺杂区形成于该漂移层的一表面附近,每个该第一掺杂区彼此间隔;多个第二掺杂区,具有该第一导电类型,该第二掺杂区形成于该漂移层的该表面附近且位于该些第一掺杂区之间;以及一第一金属层,设置于该漂移层的该表面上,该第一金属层与该第二掺杂区形成一欧姆接触;其中,该漂移层具有一第一掺杂浓度,该第一掺杂浓度具有该第一导电类型,每个该第二掺杂区具有一第二掺杂浓度,该第二掺杂浓度具有该第一导电类型,该第二掺杂浓度等于或高于该第一掺杂浓度;以及其中,每个该第一掺杂区具有一第一深度,每个该第二掺杂区具有一小于该第一深度的第二深度。

2、在一实施例中,每个该第一掺杂区具有一第三掺杂浓度,该第三掺杂浓度具有该第二导电类型,并且在该些第一掺杂区之间提供有一第一间距,其中该第一掺杂区的该第一深度、该第一掺杂区的该第三掺杂浓度以及该漂移层的该第一掺杂浓度被配置为当对该碳化硅半导体元件施以反向偏压时,该漂移层在该第一掺杂区之间的一区域被完全耗尽以夹止一漏电流。

3、在一实施例中,还包括一第二金属层,该第二金属层设置在该第一金属层以及该第二掺杂区上,且该第二金属层与该第二掺杂区的一部分形成一肖特基接触。

4、在一实施例中,还包括一氧化层,该氧化层设置于该第二掺杂区的一部分上。

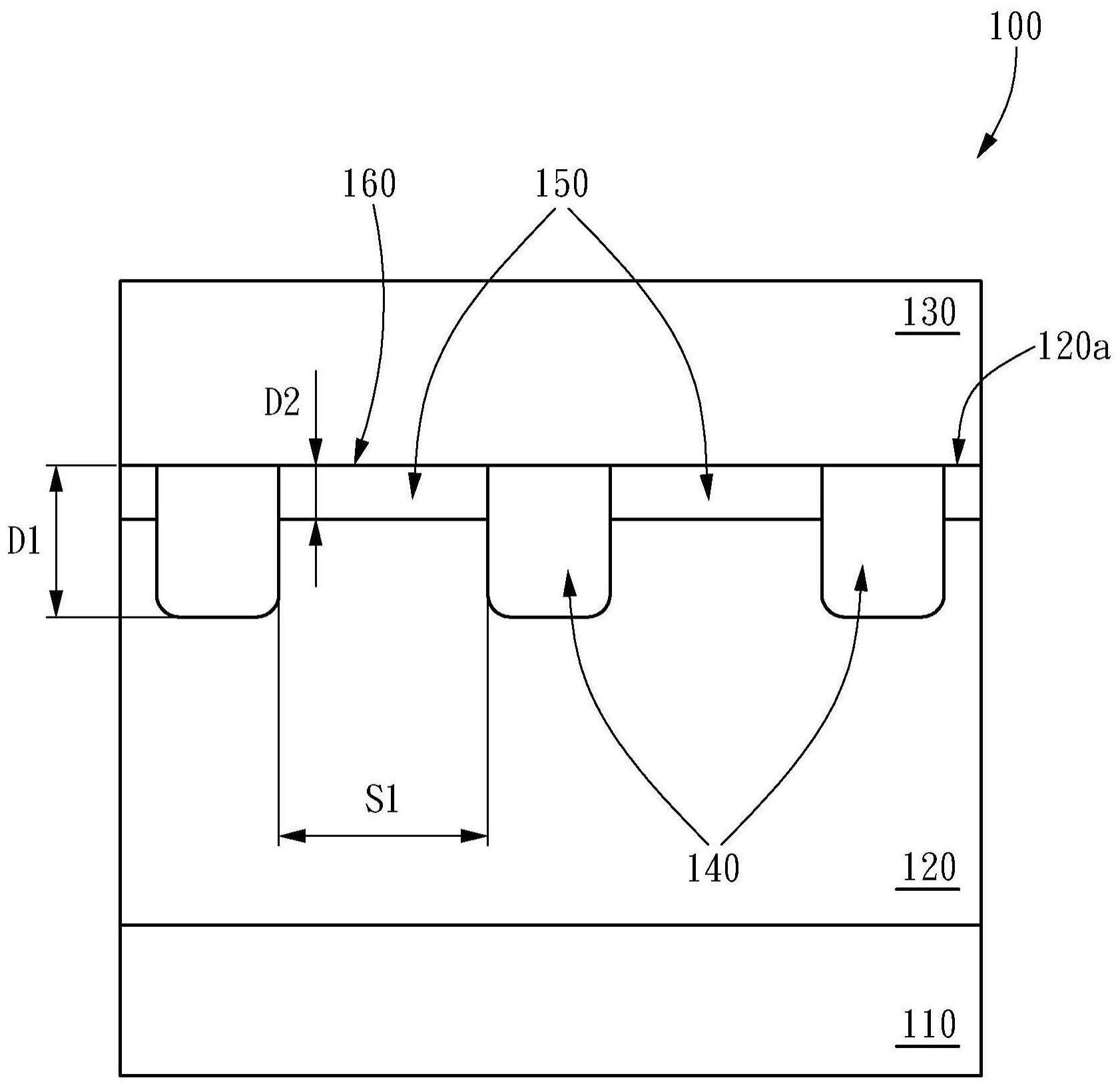

5、根据本发明另一实施例的碳化硅半导体元件,包括:一碳化硅基板,具有一第一导电类型;一漂移层,具有该第一导电类型且设置于该碳化硅基板上;多个凹陷部,该凹陷部从该漂移层的一表面凹陷,每个该凹陷部沿着该漂移层的该表面彼此间隔;多个第一掺杂区,该第一掺杂区具有一第二导电类型且形成于该凹陷部的一底部的下方;多个第二掺杂区,该第二掺杂区具有一第一导电类型,该第二掺杂区形成于该漂移层的该表面附近并且在该些凹陷部之间;以及一第一金属层,该第一金属层填充至该凹陷部中并与该第二掺杂区形成一欧姆接触;其中,该漂移层具有一第一掺杂浓度,该第一掺杂浓度具有该第一导电类型,每个该第二掺杂区具有一第二掺杂浓度,该第二掺杂浓度具有该第一导电类型,该第二掺杂浓度等于或高于该第一掺杂浓度;以及其中,每个该凹陷部具有一第三深度,每个该第二掺杂区具有一小于该第三深度的第二深度。

6、在一实施例中,每个该第一掺杂区具有一第三掺杂浓度,该第三掺杂浓度具有该第二导电类型,并且在该凹陷部之间提供有一间隔,其中该第一掺杂区的该第三掺杂浓度以及该漂移层的该第一掺杂浓度被配置为当向该碳化硅半导体元件施加反向偏压时,该漂移层在该些凹陷部之间的一区域被完全耗尽以夹止一漏电流。

7、在一实施例中,位于该凹陷部中的该第一金属层沿着该凹陷部及该漂移层之间的一侧壁与该漂移层形成一肖特基接触。

8、在一实施例中,该第一掺杂区向上延伸以邻接该凹陷部的一侧壁。

9、在一实施例中,还包括一多晶硅层,该多晶硅层设置在该凹陷部的一内表面上。

10、基于该碳化硅半导体元件的结构,提供在正向偏压下的低导通功率损耗。凭借在该区域的耗尽,即使是在正向偏压条件下的低开启电压,也可以实现阻断漏电流并且可以降低反向偏压下的漏电流。通过利用这种特性,可以实现低拐点电压或准无拐点电压的碳化硅整流器。

技术特征:

1.一种碳化硅半导体元件,其特征在于,包括:

2.根据权利要求1所述的碳化硅半导体元件,其特征在于,每个该第一掺杂区具有一第三掺杂浓度,该第三掺杂浓度具有该第二导电类型,并且在多个该第一掺杂区之间提供有一第一间距,其中该第一掺杂区的该第一深度、该第一掺杂区的该第三掺杂浓度以及该漂移层的该第一掺杂浓度被配置为当对该碳化硅半导体元件施以反向偏压时,该漂移层在该第一掺杂区之间的一区域被完全耗尽以夹止一漏电流。

3.根据权利要求1所述的碳化硅半导体元件,其特征在于,还包括一第二金属层,该第二金属层设置在该第一金属层以及该第二掺杂区上,且该第二金属层与该第二掺杂区的一部分形成一肖特基接触。

4.根据权利要求1所述的碳化硅半导体元件,其特征在于,还包括一氧化层,该氧化层设置于该第二掺杂区的一部分上。

5.一种碳化硅半导体元件,其特征在于,包括:

6.根据权利要求5所述的碳化硅半导体元件,其特征在于,每个该第一掺杂区具有一第三掺杂浓度,该第三掺杂浓度具有该第二导电类型,并且在该凹陷部之间提供有一间隔,其中该第一掺杂区的该第三掺杂浓度以及该漂移层的该第一掺杂浓度被配置为当向该碳化硅半导体元件施加反向偏压时,该漂移层在多个该凹陷部之间的一区域被完全耗尽以夹止一漏电流。

7.根据权利要求5所述的碳化硅半导体元件,其特征在于,位于该凹陷部中的该第一金属层沿着该凹陷部及该漂移层之间的一侧壁与该漂移层形成一肖特基接触。

8.根据权利要求5所述的碳化硅半导体元件,其特征在于,该第一掺杂区向上延伸以邻接该凹陷部的一侧壁。

9.根据权利要求5所述的碳化硅半导体元件,其特征在于,还包括一多晶硅层,该多晶硅层设置在该凹陷部的一内表面上。

技术总结

一种碳化硅半导体元件,包括一碳化硅基板、一设置于该基板上的漂移层、复数形成于该漂移层的一表面附近的第一掺杂区、复数形成于该漂移层的该表面附近且位于多个该第一掺杂区之间的第二掺杂区及一设置于该漂移层的该表面上的第一金属层。该第一金属层与该第二掺杂区形成一欧姆接触。该漂移层有一第一掺杂浓度,该第一掺杂浓度有一第一导电类型,且每个该第二掺杂区有一第二掺杂浓度,该第二掺杂浓度有该第一导电类型,该第二掺杂浓度高于该第一掺杂浓度。每个该第一掺杂区有一第一深度,每个该第二掺杂区有一小于该第一深度的第二深度。

技术研发人员:许甫任,颜诚廷,洪湘婷

受保护的技术使用者:即思创意股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!