半导体元件及其制备方法与流程

本申请案主张美国第17/897,898号专利申请案的优先权(即优先权日为“2022年8月29日”),其内容以全文引用的方式并入本文中。本公开涉及一种半导体元件及其制备方法,尤其涉及一种具有浅插塞的半导体元件及其制备方法。

背景技术:

1、半导体元件用于各种电子应用,例如个人计算机、手机、数码相机和其他电子设备。为满足对计算能力不断增长的需求,半导体元件的尺寸不断地缩小。然而,在缩减过程中会出现各种各样的问题,而且这些问题还在不断增加。因此,在提高半导体元件的性能、质量、良率、效能和可靠性等方面仍然面临挑战。

2、上文的“先前技术”说明仅是提供背景技术,并未承认上文的“先前技术”说明揭示本公开的标的,不构成本公开的先前技术,且上文的“先前技术”的任何说明均不应作为本案的任一部分。

技术实现思路

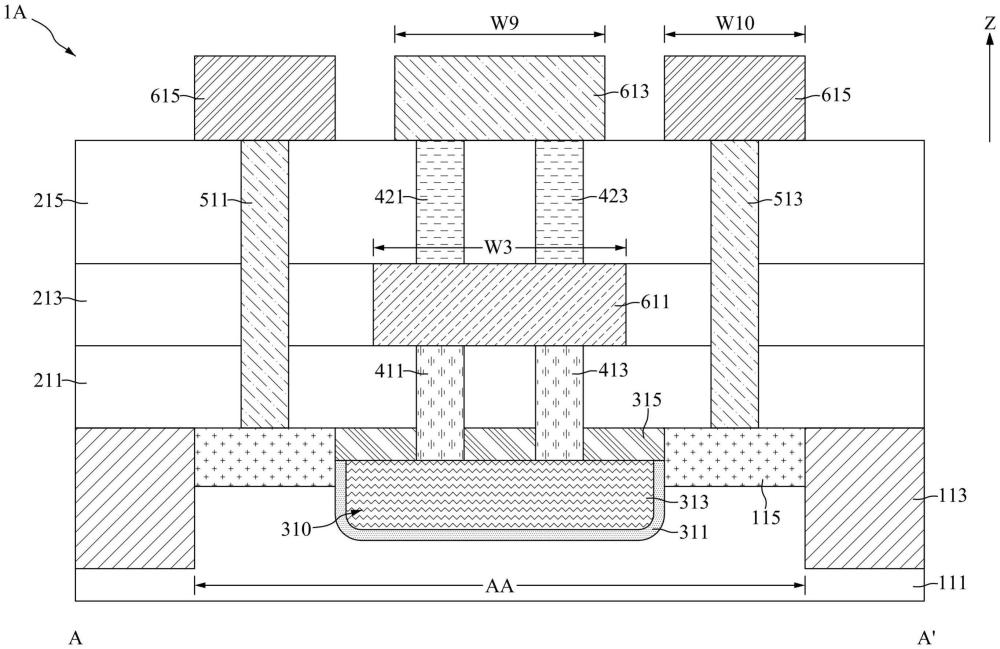

1、本公开的一个方面提供一种半导体元件,其包括:一基底;一字元线结构,设置于该基底中;多个杂质区域,设置于该基底中并邻近该字元线结构;多个底部浅插塞,设置于该字元线结构上;一第一内连接层,设置于该些底部浅插塞上;多个顶部浅插塞,设置于该第一内连接层上;及多个深插塞,设置于该些杂质区域上。该些顶部浅插塞的顶面和该些深插塞的顶面实质上共面。

2、本公开的另一方面提供一种半导体元件,其包括:一基底;多个隔离层,设置于该基底中;一字元线结构,设置于该基底中,且位于该些隔离层之间;多个杂质区域,设置于该基底中并邻近该字元线结构;一第一内连接层,设置于该些底部浅插塞上;多个顶部浅插塞,设置于该第一内连接层上;及多个深插塞,设置于该些杂质区域上。该些顶部浅插塞的顶面和该些深插塞的顶面实质上共面。该字元线结构在俯视视角下沿一第一方向延伸。该些隔离层沿该第一方向延伸且彼此间相互平行。

3、本公开的另一方面提供一种半导体元件的制备方法,其包括:提供一基底;形成一字元线结构在该基底中,并形成多个杂质区域在该基底中且与该字元线结构相邻;形成多个底部浅插塞在该字元线结构上;形成一第一内连接层在该些底部浅插塞上;形成多个顶部浅插塞在该第一内连接层上;及形成多个深插塞在该些杂质区域上。该些顶部浅插塞的顶面和多个深插塞的顶面实质上共面。该些底部浅插塞的宽度小于该些深插塞的宽度。

4、由于本公开的半导体元件的设计,通过在底部浅插塞和顶部浅插塞之间采用第一内连接层,底部浅插塞与顶部浅插塞的纵宽比将得以减小。结果,制造半导体元件的复杂性将得以降低。

5、上文已相当广泛地概述本公开的技术特征及优点,使下文的本公开详细描述得以获得较佳了解。构成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中具有通常知识者应了解,可相当容易地利用下文揭示的概念与特定实施例可作为修改或设计其它结构或制程而实现与本公开相同的目的。本公开所属技术领域中具有通常知识者亦应了解,这类等效建构无法脱离后附的权利要求所界定的本公开的精神和范围。

技术特征:

1.一种半导体元件,包括:

2.如权利要求1所述的半导体元件,其中所述多个底部浅插塞的宽度小于所述多个深插塞的宽度。

3.如权利要求2所述的半导体元件,其中该字元线结构包括:

4.如权利要求3所述的半导体元件,其中该字元线结构的宽度与该第一内连接层的宽度不同。

5.如权利要求3所述的半导体元件,其中该字元线结构的宽度与该第一内连接层的宽度实质上相同。

6.如权利要求4所述的半导体元件,其中所述多个底部浅插塞的宽度与所述多个顶部浅插塞的宽度实质上相同。

7.如权利要求4所述的半导体元件,其中所述多个底部浅插塞的宽度与所述多个顶部浅插塞的宽度不同。

8.如权利要求4所述的半导体元件,其中所述多个底部浅插塞的宽度实质上相同。

9.如权利要求4所述的半导体元件,其中所述多个底部浅插塞的宽度不同。

10.如权利要求4所述的半导体元件,其中所述多个顶部浅插塞的宽度实质上相同。

11.如权利要求4所述的半导体元件,其中所述多个顶部浅插塞的宽度不同。

12.如权利要求4所述的半导体元件,其中所述多个深插塞的宽度不同。

13.如权利要求4所述的半导体元件,其中所述多个深插塞的宽度实质上相同。

14.如权利要求4所述的半导体元件,还包括一底部介电层,设置于该基底上、一中间介电层,设置于该底部介电层上、及一顶部介电层,设置于该中间介电层上;

15.如权利要求14所述的半导体元件,还包括一第二内连接层,设置于所述多个顶部浅插塞上,及多个第三内连接层,设置于所述多个深插塞上;其中,该第一内连接层的宽度和该第二内连接层的宽度不同。

16.一种半导体元件,包括:

17.如权利要求16所述的半导体元件,其中所述多个底部浅插塞的宽度小于所述多个深插塞的宽度,其中该字元线结构包括:

18.如权利要求17所述的半导体元件,其中该字元线结构的宽度与该第一内连接层的宽度不同。

19.如权利要求17所述的半导体元件,还包括一底部介电层,设置于该基底上、一中间介电层,设置于该底部介电层上、一顶部介电层,设置于该中间介电层上、一第二内连接层,设置于顶部浅插塞上、及多个第三内连接层,设置于所述多个深插塞上;

20.一种半导体元件的制备方法,包括:

技术总结

本申请公开一种半导体元件及其制备方法,该半导体元件包括:一基底;一字元线结构,设置于该基底中;多个杂质区域,设置于该基底中并邻近该字元线结构;多个底部浅插塞,设置于该字元线结构上;一第一内连接层,设置于该些底部浅插塞上;多个顶部浅插塞,设置于该第一内连接层上;及多个深插塞,设置于该些杂质区域上。该些顶部浅插塞的顶面和该些深插塞的顶面实质上共面。

技术研发人员:黄则尧

受保护的技术使用者:南亚科技股份有限公司

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!