一种增强型氮化镓基电子器件及其制备方法

本发明涉及半导体器件,具体涉及一种氮化镓基电子器件及其制作方法。

背景技术:

1、gan基金属绝缘体半导体高电子迁移率晶体管(mis/mos-hemt)具有输出功率密度大、高频高压、耐高温、抗辐射等优异特性,在gan基电力电子器件与微波器件等应用领域具备很大应用潜力。增强型是功率电子器件安全工作的关键要求,即在高压工作时,器件即使失去栅控的状态下也是安全的,不会导致系统的烧毁。这就要求功率电子器件必须是增强型的(enhancement-mode,也称normally-off),从安全性角度考虑,器件设计阈值要求更高一些,主要因素包括:器件发热和所处环境温度的提升会导致增强型阈值电压的负向漂移;3)栅极控制电压随机噪音所带来的阈值抖动会导致器件阈值电压的移动。综合考虑器件物理和系统安全设计,实现阈值高于+3v 是gan基电力电子器件的必要条件。

2、目前氮化镓基绝缘栅器件增强型技术主要有三种。(1)f离子注入技术:通过向栅极下的algan势垒层自对准注入带负电的f离子,抬高了势垒层的能带,从而耗尽沟道中的2deg,实现增强型,结合金属-绝缘体-半导体技术,可以将阈值电压提高到3 v以上。但由于f离子注入的深度难以控制,在algan/gan异质结附近的拖尾会造成2deg的输运性能降低,高温下栅极可靠性也存在很大问题。(2)凹槽栅刻蚀技术:利用刻蚀工艺,部分或全部去除栅极区域下的algan势垒层,以削弱其极化效应,降低2deg密度,来达到增强型的目的。但在对algan势垒层减薄的过程中,刻蚀会引起较大的晶格损伤,降低沟道中2deg的迁移率,使导通电阻上升。同时由于缺乏刻蚀停止层,使刻蚀深度的均匀性较难控制,刻蚀损伤带来的界面态问题影响着器件的可靠性,且随着gan-on-si晶圆尺寸的增大,晶圆间刻蚀均匀性和晶圆内重复性也会下降,影响器件的大批量规模生产。(3)超薄势垒技术:利用金属有机化学气相沉积在si衬底上外延生长超薄势垒algan(<6 nm)/gan异质结构,实现沟道中2deg本征耗尽,然后利用高温低压化学气相沉积sinx钝化层在algan表面诱导的高密度正电荷,可有效恢复有源区的2deg,但栅极区域的超薄势垒层残余极化效应在栅介质淀积后将阈值电压限制在1v以内,无法使阈值电压达到增强型高标准要求。

3、如何进一步提升阈值电压至企业级应用,实现栅极沟道无刻蚀损伤且得到高栅极可靠性及片内均匀性及重复性,是下一步有效提高gan基增强型器件的工艺重复性和成品率,推动gan基功率电子器件的产业化进程的重要手段。

技术实现思路

1、有鉴于此,本发明的主要目的是提供一种gan基增强型电子器件及其制备方法,用以实现gan基电子器件阈值电压进一步提升至3v以上,并可避免势垒层刻蚀均匀性及重复性的问题。

2、本发明通过在gan缓冲层生长完成后将栅极区域刻蚀为“v”型槽形成半极性面或非极性面,可以是a面(11-20)、m面(1-100)或(11-22)面,削弱gan极化效应,并结合薄al(in,ga)n势垒层进一步降低残余极化效应,实现栅极区域2deg的本征完全耗尽,且在栅极介质淀积后也达到完全没有或者极低二维电子气浓度,实现阈值电压的有效正向提升;在栅极与源极以及栅极与漏极之间的access区域为薄al(in,ga)n势垒层与全极性面(c面)gan异质结构,通过钝化介质层恢复得到高浓度2deg。

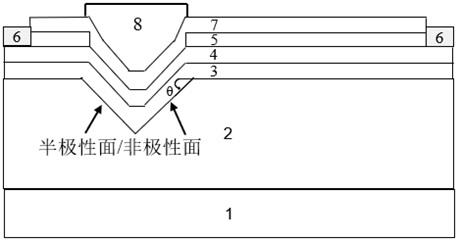

3、具体的,本发明提供的增强型gan基电子器件包括衬底和其上的gan缓冲层,其特征在于,所述gan缓冲层在栅极区域具有刻蚀形成的“v”型槽,得到gan半极性面或非极性面;在gan缓冲层上为依次层叠的薄gan缓冲层再生长层和薄al(in,ga)n势垒层,在栅极区域“v”型槽处al(in,ga)n势垒层上依次是栅介质层和栅极金属,两侧的al(in,ga)n势垒层上制备有欧姆接触层,栅极金属与所述欧姆接触层之间淀积有钝化层。

4、上述增强型gan基电子器件中,所述gan缓冲层的厚度要大于所述“v”型槽的深度。“v”型槽的斜面与水平方向的夹角θ的角度小于90°,形成的非极性面为a面(11-20)或m面(1-100)等,半极性面为(11-22)等方向,“v”型槽顶宽度为100nm~3μm,槽深度为50nm-1μm。

5、所述gan缓冲层再生长层的厚度优选为20~200nm,所述al(in,ga)n势垒层的厚度优选为3~10nm。所述al(in,ga)n势垒层可以是algan或alinn三元合金势垒层,也可以是alingan四元合金势垒层。

6、所述栅介质层可以是sin、sio2、alon、alsio、alsin或者sion,厚度优选为5~30nm。所述栅极金属可以是ni/au、pt/ti/au、al/ni/au或tin等。

7、所述钝化层可以是sin,aln或sio2等单一介质或它们之间叠加组成的复合介质。

8、本发明还提供了上述增强型gan基电子器件的制备方法,包括以下步骤:

9、1)在衬底上生长gan缓冲层;

10、2)在栅极区域刻蚀gan缓冲层形成“v”型槽,得到gan半极性面或非极性面;

11、3)在gan缓冲层上依次生长薄gan缓冲层再生长层和薄al(in,ga)n势垒层,形成al(in,ga)n/gan异质结;

12、4)在有源区淀积钝化层,然后刻蚀两侧的钝化层,在al(in,ga)n势垒层上形成欧姆接触槽,并在欧姆接触槽内淀积金属形成欧姆接触层;

13、5)在栅极区域刻蚀钝化层,形成栅极槽,在栅极槽内al(in,ga)n势垒层上淀积栅介质层;

14、6)进行器件隔离;

15、7)在栅介质层上淀积栅极金属,得到所述增强型gan基电子器件。

16、本发明采用栅极区域gan半极性面或非极性面“v”型槽组合薄势垒层实现高阈值电压的增强型技术,对于gan器件阈值电压的进一步提升起到推进作用,可以实现更高阈值电压的增强型器件,并可避免了algan势垒层刻蚀带来的沟道界面态问题,实现高片内均匀性及重复性,成功为制备高性能增强型器件提供了有效方法。

17、上述步骤2)刻蚀形成“v”型槽时,1 微米以下栅线条可以通过步进光刻或电子束光刻实现,1 微米以上可以采用光学光刻实现。

18、上述步骤4)制备钝化层时,可以采用lpcvd、ald或pecvd方法沉积,如果是具有极化特性的aln钝化薄膜或sinx钝化保护层,厚度在10nm 以下,可以采用等离子体增强模式原子层沉积或分子束外延技术在低温下生长,生长温度在150 ℃到800 ℃之间。

19、上述步骤4)中,欧姆接触层的制备采用剥离(lift-off)工艺和含au温度为700~900℃的合金化工艺或不含au温度为300~600℃的合金化工艺。

20、上述步骤6)中,器件隔离采用台面隔离或注入隔离。

21、上述步骤5)中栅介质层可以采用ald、cvd、mbe技术生长,生长温度为500~1000℃,厚度在5~30nm之间。

22、基于上述技术方案可知,本发明的氮化镓基电子器件及其制作方法相对于现有技术具有以下优势:

23、1、本发明提供的氮化镓基电子器件及其制作方法,基于gan缓冲层(buffer层)将栅极区域刻蚀为“v”型槽形成半极性面或非极性面,再生长薄势垒层使栅极区域的极性降低,实现半极性或无极性的al(in,ga)n/gan异质结,并结合薄势垒层al(in,ga)n进一步削弱栅极区域极化效应,实现栅极区域2deg本征完全耗尽,且在栅极介质淀积后栅极区域也达到极低或者完全没有二维电子气浓度,栅外区域通过钝化恢复得到高2deg,实现了更高阈值电压的增强型gan基电子器件。

24、2、本发明提供的氮化镓基电子器件及其制作方法,gan缓冲层刻蚀后再生长薄gan缓冲层避免了刻蚀后沟道损伤问题,通过后续连续薄gan缓冲层和薄势垒层al(in,ga)n再生长,避免了gan缓冲层刻蚀带来的损伤问题,使得沟道仍然在无刻蚀连续生长的al(in,ga)n/gan异质结界面,有效降低了刻蚀带来的界面态问题,显著提升了器件栅极可靠性。

25、3、本发明提供的氮化镓基电子器件及其制作方法,采用gan缓冲层刻蚀,gan缓冲层及al(in,ga)n势垒层再生长技术,有效避免了栅极区域刻蚀均匀性及重复性的问题,并且能有效提高gan基增强型器件的工艺重复性和成品率,推动gan基功率电子器件的产业化进程。

- 还没有人留言评论。精彩留言会获得点赞!