半导体封装的制作方法

本公开涉及一种半导体封装,且更特定来说,涉及一种能够增强3d ic散热的半导体封装。

背景技术:

1、尽管最近归因于工程及材料科学伟大成就的演进,例如涉及极复杂多步光刻图案化、新应变改良材料及金属氧化物栅极,但常规晶体管的2d几何微缩正快速接近“红砖墙”。3d ic(3d集成电路)的集成通过在单个中介层或衬底上垂直堆叠ic及/或晶体管层以提供极密集的ic呈现出相较于传统2d ic及2d封装集成的重大转变。3d ic已被公认为下一代半导体技术,其具有高性能、低功耗、物理尺寸小及高集成密度的优点。3d ic提供持续满足后代装置的性能/成本需求同时保持更宽松栅极长度及更低工艺复杂性的一途径。

2、针对例如高性能计算(hpc)、数据中心、人工智能(ai)及智能手持设备的高端应用,通常会采用包含特别具有处理器及存储器的多个有源裸晶的先进sip(系统级封装)以在更小的外形规格内提高计算能力。本文中描述的先进sip包含图1a中展示的2.5d ic、图1b中展示的扇出sip、图1c中展示的嵌入式sip、图1d中展示的硅光子及图1e中展示的3dic。

3、在图1a中,2.5d ic结构90包含通过多个焊料连接903支撑硅中介层902的层压衬底901。常用于2.5d ic封装中且含有硅通孔(tsv)904的硅中介层902可用作一平台以桥接层压衬底901与涵盖3d ic(例如高带宽存储器(hbm)动态随机存取存储器(dram)堆叠,即,图1a中的存储器结构905及处理器ic 907)的ic块之间精细的线条及空间(l/s)间距落差。硅中介层902可拥有针对不同应用而具有不同功能的无源及/或有源ic。除存储器装置(例如存储器结构905)及逻辑装置(例如处理器907)之外,包含其它类型的有源ic(例如模拟及混合信号装置)、mems(微电机系统)装置及无源装置的各种其它类型的电子组件均可安装于由晶圆级工艺生产的硅中介层902上。这些电子组件可布置成裸晶并排放置的2d ic形式、含有多个3d存储器结构905与处理器并排安装于中介层(图1a)上的2.5d ic形式,或将处理器安装于中介层上,并在处理器顶部上安装存储器结构905的3d ic封装形式。例如,图1a中的存储器结构905可为hbm dram堆叠,其包含通过现在的铜柱微凸块或随着工艺成熟通过未来的铜混合接合层来垂直堆叠于基底控制裸晶905b之上的多个dram裸晶905a。如图1a中展示,硅中介层902使用微凸块或焊料凸块接合于在层压衬底901的上方,而层压衬底901可通过下面的多个球栅阵列(bga)焊料球906接合到印刷电路板pcb(图中未展示)。

4、在图1b中,可采用扇出封装结构91,其中芯片913a及913b上的电性连接从芯片的有效表面扇出以使外部i/o 903a能够放置到芯片的界限外。扇出封装结构91包含模封于模封化合物中的一或多个半导体芯片(例如芯片913a及芯片913b),并允许个别芯片连接到扇出布线层或重布层(rdl)911并与焊料凸块903a耦合或替代地,与微凸块耦合以连接到衬底901,衬底901可为使用焊料凸块或焊料球906接合到下一层阶衬底(例如pcb)的层压衬底、中介层或扇出封装结构。除图1b中展示的结构之外,还存在各种其它扇出封装结构,包含含有模通孔(through mold via,tmv,见图2)及形成于tmv顶部上的适当表面涂层的结构,表面涂层暴露于顶部模封化合物表面或将图1b中的rdl 911连接到形成于模封化合物顶部上的另一rdl以促进随后将另一电子组件(例如存储器)垂直安装于扇出结构的顶部上。图2中描绘的最高容量商业化扇出封装可在智能手持应用中见到,其中应用处理器(ap)裸晶嵌入模封化合物中且dram封装安装于扇出结构上。

5、在图1c中,嵌入式sip 92包含嵌入层压衬底901中的一或多个装置923。一或多个装置923可为嵌入式硅互连件(其可为无源装置或有源装置)、有源ic装置(例如dc-dc转换器)或嵌入式无源装置(例如电容器或电感器)。此外,其中嵌入有装置923的层压衬底901可根据应用而通过焊料球906或微凸块进一步接合到另一层压衬底或pcb 908。嵌入式sip通常连同先进sip一起实施,先进sip包含含有嵌入模封化合物(图1b)中的裸晶的扇出结构。

6、在图1d中,硅光子结构93包含cmos裸晶916、其内嵌入有调制器919及光电检测器920的波导结构918及将光学信号耦合进出波导结构918的光纤921。激光二极管917及波导结构918以及耦合到波导结构的组件集成于具有tsv的硅中介层914之上。由晶圆级工艺生产的硅中介层914可经配置而通过用于外部连接的多个焊料凸块或微凸块903安装于衬底(例如层压衬底)上。

7、在图1e中,基于3d ic的结构94包含第一裸晶940(呈裸晶形式)及第二裸晶941(也呈裸晶形式)。第一裸晶940可为处理器裸晶,而第二裸晶941可含有dram裸晶或其它类型的存储器装置,例如sram。第二裸晶941可通过各种合适的接合技术(包含覆晶及铜混合接合)堆叠于第一裸晶940上。基于3d ic的结构94允许第一裸晶940(例如处理器裸晶)近距离存取第二裸晶941(例如存储器裸晶),在所有先进sip(见图1a到1e及图2)中处理器与存储器之间具有最短数据传送时间。

8、未来,3d ic应用的数目将稳定增加。预期3d ic将在需要“极端”超高性能、更高功率效率装置的应用(例如高性能计算及数据中心(hpc)、ai(人工智能)/ml(机器学习)、5g/6g网络、图形、智能手机/穿戴式设备、汽车及其它)中找到广泛用途。这些装置包含cpu(中央处理单元)、gpu(图形处理单元)、fpga(现场可编程逻辑门阵列)、asic(专用ic)、tpu(张量处理单元)、集成光子、ap(手机应用处理器)及封包缓冲器/路由器装置。

9、为了加快采用,3d ic系统必须经由涉及硅ip、ic/小芯片及ic封装且解决伴随功率及热挑战的ic封装系统协同设计来全盘构建。与2d封装对每“平方厘米”的性能、功率、面积及成本(performance,power,area,and cost,ppac)优化相比,3d ic的ic封装系统协同设计旨在实现对每“立方毫米”的ppac优化,其中现在在所有权衡决策中必须考虑涵盖ic、中介层、ic封装衬底、ic封装及系统印刷电路板(pcb)的垂直尺寸。

10、商用3d ic(例如3d hbm dram存储器堆叠)越来越多地受到在有源裸晶及硅中介层两者中含有硅通孔(through silicon via,tsv)的商用2.5d ic(例如图1a中展示的2.5dic结构90)支持。通过适当散热解决方案,3d ic最终可使用互连技术(例如tsv、含有互连布线及微通孔的rdl、使用铜柱微凸块或焊料凸块的覆晶接合及由索尼(sony)最先证明用于裸晶间通信的互补金属氧化物半导体(cmos)图像传感器的新兴铜混合接合)实现存储器上叠存储器、逻辑上叠存储器、逻辑上叠逻辑。

11、3d ic允许来自不同制造工艺及节点的异质裸晶垂直堆叠、芯片再利用及sip中小芯片用于已突破最先进节点单个裸晶的限制的高性能应用。3d ic集成可经由3d单片集成及/或不同裸晶(如同hbm dram堆叠的情况)或嵌入不同封装层中的裸晶的垂直集成来进行。

12、3d单片集成通常涉及多个有源硅层与层之间的垂直互连件的垂直集成。单片3dic构建于多个有源硅层及层之间的垂直互连件上。其仍处于早期开发阶段且尚未广泛部署。近来,“中央处理单元(cpu)上叠高速缓存”的3d ic结构已使用铜混合接合呈现及商业化。现今,hbm dram堆叠(其中的每一者是通过将数个dram裸晶垂直集成于控制ic上来创建)代表现今最大量的商用3d ic。3d ic对要求在给定装置占用面积中堆积更多晶体管的应用来说是理想的,例如用于移动应用的单芯片系统soc(例如图2中的ap)及用于已超越最先进节点处的单裸晶限制的其它应用,例如hpc、数据中心及ai。

13、移动装置(例如智能手机)由于仅能使用小面积进行散热、且仅有较小的空间可用于实施散热解决方案,加上移动装置中所产生的热须受到相对较低的最大允许壳体温度所限制,一般在44℃到50℃之间,因此面临特殊热管理挑战。

14、图2展示基于叠层封装(package-on-package,pop)结构96的当前智能移动应用。如图2中展示,dram封装931堆叠于pop结构中的应用处理器(ap)封装932上。dram封装931包含堆叠于层压衬底9312上的dram裸晶9311、模封dram裸晶9311的模制层9313(例如模封化合物)及形成于层压衬底9312上的垂直接合到ap封装932的焊料球9314。ap封装932包含ap裸晶9321、模封ap裸晶9321的模制层9322、形成于模制层9322中且耦合到dram封装931的焊料球9314的多个tmv 9323及形成于ap 9321及模制层9322上的rdl 9324及形成于rdl 9324上的焊料球9325。此外,pop结构96通过焊料球9325安装于pcb 933上,且散热器934安置于具有热界面材料(tim)9381的dram封装931之上。pop结构96及pcb 933安置于显示面板936下的智能移动装置的壳体935内部。为了降低干扰,防护屏937可安置于具有热界面材料(tim)9382的散热器934上且在显示面板936下以便保护pop结构96。此外,间隙填料939可添加于pcb 933与壳体935之间以填充pcb 933与防护屏/壳体之间中的空间。

15、在图2中展示的智能移动装置结构中,由ap裸晶9321产生的热主要通过安装于ap封装932顶部上的模制堆叠裸晶dram bga封装931耗散到散热器934及接着到壳体935。

16、与通过自然对流及辐射(其主要取决于移动装置的表面积)将热从壳体935的表面移除到周围环境相比,从ap裸晶9321的热点到壳体935的表面存在较高热电阻(因为用于模制层9313及9322中的模封化合物实际上是热绝缘体)。為将壳体温度控制到低于其最大允许温度,通常在44℃到50℃之间,此将导致图2中的半导体封装可承受的最大ap功率受到限制。针对其空间宝贵且通常没有空间可装设风扇及鳍式散热片的移动装置,图2中展示的从ap封装到壳体的散热是主要散热方式。

17、在应用及数据流量持续爆炸式增长的驱动下,移动装置的ap功率预期将增加,借此严重挑战图2中展示的pop封装结构的冷却极限。此外,更高数据流量需要更高存储器容量来与更强大、更高功率的ap裸晶通信。为了增加存储器容量同时提高从扇出ap封装到壳体的散热效率,可在垂直或封装厚度方向上将裸晶形式的更多dram裸晶(在dram裸晶底部上根据需要含有控制ic)堆叠于ap封装上或更好地堆叠于裸ap裸晶(在3d ic中)或高热导率中介层(在2.5d ic中)上,而非堆叠模封dram层压封装(如图2中展示),应理解,与裸晶中的硅衬底相比,用于dram封装中的层压衬底及用于dram封装及扇出ap封装两者中的模封化合物是不良热导体。

18、与安装于pcb上的2d dram封装相比,3d dram堆叠(例如,基于移动装置的宽i/odram裸晶或hpc、数据中心及ai应用的hbm dram裸晶)提供更低功率、更高带宽及更高密度优点。在3d dram堆叠中,每单位面积功率可由于更多裸晶堆叠而增大(其中垂直堆叠中的相邻裸晶彼此加热)且在用于移动装置中的空气冷却的情况中,底部及中间层级dram与更靠近散热片(heat spreader)或热导板及散热器(heatsink)的其顶部上的裸晶相比通常具有有限散热路径。这两种因素均可能造成3d装置过热(与2d存储器相比),其中底部层最热而顶部层较冷。dram中的高温可导致性能及效率降低,尤其当动态热管理方案用于当温度变得过高时调节dram带宽。过热还可致使装置停转(即,被禁止存取)以及可靠性问题。所有电子装置在特定温度范围内可靠运转。随着更多dram裸晶垂直堆叠于处理器上,需要新的热解决方案来缓解与较底层dram裸晶及控制ic相关联的过热效应,尤其当其直接堆叠于较高功率处理器(例如ap裸晶或3d ic中的处理器)顶部上时,这将导致上述过热效应更加严重。

19、随着过热效应使用本文中公开的新热管理解决方案来解决,将多个dram裸晶(及控制ic)直接放置于处理器顶部上(无论其是ap裸晶还是hpc、数据中心及ai应用的处理器)不仅有助于增大存储器容量,而且有助于减小计算及存储器带宽间隙。未来,处理器速度的提高率将不断超过dram存储器速度的提高率。微处理器的成长指数基本上大于dram的成长指数,但每一者都呈指数提高。如图3(引用自美国加州大学伯克利分校的riselab)中展示,处理器与存储器之间的互连带宽滞后于处理器性能增益。此导致使处理器性能无法被充分利用的“存储墙”效应。存储器延时及带宽将继续限制系统性能,而存储器带宽将持续落后于例如hpc、数据中心及ai的高端应用的峰值flop速率,如图3中展示。这种不平衡同样也适用于应用处理器,且尽管行业不断需要更高计算性能,这种不平衡已导致每年不断扩大的显著瓶颈。

20、现今,2.5d ic及3d ic(例如移动装置的hbm dram堆叠或类似地,宽i/o dram堆叠)采用单侧封装拓扑,其含有从用于供电及传讯的顶部ic及单侧区域电性互连件的顶侧(例如,从底部ic(例如图1a中的控制裸晶)的底侧)到上方裸晶的单侧冷却,一次一个裸晶。这些封装拓扑例如通过包含覆晶组合件、tsv及rdl的互连技术来创建。在对3d ic供电时,设计者在设计电源供给网络时必须考虑所有堆叠裸晶/封装层,其中顶部上的裸晶从下方裸晶获得其电力且底部裸晶从2.5d中介层(图1a)或层压衬底(图1b及2)获得其电力。单侧互连件及单侧冷却不可扩展,因为3d ic占用面积(例如,见关于3d ic的图1e或关于2.5dic的图1a中的hbm堆叠)不随堆叠中的裸晶数目增加而变化。单侧电性互连件及冷却对3dic设计者提出最佳设计解决方案的ppac优化造成严格的约束。

技术实现思路

1、本公开的一个方面提供一种半导体封装。所述半导体封装包含第一裸晶及第一支撑件。所述第一裸晶具有前侧及背侧。所述第一支撑件安置于所述第一裸晶正下方且热耦合到所述第一裸晶。所述第一支撑件的热导率大于所述第一裸晶的热导率。

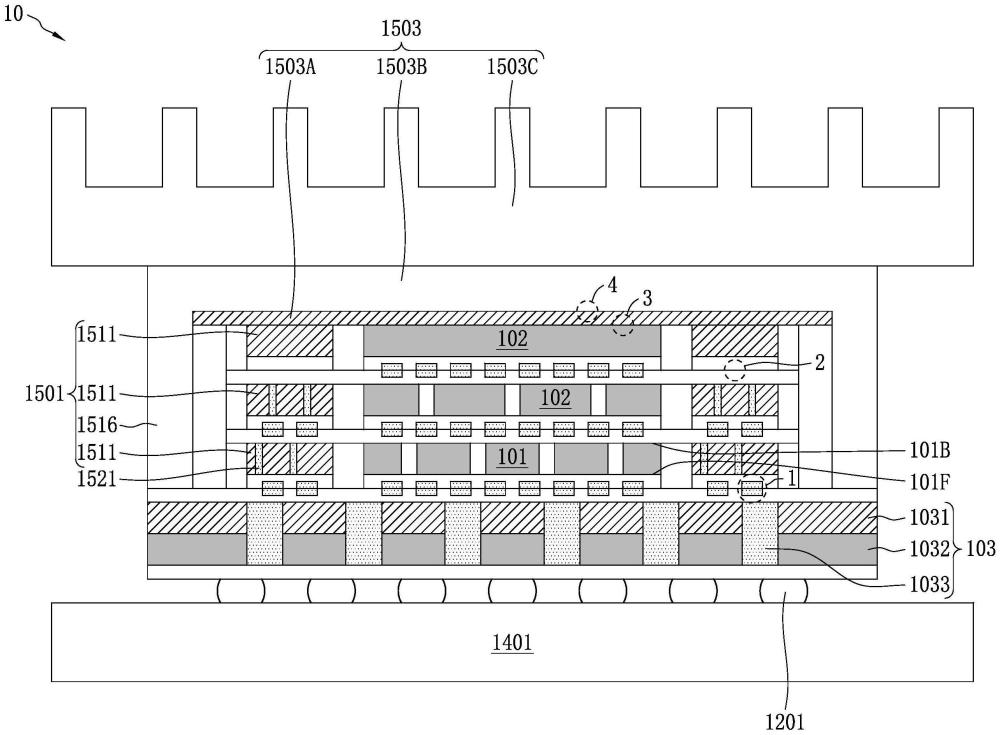

2、本公开的另一方面提供一种允许双侧或多侧供电及传讯以及双侧或多侧冷却的半导体封装。所述半导体封装包含处理器裸晶、多个存储器裸晶及控制裸晶或多个3d存储器堆叠、第一高热导率(htc)结构及多个其它htc结构。所述处理器裸晶具有前侧及背侧。所述第一htc结构安置于所述处理器裸晶正下方且热耦合到所述处理器裸晶。所述第一htc结构的热导率大于所述处理器裸晶的热导率。所述存储器裸晶及所述控制裸晶堆叠于所述处理器裸晶之上。所述多个其它htc结构安置于所述处理器裸晶与控制裸晶之间、安置于邻近垂直堆叠的存储器裸晶之间、与所述裸晶并排放置及/或创建于所述裸晶上作为所述半导体结构中的这些裸晶的集成部分。所述多个其它htc结构的热导率中的每一者大于所述处理器裸晶的热导率。

- 还没有人留言评论。精彩留言会获得点赞!