一种p沟道氮化镓异质结晶体管及其制备方法

本发明涉及gan器件,具体涉及一种势垒插入层p沟道异质结晶体管,属于电力电子器件领域。

背景技术:

1、由于gan材料本身所具有的高击穿场强、高电子饱和速度和异质结高迁移率等特点,基于宽带隙gan半导体材料的微波功率器件有望突破si基器件的限制,成为下一代功率转换系统的候选者。

2、按照载流子的导电类型可以将gan器件分为n型和p型两种类型,n型器件是以电子导电为主,p型器件是以空穴导电为主。由于二维电子气(2deg)密度高、电子迁移率高的优点,gan高电子迁移率晶体管(hemt)适用于高功率和高频应用,并且随着技术的发展,ganhemt器件已经逐渐商业化。基于n沟道的功率开关器件的快速发展刺激了基于p沟道的gan晶体管的发展。实现互补的n沟道和p沟道gan晶体管可以降低功率集成电路的设计复杂度和静态功耗。作为互补金属氧化物半导体(cmos)结构中的关键元件,我们非常期待p沟道gan晶体管在实现增强型的基础上能够具有与n沟道器件相当的电流密度。对于p沟道晶体管增强型的实现,沟槽栅技术已经逐渐成为主流,即将栅极下方的p型gan进行部分刻蚀,使得在零栅压下栅极下方的耗尽区填满沟道,进而实现增强型。然而随着刻蚀深度的增加,栅极下方的导通电阻会大大增加,同时,刻蚀工艺过程中的等离子体又会对被刻蚀部分的p型gan表面造成损伤,进而降低表面载流子的迁移率,另外,由于典型的p型gan中掺入的mg具有高的活化能,使得杂质具有非完全电离的特性,以上这些因素在一定程度上大大降低了p沟道gan晶体管的电流密度。

3、2013年圣母大学的guowang li等人利用gan/aln外延层极化诱导二维空穴气(2dhg)的方法来增加载流子密度和迁移率,并且实现了100ma/mm的电流密度[1]。然而,这一外延层并没有提供n沟道,进而对n型和p型gan晶体管的互补集成产生了影响。

4、香港科技大学的zheyang zheng等人在2020年提出了opt技术,在保留更多栅极下方p型gan的基础上又进行了opt工艺[2],即对表面进行氧处理和高温退火,旨在实现低导通电阻的基础上又具有增强型的操作模式,然而这并未在根本上解决电流密度低的问题,并且增加了工艺的复杂度。

5、2022年麻省理工学院的nadim chowdhury等人通过栅极缩放来降低器件的导通电阻进而增加器件的电流密度,然而随着栅极长度的不断减小,器件的漏致势垒降低效应会变得显著,并且该工作中所制作的器件为耗尽型工作模式[3]。

6、参考文献:

7、[1]g.li et al.,“polarization-induced gan-on-insulator e/d mode p-channel heterostructure fets,”ieee electron device lett.,vol.34,no.7,pp.852–854.

8、[2]z.zheng,w.song,l.zhang,s.yang,j.wei,and k.j.chen,“high ion and ion/ioff ratio enhancement-mode buried p-channel gan mosfets on p-gan gate powerhemt platform,”

9、ieee electron device lett.,vol.41,no.1,pp.26–29.

10、[3]n.chowdhury,q.xie,and t.palacios,“tungsten-gated gan/algan p-fetwith i max>120ma/mm on gan-on-si,”ieee electron device lett.,vol.43,no.4,pp.545–548.

技术实现思路

1、本发明的目的是提出一种新型p沟道gan器件结构,用以解决器件导通电流小、导通电阻大的问题。本发明提出的器件结构在实现增强型的同时,通过在顶部的p型gan中插入一层势垒层来将其下方p型gan中的空穴转到其上方的p型gan中,且由于很强的极化效应,下方p型gan中的空穴完全电离到该势垒插入层上方,增加了载流子密度,进而实现了电流密度的增加。

2、具体的,本发明的技术方案如下:

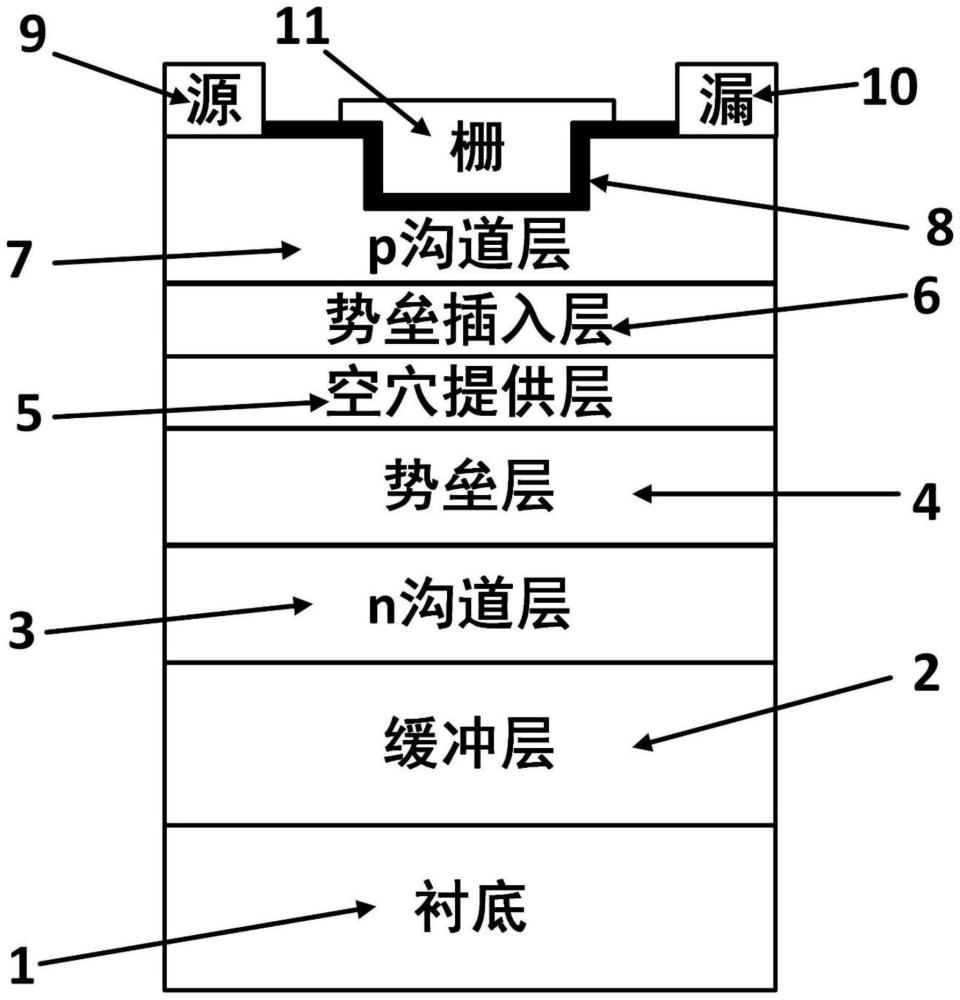

3、一种p沟道gan异质结晶体管,包括衬底及衬底上依次层叠的缓冲层、n沟道层、势垒层、空穴提供层、势垒插入层和p沟道层,栅极、源极和漏极位于p沟道层上,其中所述势垒插入层的禁带宽度相对于空穴提供层和p沟道层的禁带宽度大。

4、进一步的,上述p沟道gan异质结晶体管可以采用mis栅结构或者肖特基型栅结构。在mis栅结构中,栅极与p沟道层之间为栅介质层。

5、上述p沟道gan异质结晶体管中,所述衬底可以是si衬底、蓝宝石衬底、gan衬底等。

6、所述n沟道层可以是gan层、ingan层等可以与势垒层产生极化效应的外延层,其相对于势垒层禁带宽度较小;所述势垒层可以是algan、aln、alingan等可以与n沟道层产生极化效应的外延层,其相对于n沟道层禁带宽度较大。

7、所述空穴提供层可以是掺mg或c的p型gan层、ingan层等可以提供空穴的外延层,其相对于势垒插入层禁带宽度小;所述势垒插入层可以是algan、aln、alingan等材料的势垒层,其相对于空穴提供层禁带宽度大;所述p沟道层可以是掺mg或c的p型gan层、ingan层等可以提供空穴的外延层,其相对于势垒插入层禁带宽度小。所述空穴提供层/势垒插入层/p沟道层具有多种相互组合方式,例如p-gan/aln/p-gan、p-gan/algan/p-ingan、p-ingan/aln/p-gan等多种外延层的相互组合。

8、上述栅介质层可以为al2o3、sio2、hfo2等介质层。

9、本发明还提供了上述p沟道gan异质结晶体管的制备方法,包括以下步骤:

10、1)在衬底上依次外延生长缓冲层、n沟道层、势垒层、空穴提供层、势垒插入层和p沟道层;

11、2)利用光刻工艺在p沟道层上刻蚀出栅极凹陷区域;

12、3)外延生长栅介质层然后制备源漏极,或者直接在p沟道层上制备源漏极;

13、4)在栅介质层上制备栅极,或者直接在p沟道层上制备栅极。

14、总之,本发明的关键点在于势垒插入层的禁带宽度相对于空穴提供层和p沟道层的禁带宽度较大,这样势垒插入层将会把空穴提供层的能带压下来进而使得该层内空穴完全电离,顶部p沟道层充当p型导电沟道的作用。这里并不将顶部p沟道层限制为某单一外延层材料,也可以为不同掺杂、组分等的其他导电材料的相互组合。此外,各区域的长度、厚度、掺杂浓度以及电极种类等参数的变化都是本发明所涉及的范畴,这取决于不同的设计需求和制备工艺。值得注意的是,本发明的重点在于势垒插入层的插入,使得势垒插入层上界面的空穴浓度增加,并通过控制栅极区域的刻蚀深度或通过其他栅极处理方法使得器件达到增强型的工作模式,当然,本发明所提出的通过势垒插入层以提高导电能力同样适用于耗尽型工作模式器件(一般耗尽型器件相对于增强型器件栅极下方刻蚀深度较浅)。可以理解,在不脱离本发明的范围,可以有其他结构和其他变化的实例。再者,不同的实例、结构和工艺可以相互组合来实现相同的目的。

15、本发明的有益效果:

16、现有技术已经可以通过控制刻蚀深度或者栅极后处理工艺来达到增强型的工作模式,但沟道区域载流子迁移率低,导通电阻大等问题还没有有效解决。为此,本发明提出了这样一种结构,通过势垒插入层的插入使得下方空穴提供层中的空穴全部电离,并借助极化效应将底层中完全电离的空穴转移到势垒插入层上界面,因为刻蚀会对gan表面造成损伤导致表面载流子迁移率较低,而势垒插入层插入后的沟道位于底部,这恰恰避免了沟道载流子迁移率低的问题。基于以上原因,本发明所制备的器件电流密度要高于其他器件。总之,本发明既可以通过控制刻蚀深度来实现增强型,又可以通过势垒插入层极化诱导底层空穴完全电离实现相对高的电流密度。

- 还没有人留言评论。精彩留言会获得点赞!