一种集电结浮空P柱结构的IGBT器件的制作方法

本发明属于功率半导体器件的,具体涉及一种集电结浮空p柱结构的igbt器件。

背景技术:

1、近四十年来,随着电子工业对半导体器件的功率性能要求不断提高,半导体中新材料的应用和制造工艺的进步,功率器件领域也得到了迅速的发展,绝缘栅双极型晶体管(insulated gate bipolar transistor,igbt)是当前功率半导体器件主流的发展方向之一,综合了bjt的高导通电流密度和低导通电阻特性,以及功率mosfet电压控制和高输入阻抗的特性,igbt具有驱动功率小、导通电阻低和电流密度大的特点,特别适合应用于消费电子、光伏储能、智能电网和新能源汽车逆变器等领域,未来市场广阔。

2、当前功率器件主要关注的是igbt的关断损耗和导通压降的折中问题,主要为两个发展方向,一为垂直方向的晶圆减薄技术,二为表面结构设计。在晶圆减薄方向上,igbt经历了非穿通型npt-igbt,穿通型pt-igbt,场阻止型fs-igbt,大幅减小了igbt的晶圆厚度,改善了igbt的拖尾电流现象,现在1200v级别的igbt产品厚度可以控制在115um。在igbt的表面结构上,主要的方式是提高发射极处的载流子浓度,以提高igbt的注入增强效应。对于背面结构,由于在集电极处阻断状态下电场强度低,而传统的fs结构的导通下载流子浓度分布是集电极处高,是必在提高集电极注入效率降低导通压降的同时,会造成关断损耗的显著升高,关断时间显著增加。对于传统的fs结构目前普遍优化的是载流子浓度的分布来符合阻断电场的分布;而通过优化电场的分布来符合传统fs结构的载流子分布的相关研究较少。

技术实现思路

1、本发明的目的是通过设计新的背面结构,优化igbt关断损耗和导通压降之间的折中,提高器件的性能,提出一种新型的改变漂移区电场分布而达到快速关断的器件。

2、本发明通过在传统fs-igbt的背面利用集电极隔离槽将集电极隔离成不同区域,其中部分集电极金属被氧化物隔离槽隔离形成无源区,集电极隔离槽中间为集电结浮空p柱,集电结浮空p柱具有特定的的深度与掺杂浓度,用来使器件获得特殊结构的电场,实现快速关断。

3、为实现上述发明目的,本发明技术方案如下:

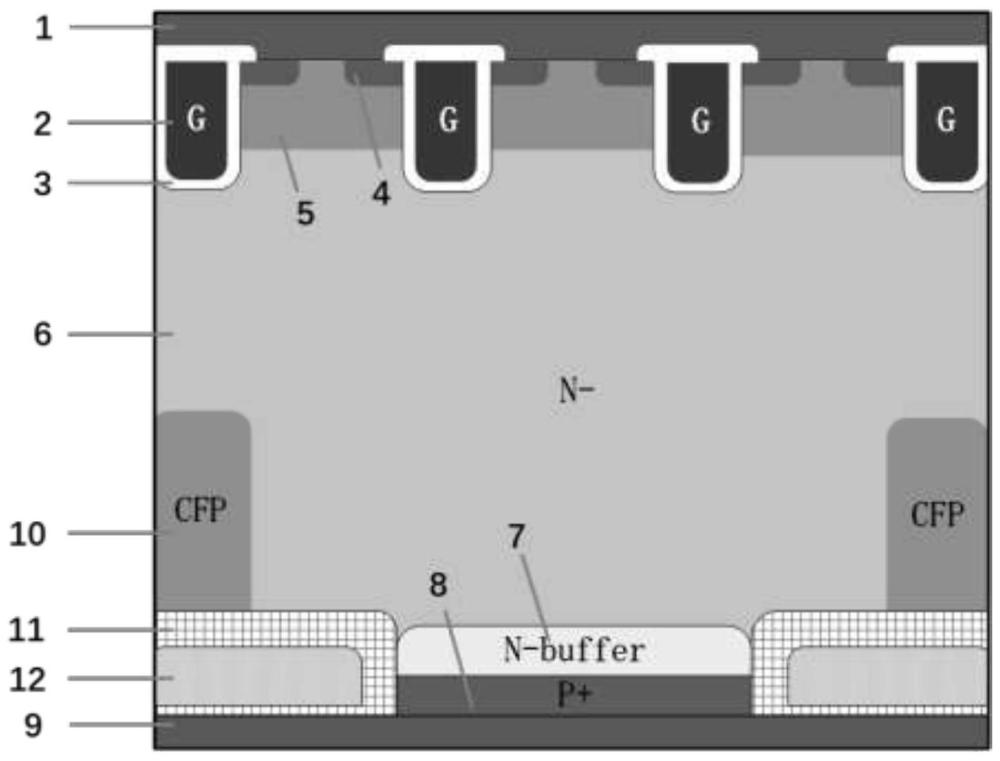

4、一种集电结浮空p柱结构的igbt器件,其元胞结构包括发射极金属1、发射极金属1下方的沟槽栅结构、发射极金属1下方的n+发射区4、n+发射区4下方的p基区5、p基区5下方的n-漂移区6;n-漂移区6下方依次为n型缓冲层7、集电极p+区8、集电极金属9;

5、沟槽栅结构包括沟槽栅电极2、沟槽栅电极2外围的沟槽栅介质层3,沟槽栅结构穿过n+发射区4、p基区5深入到n-漂移区6内,

6、n型缓冲层7与集电极p+区8两侧被集电极隔离槽结构包围,集电极隔离槽结构位于n-漂移区6下方、集电极金属9上方,集电极隔离槽结构包括内部填充物12、包围内部填充物12的外围介质层11;集电结浮空p柱10位于n-漂移区6与集电极隔离槽结构之间,并深入到n-漂移区6内。

7、作为优选方式,其背面工艺制作包括如下步骤:

8、(1)n-漂移区6的背面氧化;

9、(2)背面光刻形成的集电结浮空p柱10的窗口;

10、(3)刻蚀集电结浮空p柱10的20um深的沟槽;

11、(4)外延生长集电结浮空p柱10;

12、(5)集电结浮空p柱10杂质的退火激活;

13、(6)背面光刻形成集电极隔离槽的刻蚀窗口;

14、(7)集电极隔离槽的刻蚀,深度5um;

15、(8)集电极隔离槽在干氧条件生长0.1um二氧化硅;

16、(9)在湿氧条件生长0.9um二氧化硅,形成外围介质层11;

17、(10)集电极隔离槽中淀积3um厚的内部填充物12;

18、(11)背面cvd法淀积1um厚二氧化硅;

19、(12)cmp工艺研磨至硅表面,集电结浮空p柱10结构制作完成;

20、(13)n型缓冲层7的杂质离子注入,激光退火激活;

21、(14)集电极p+区8的杂质离子注入,激光退火激活;

22、(15)溅射集电极金属9完成合金化。

23、作为优选方式,集电结浮空p柱10的背面被集电极隔离槽隔离处于浮空状态;n型缓冲层7与集电极p+区8的两侧被集电极隔离槽所保护;所述的集电结浮空p柱10自上至下的深度大于n型缓冲层7的自上至下的深度,且集电结浮空p柱10和n型缓冲层7在左右方向上没有接触。

24、作为优选方式,在器件由开通转为关闭状态时,n-漂移区6中的耗尽区扩展到集电结浮空p柱10。

25、作为优选方式,在器件正向阻断时,n型缓冲层7与n-漂移区6交界处出现由浮空p柱掺杂浓度和深度决定的电场峰。

26、作为优选方式,集电极隔离槽的外围介质层11是二氧化硅、氮化硅、或者氧化铪介质材料;

27、并且/或者集电极隔离槽的内部填充物12是氮化硅,或者二氧化硅、多晶硅。

28、作为优选方式,集电结浮空p柱10的掺杂方式为均匀掺杂或者非均匀掺杂,掺杂离子为p型杂质,掺杂浓度的范围为2e14到2e16,掺杂深度大于漂移区厚度的10%。

29、作为优选方式,背面与正面结构没有存在对齐的关系,集电结浮空p柱的位置正上方是p基区5,或者是沟槽栅电极2。

30、作为优选方式,所述沟槽栅电极2使用的多晶硅电极材料,重掺杂n型杂质,浓度为1e19;并且/或者沟槽栅介质层3使用二氧化硅、氮化硅、或二氧化铪。

31、作为优选方式,器件半导体材料采用si、sic、gaas或者gan,且各部分采用相同的材料或采用不同材料组合。

32、进一步的是,一种集电结浮空p柱结构的igbt器件,集电极隔离槽与集电极p+区9的宽度占比不固定;浮空p区7到集电极p+区9和n型缓冲层8两侧的间距存在最优值;

33、本发明一种集电结浮空p柱结构需要满足以下条件:

34、1、集电结浮空p柱10的掺杂浓度要介于n-漂移区6与n型缓冲层7之间;

35、2、集电结浮空p柱10的掺杂深度远大于集电极隔离槽的深度;

36、3、n型缓冲层7的掺杂深度不超过集电极隔离槽的深度;

37、4、集电结浮空p柱10为刻蚀沟槽后外延填充p型半导体形成;可以为刻蚀沟槽后离子注入形成;或者直接高能离子注入形成。

38、5、集电结浮空p柱10与n型缓冲层7之间有合适宽度的集电极隔离槽;

39、6、集电极隔离槽的作用是屏蔽或转移电场的分布,改善pn结拐角处的电场集中。

40、本发明的一种集电结浮空p柱结构的igbt器件的有益效果在于:

41、(1)突破了传统fs结构的漂移区电场分布,提出悬链式电场分布,利用尾部形成的pn结与集电极栅的辅助,形成高电场水平错位拉高了导通路径的末端的电场,提高了传统igbt器件的击穿电压;

42、(2)由于集电极隔离槽屏蔽了部分集电极,集电极处具有阳极注入增强效应,器件的导通压降降低;

43、(3)集电结浮空p柱10与n型缓冲层7形成水平错位的pn结,提高了集电极处的电场强度,加快器件的尾部载流子抽取,大幅降低器件的关断时间;

44、(4)工艺上本结构由于集电结浮空p柱10不必与n-漂移区6形成超结sj结构,背面工艺上制作更容易实现,与现有的沟槽工艺是兼容的。

- 还没有人留言评论。精彩留言会获得点赞!