小线宽高频GaN器件及其制备方法

本发明属于半导体制造,涉及一种小线宽高频gan器件及其制备方法。

背景技术:

1、作为第三代半导体材料的代表,氮化镓(gan)具有如高临界击穿电场、高电子迁移率、高二维电子气浓度和良好的高温工作能力等许多优良的特性。因此,基于gan的第三代半导体器件,如高电子迁移率晶体管(hemt)、异质结场效应晶体管(hfet)等已经得到了应用,尤其在射频、微波等需要大功率和高频率的领域具有明显优势。

2、为提高器件射频性能,需要制备小线宽的栅极,且随着器件频率要求越来越高,栅极尺寸要求越来越小,如栅极长度lg<0.15μm。在制备栅极的过程中,由于传统光刻所能实现的线宽尺寸的极限值在0.35μm左右,从而要制备更小尺寸的栅极器件,通常需要采用电子束光刻的工艺。但在采用电子束光刻时,存在电子束曝光时间长的劣势,从而在大规模生产需求下,很难满足量产需求。

3、因此,提供一种小线宽高频gan器件及其制备方法,实属必要。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种小线宽高频gan器件及其制备方法,用于解决现有技术中难以量产小线宽高频gan器件的问题。

2、为实现上述目的及其他相关目的,本发明提供一种小线宽高频gan器件的制备方法,包括以下步骤:

3、提供gan外延结构,所述gan外延结构包括gan沟道层及势垒层;

4、于所述势垒层上形成自下而上由sixn层叠置构成的sixn叠层,所述sixn叠层的折射率为n,其中,x的取值为0.75<x<1.5,n的取值为1.9<n<2.2,且位于下方的所述sixn层的x值及n值均大于位于上方的所述sixn层的x值与n值,以及位于下方的所述sixn层的介电常数大于位于上方的所述sixn层的介电常数;

5、图形化所述sixn叠层,于所述sixn叠层中形成显露所述势垒层的栅极窗口,且所述栅极窗口的开口宽度大于所述栅极窗口的底部宽度;

6、于所述栅极窗口的侧壁形成介电侧墙,所述介电侧墙显露所述势垒层,且所述介电侧墙的介电常数小于位于顶部的所述sixn层的介电常数;

7、于所述栅极窗口中形成t型栅极,且所述t型栅极的栅脚与所述介电侧墙接触。

8、可选地,所述sixn叠层包括自下而上堆置的第一sixn层、第二sixn层及第三sixn层,且所述第一sixn层的开口角度为85-90°,所述第二sixn层的开口角度为75-85°,所述第三sixn层的开口角度为45-75°。

9、可选地,所述介电侧墙包括sio2层及sion层中的一种或组合。

10、可选地,还包括在所述势垒层的表面形成介电钝化保护层的步骤,且所述介电钝化保护层的介电常数大于位于底部的所述sixn层的介电常数;所述介电钝化保护层包括aln层及al2o3层中的一种或组合。

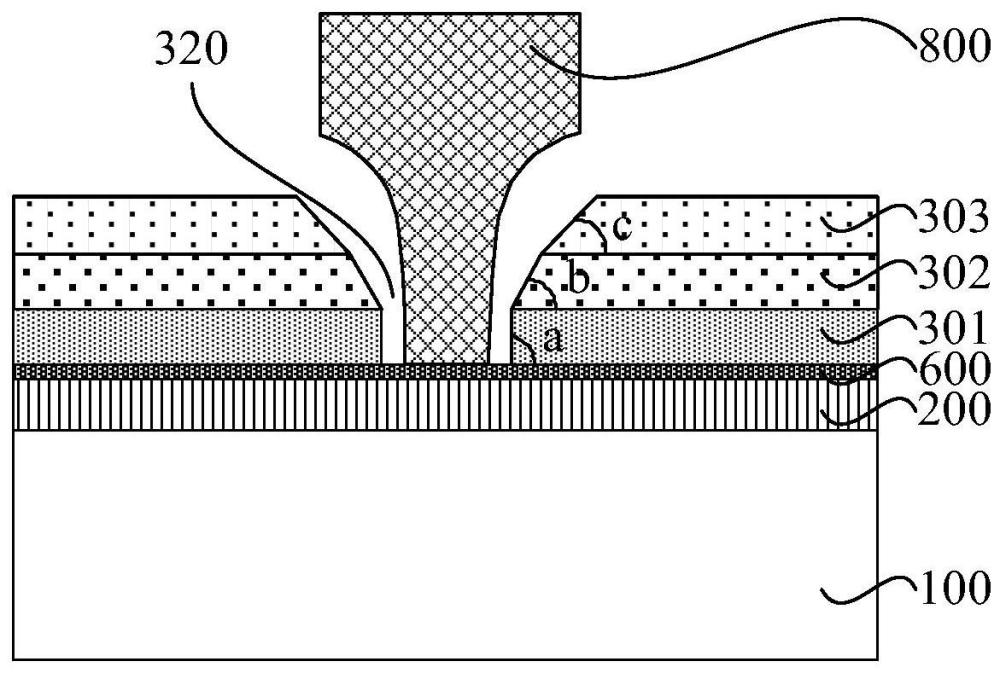

11、本发明还提供一种小线宽高频gan器件,所述gan器件包括:

12、gan外延结构,所述gan外延结构包括gan沟道层及势垒层;

13、自下而上由sixn层叠置构成的sixn叠层,所述sixn叠层位于所述势垒层上,所述sixn叠层的折射率为n,其中,x的取值为0.75<x<1.5,n的取值为1.9<n<2.2,且位于下方的所述sixn层的x值及n值均大于位于上方的所述sixn层的x值与n值,以及位于下方的所述sixn层的介电常数大于位于上方的所述sixn层的介电常数;

14、栅极窗口,所述栅极窗口贯穿所述sixn叠层显露所述势垒层,且所述栅极窗口的开口宽度大于所述栅极窗口的底部宽度;

15、介电侧墙,所述介电侧墙位于所述栅极窗口的侧壁,所述介电侧墙显露所述势垒层,且所述介电侧墙的介电常数小于位于顶部的所述sixn层的介电常数;

16、t型栅极,所述t型栅极位于所述栅极窗口中,且所述t型栅极的栅脚与所述介电侧墙接触。

17、可选地,所述sixn叠层包括自下而上堆置的第一sixn层、第二sixn层及第三sixn层,且所述第一sixn层的开口角度为85-90°,所述第二sixn层的开口角度为75-85°,所述第三sixn层的开口角度为45-75°。

18、可选地,所述介电侧墙包括sio2层及sion层中的一种或组合。

19、可选地,还包括位于所述势垒层的表面的介电钝化保护层,且所述介电钝化保护层的介电常数大于位于底部的所述sixn层的介电常数;所述介电钝化保护层包括aln层及al2o3层中的一种或组合。

20、本发明还提供一种小线宽高频gan器件的制备方法,包括以下步骤:

21、提供gan外延结构,所述gan外延结构包括gan沟道层及势垒层;

22、于所述势垒层上形成自下而上由sixn层叠置构成的sixn叠层,所述sixn叠层的折射率为n,其中,x的取值为0.75<x<1.5,n的取值为1.9<n<2.2,且位于下方的所述sixn层的x值及n值均大于位于上方的所述sixn层的x值与n值,以及位于下方的所述sixn层的介电常数大于位于上方的所述sixn层的介电常数;

23、图形化所述sixn叠层,于所述sixn叠层中形成显露所述势垒层的栅极窗口,且所述栅极窗口的开口宽度大于所述栅极窗口的底部宽度;

24、于所述sixn叠层上形成图形化的光刻胶,所述光刻胶显露所述栅极窗口;

25、进行加热回流及固化,使所述光刻胶回流进所述栅极窗口中形成覆盖所述栅极窗口的侧壁的光刻胶填充层,且所述光刻胶填充层显露所述势垒层;

26、于所述栅极窗口中形成t型栅极,且所述t型栅极的栅脚与所述光刻胶填充层接触;

27、去除所述光刻胶填充层,且所述t型栅极的栅脚与所述sixn叠层具有间距。

28、可选地,所述光刻胶包括pmma层;加热回流的温度包括150-200℃。

29、可选地,所述sixn叠层包括自下而上堆叠设置的第一sixn层、第二sixn层及第三sixn层,且所述第一sixn层的开口角度为85-90°,所述第二sixn层的开口角度为75-85°,所述第三sixn层的开口角度为45-75°。

30、可选地,还包括在所述势垒层的表面形成介电钝化保护层的步骤,且所述介电钝化保护层的介电常数大于位于底部的所述sixn层的介电常数;所述介电钝化保护层包括aln层及al2o3层中的一种或组合。

31、本发明还提供一种小线宽高频gan器件,所述gan器件包括:

32、gan外延结构,所述gan外延结构包括gan沟道层及势垒层;

33、自下而上由sixn层叠置构成的sixn叠层,所述sixn叠层位于所述势垒层上,所述sixn叠层的折射率为n,其中,x的取值为0.75<x<1.5,n的取值为1.9<n<2.2,且位于下方的所述sixn层的x值及n值均大于位于上方的所述sixn层的x值与n值,以及位于下方的所述sixn层的介电常数大于位于上方的所述sixn层的介电常数;

34、栅极窗口,所述栅极窗口贯穿所述sixn叠层显露所述势垒层,且所述栅极窗口的开口宽度大于所述栅极窗口的底部宽度;

35、t型栅极,所述t型栅极位于所述栅极窗口中,且所述t型栅极的栅脚与所述sixn叠层具有间距。

36、可选地,所述sixn叠层包括自下而上堆置的第一sixn层、第二sixn层及第三sixn层,且所述第一sixn层的开口角度为85-90°,所述第二sixn层的开口角度为75-85°,所述第三sixn层的开口角度为45-75°。

37、可选地,还包括位于所述势垒层的表面的介电钝化保护层,且所述介电钝化保护层的介电常数大于位于底部的所述sixn层的介电常数;所述介电钝化保护层包括aln层及al2o3层中的一种或组合。

38、如上所述,本发明的小线宽高频gan器件及其制备方法,通过在势垒层上形成具有不同组分的sixn叠层,在采用传统的光刻方法时,即可形成开口宽度大于底部宽度的类倒梯形的栅极窗口,以缩减栅极尺寸,突破设备线宽限制,实现小线宽的gan器件的制备;进一步的,通过在栅极窗口中形成低k的介电侧墙,可精确控制栅脚尺寸,且可提高gan器件的耐压性;进一步的,通过在势垒层上形成高k的介电钝化保护层,可确保工艺制备过程中不引入额外的工艺损伤,有效钝化缺陷,提高gan器件性能,且介电钝化保护层的散热性能突出,能提高gan器件的散热水平;进一步的,通过在栅极窗口中形成光刻胶填充层,可制备t型栅极,以减小gan器件的寄生参数,进一步提升gan器件的频率。

39、本发明工艺简单、成本低、可重复性强,适用于制备小线宽高频gan器件。

- 还没有人留言评论。精彩留言会获得点赞!