一种降低晶边保护环附近深沟槽侧壁缺陷的方法与流程

本发明涉及半导体制造领域,且具体涉及一种降低晶边保护环附近深沟槽侧壁缺陷的方法。

背景技术:

1、光刻工艺是集成电路制造工艺中的关键步骤,通过曝光和显影等工艺可将掩膜板的图案转移至光刻胶,进一步利用蚀刻工艺将图案转移至半导体衬底或其上部的材料中,其步骤由旋涂、软烘、曝光、显影、硬烘、蚀刻、去胶等工序构成。其中,在旋涂工序中,大部分光刻胶在离心力作用下被甩离晶圆,受晶边处气流速度大的影响,晶边附近光刻胶固化速度快,出现光刻胶堆积和涂布不均匀等问题,如图1所示,易在后续工艺中发生剥离,而且少量光刻胶会由边缘流至晶背,易造成机台污染。因此,在旋涂工艺后,通常执行晶边光刻胶的去除,以形成晶边无光阻且边缘光阻呈斜坡状的形貌,去胶方法例如是基于化学方法的晶边清洗工艺(edge bead removal,ebr)和基于光学方法的晶圆边缘曝光工艺(waferedge exposure,wee)。

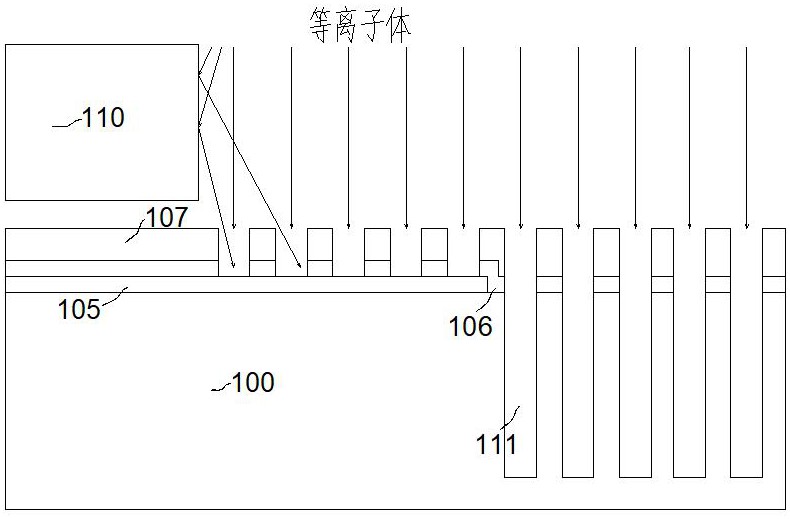

2、然而,在蚀刻工艺中,特别是在深沟槽蚀刻或硅通孔蚀刻工艺中,受晶边无光阻和边缘光阻较薄的影响,晶边会出现硅针缺陷,如图2所示。所述硅针缺陷不仅是颗粒污染源,而且会增大裂片风险。目前,通常采用可升降的晶边保护环,如图3所示,通过对晶圆边缘进行非接触式覆盖,可以避免等离子体对晶边的蚀刻,进而消除硅针缺陷。

3、但是,晶边处的蚀等离子体会在晶边保护环的侧壁产生散射,进而在深沟槽顶部的侧壁区域出现过度蚀刻的现象。所述过度蚀刻发生于晶边保护环内侧2至3mm区域,并由外至内呈现先增强后减弱的趋势。对于毗邻的沟槽结构,过度蚀刻易造成侧壁穿孔缺陷,在沟槽填充之后的热工艺中,诸如炉管、热退火等,所述穿孔缺陷上方的侧壁易发生剥落,造成颗粒污染,严重时会带来裂片风险。

技术实现思路

1、为解决上述问题,本发明提供了一种降低晶边保护环附近深沟槽侧壁缺陷的方法,可以降低等离子体散射而产生的深沟槽侧壁穿孔缺陷。

2、本发明的技术方案:

3、一种降低晶边保护环附近深沟槽侧壁缺陷的方法,所述方法:保留晶边保护环,在晶边保护环内侧区域增加额外一层硬掩膜层,来阻挡深沟槽蚀刻,具体如下:

4、提供半导体衬底;形成第一介质层和第一光阻层;边缘曝光第一光阻层;蚀刻第一介质层;

5、形成第一硬掩膜层;化学机械抛光所述第一硬掩膜层,并停止在所述第一介质层;湿法蚀刻去除第一介质层;形成第二硬掩膜层和第二光阻层;边缘曝光和图案化第二光阻层;执行第一蚀刻以图案化第二硬掩膜层;执行第二蚀刻以图案化半导体衬底。

6、所述半导体衬底为硅衬底。

7、所述第一介质层为氮化硅。

8、所述第一硬掩膜层为氧化硅。

9、所述第二硬掩膜层为氮化硅。

10、所述第一光阻层的边缘曝光宽度w1大于晶边保护环宽度w,且w1-w介于2至3mm。

11、晶边保护宽度w大于所述第一光阻层的边缘曝光宽度w2。

12、本发明的优点是,设计合理,构思巧妙,保留晶边保护环,在晶边保护环内侧区域增加额外一层硬掩膜层,来阻挡深沟槽蚀刻,可以有效降低等离子体散射而产生的深沟槽侧壁穿孔缺陷,减少了颗粒污染源,降低了裂片风险,保证了晶圆质量。

技术特征:

1.一种降低晶边保护环附近深沟槽侧壁缺陷的方法,其特征在于,所述方法:保留晶边保护环,在晶边保护环内侧区域增加额外一层硬掩膜层,具体如下:

2.根据权利要求1所述的降低晶边保护环附近深沟槽侧壁缺陷的方法,其特征在于,所述半导体衬底为硅衬底。

3.根据权利要求1所述的降低晶边保护环附近深沟槽侧壁缺陷的方法,其特征在于,所述第一介质层为氮化硅。

4.根据权利要求1所述的降低晶边保护环附近深沟槽侧壁缺陷的方法,其特征在于,所述第一硬掩膜层为氧化硅。

5.根据权利要求1所述的降低晶边保护环附近深沟槽侧壁缺陷的方法,其特征在于,所述第二硬掩膜层为氮化硅。

6.根据权利要求1所述的降低晶边保护环附近深沟槽侧壁缺陷的方法,其特征在于,所述第一光阻层的边缘曝光宽度w1大于晶边保护环宽度w,且w1-w介于2至3mm。

7.根据权利要求1所述的降低晶边保护环附近深沟槽侧壁缺陷的方法,其特征在于,晶边保护宽度w大于所述第一光阻层的边缘曝光宽度w2。

技术总结

本发明涉及一种降低晶边保护环附近深沟槽侧壁缺陷的方法,所述方法:保留晶边保护环,在晶边保护环内侧区域增加额外一层硬掩膜层,具体如下,提供半导体衬底;形成第一介质层和第一光阻层;边缘曝光第一光阻层;蚀刻第一介质层;形成第一硬掩膜层;化学机械抛光所述第一硬掩膜层,并停止在所述第一介质层;湿法蚀刻去除第一介质层;形成第二硬掩膜层和第二光阻层;边缘曝光和图案化第二光阻层;执行第一蚀刻以图案化第二硬掩膜层;执行第二蚀刻以图案化半导体衬底。可以降低等离子体散射而产生的深沟槽侧壁穿孔缺陷。

技术研发人员:聂祥龙,宋一诺,曹红霞

受保护的技术使用者:上海兆方半导体有限公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!