封装载板及其制作方法、半导体器件及半导体组件与流程

本技术涉及半导体,特别是涉及一种封装载板及其制作方法、半导体器件及半导体组件。

背景技术:

1、相较于硅基板,玻璃基板具有损耗低、机械稳定性强、成本低、可实现大尺寸超薄设计等特性,因此受到广泛的关注,具有广阔的应用前景,被应用在光通信、射频模块、光电系统集成、mems封装、消费电子、电子气体放大器、医疗器械等领域。

技术实现思路

1、基于此,本技术提供一种封装载板及其制作方法、半导体器件及半导体组件,以降低封装载板的制作难度和成本。

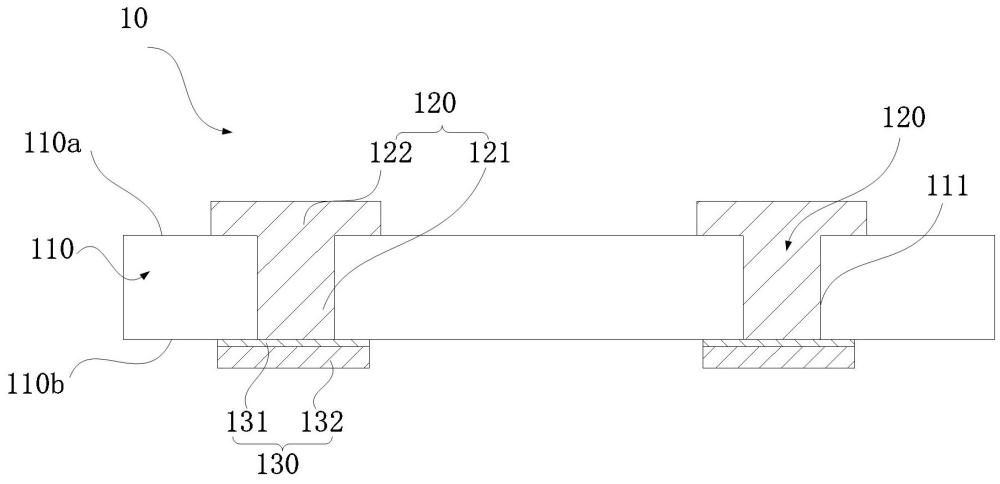

2、根据本技术的一个方面,提供一种封装载板,包括基板和一体式导电结构,所述基板上设置有沿所述基板的厚度方向贯通的通孔;所述一体式导电结构的至少部分填充于所述通孔。

3、根据本技术实施例的封装载板,包括基板和一体式导电结构,基板上设置有沿基板的厚度方向贯通的通孔;一体式导电结构的至少部分填充于通孔,一体式导电结构也就是一体成型的导电结构,由此,相较于相关技术中采用种子层结合电镀工艺技术的封装载板,可降低填充于通孔内的导电结构的制作难度,减少制作工序,降低制作成本,从而可降低封装载板的制作难度和制作成本;同时降低因基板与金属两种材料热膨胀系数差异大,热失配产生热应力问题,提高封装载板的稳定性和可靠性。

4、在其中一个实施例中,所述一体式导电结构包括第一部分,所述第一部分填充于所述通孔。

5、可选地,所述第一部分包括相对设置的第一端面和第二端面,以及连接所述第一端面和所述第二端面的连接侧面,所述连接侧面覆盖所述通孔的侧壁;所述基板包括沿其厚度方向相对设置的第一面和第二面,所述第一端面位于所述第一部分靠近所述第一面的一侧,所述第二端面位于所述第一部分靠近所述第二面的一侧。

6、可选地,所述第一端面与所述第一面平齐,所述第二端面与所述第二面平齐。

7、可选地,所述一体式导电结构包括第二部分,所述第二部分设置于所述第一面,且与所述第一部分连接。

8、可选地,所述第二部分覆盖所述第一部分的第一端面。

9、可选地,所述一体式导电结构的材质包括导电膏、导电油墨中的一种。

10、在其中一个实施例中,所述封装载板还包括导电层;所述导电层设置于所述第二面,并与所述第一部分连接。

11、可选地,所述导电层包括第一子导电层和第二子导电层;所述第一子导电层设置于所述第二面,并与所述第一部分连接;所述第二子导电层设置于所述第一子导电层背离所述基板的一侧。

12、可选地,所述第一子导电层覆盖所述第一部分的第二端面。

13、可选地,所述第一子导电层的厚度为0.1um~2um。

14、可选地,所述第二子导电层的厚度为2um~20um。

15、可选地,所述第一子导电层的材质包括金属材料。

16、可选地,所述第二子导电层的材质包括金属材料。

17、可选地,所述第一子导电层的材质为钛、铜、铝、镍、金、锡、银中的至少一种。

18、可选地,所述第二子导电层的材质包括铜、铝、镍、金、锡、银中的至少一种。

19、根据本技术的另一个方面,提供一种封装载板的制作方法,包括:

20、提供基板,并在所述基板上形成沿所述基板的厚度方向贯通的通孔;

21、形成至少部分填充于所述通孔的一体式导电结构。

22、本技术实施例提供的封装载板的制作方法,通过形成至少部分填充于通孔的一体式导电结构,也就是形成一体成型的导电结构,由此,相较于相关技术中采用种子层结合电镀工艺技术的封装载板,可降低填充于通孔内的导电结构的制作难度,减少制作工序,降低制作成本,从而可降低封装载板的制作难度和制作成本;同时降低因基板与金属两种材料热膨胀系数差异大,热失配产生热应力问题,提高封装载板的稳定性和可靠性。

23、在其中一个实施例中,所述基板包括沿其厚度方向相对设置的第一面和第二面;

24、所述形成至少部分填充于所述通孔的一体式导电结构的步骤,包括:

25、于所述基板的第二面形成第二介质层;

26、采用丝网印刷工艺于所述通孔内填充第一导电材料,以形成所述一体式导电结构。

27、可选地,所述形成至少部分填充于所述通孔的一体式导电结构的步骤,还包括:

28、在所述基板的第一面形成第一介质层;

29、对所述第一介质层进行图案化处理,以在所述第一介质层上定义出第一窗口,所述第一窗口与所述通孔在所述基板的厚度方向上的正投影至少部分重合。

30、可选地,所述采用丝网印刷工艺于所述通孔内填充第一导电材料,以形成所述一体式导电结构的步骤,包括:

31、采用丝网印刷于所述通孔以及所述第一窗口内填充第一导电材料;对所述第一导电材料进行干燥和烧结,并去除所述第一介质层和所述第二介质层。

32、可选地,所述对所述第一导电材料进行干燥和烧结,其中,干燥温度为100℃~200℃;烧结温度为200℃~500℃。

33、在其中一个实施例中,在所述形成至少部分填充于所述通孔的一体式导电结构的步骤之后,所述制作方法还包括:

34、在所述基板的第二面形成与所述一体式导电结构连接的导电层。

35、可选地,所述在所述基板的第二面形成与所述一体式导电结构连接的导电层的步骤,包括:

36、在所述基板的第二面形成第二导电材料层;

37、在所述第二导电材料层背离基板的一侧形成第三介质层,并对所述第三介质层进行图案化处理,以在所述第三介质层上定义出第二窗口,所述第二窗口与所述通孔在所述基板的厚度方向上的正投影至少部分重合;

38、形成位于所述第二窗口内的第二子导电层;

39、去除所述第三介质层,并对第二导电材料层进行图案化处理,得到第一子导电层。

40、根据本技术的又一个方面,提供一种半导体器件,包括根据上述任一实施例中所述的封装载板和半导体芯片,所述半导体芯片搭载于所述封装载板上,所述半导体芯片与所述封装载板上的一体式导电结构电连接。由此,可降低半导体器件的制作难度和成本,同时克服相关技术中因基板与金属两种材料热膨胀系数差异大,热失配产生热应力问题,降低半导体芯片在工作中出现性能下降、甚至功能失效问题的几率,提高半导体器件的稳定性和可靠性。

41、在其中一个实施例中,还包括第一绝缘层和第一重布线层;所述第一绝缘层设置于所述第二面并覆盖所述导电层;所述第一绝缘层上设置有第一过孔;所述第一重布线层设置于第一绝缘层背离所述基板的一侧;所述第一重布线层通过所述第一过孔与所述导电层电连接;所述半导体芯片设置于所述第一重布线层背离所述基板的一侧,并与所述第一重布线层电连接。

42、可选地,所述第一重布线层包括第三子导电层、第四子导电层和导电体;所述第三子导电层设置于所述第一绝缘层背离所述基板的一侧;所述第四子导电层位于所述第三子导电层背离所述基板的一侧;所述导电体填充于所述第一过孔,所述导电体与所述导电层、所述第三子导电层和所述第四子导电层电连接。

43、可选地,所述导电体包括第五子导电层和第六导电部,第六导电部位于所述第一过孔内,并与所述第四子导电层连接;所述第五子导电层覆盖所述第一过孔的侧壁,所述第五子导电层背离所述第一过孔侧壁的一侧与所述第六导电部连接;所述第五子导电层与所述第六导电部均与所述导电层连接。

44、可选地,所述第五子导电层与所述第三子导电层同层设置且相互连接。

45、可选地,所述第四子导电层和所述第六导电部为一体成型。

46、可选地,还包括第一导电凸部,第一导电凸部设置于所述半导体芯片和所述第一重布线层之间,所述第一导电凸部的一端连接所述半导体芯片,所述第一导电凸部的另一端连接所述第一重布线层。

47、可选地,还包括封装层,所述封装层设置于所述半导体芯片背离所述基板的一侧;所述封装层覆盖所述半导体芯片、第一重布线层和所述第一绝缘层。

48、根据本技术的又一个方面,提供一种半导体组件,包括上述任一实施例中所述的半导体器件和印刷电路板;所述印刷电路板位于所述封装载板背离所述半导体芯片的一侧,所述印刷电路板通过所述一体式导电结构与所述半导体芯片电连接。由此,可降低半导体组件的制作难度和成本,提高半导体组件的稳定性和可靠性。

49、在其中一个实施例中,还包括第二绝缘层和第二重布线层;所述第二绝缘层设置于所述第一面,并覆盖所述第二部分;所述第二绝缘层上设置有第二过孔,所述第二重布线层通过所述第二过孔与所述第二部分电连接;所述印刷电路板设置于所述第二重布线层背离所述基板的一侧,并与所述第二重布线层电连接。

50、可选地,所述第二重布线层包括第一子部和第二子部,所述第一子部填充于所述第二过孔内,并与所述第二部分连接;所述第二子部设置于所述第二绝缘层背离所述基板的一侧,并与所述第一子部连接。

51、可选地,所述第一子部和所述第二子部为一体成型。

52、可选地,还包括第二导电凸部,所述第二导电凸部设置于所述印刷电路板和所述第二重布线层之间,所述第二导电凸部的一端连接所述印刷电路板,所述第二导电凸部的另一端连接所述第二重布线层。

- 还没有人留言评论。精彩留言会获得点赞!