半导体装置的制备方法、半导体装置和电子设备

本公开的实施例涉及一种半导体装置的制备方法、半导体装置和电子设备。

背景技术:

1、单片三维集成是一种先进的集成电路技术,它旨在通过垂直堆叠多层器件来提高芯片的性能和功能密度。单片三维集成技术需要后道兼容的晶体管技术来实现多层器件的有效堆叠和互连。

2、然而,硅基器件例如mosfet(metal-oxide-semiconductor field-effecttransistor,金属氧化物半导体场效应晶体管)和finfet(fin field-effect transistor,鳍式场效应晶体管),制造工艺复杂且成本高,它们通常需要单晶硅衬底来确保器件的性能和可靠性,这使得它们难以实现后道兼容。

技术实现思路

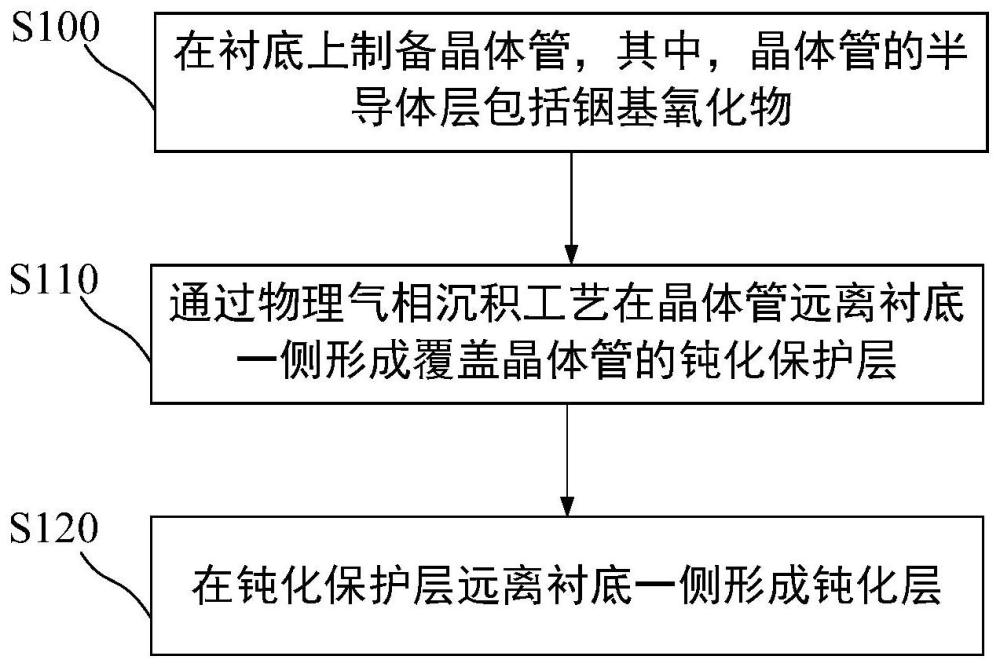

1、本公开至少一个实施例提供一种半导体装置的制备方法,所述制备方法包括:在衬底上制备晶体管,其中,所述晶体管的半导体层包括铟基氧化物;通过物理气相沉积工艺在所述晶体管远离所述衬底一侧形成覆盖所述晶体管的钝化保护层;在所述钝化保护层远离所述衬底一侧形成钝化层。

2、例如,在本公开一实施例提供的制备方法,还包括:在所述衬底上通过半导体制备工艺形成硅基半导体器件层,其中,所述衬底为硅衬底,在所述硅基半导体器件层远离所述衬底一侧制备所述晶体管。

3、例如,在本公开一实施例提供的制备方法中,所述铟基氧化物包括igzo或igo。

4、例如,在本公开一实施例提供的制备方法中,所述钝化保护层包括钇氧化物或铝氧化物。

5、例如,在本公开一实施例提供的制备方法中,所述物理气相沉积工艺包括溅射工艺或蒸镀工艺。

6、例如,在本公开一实施例提供的制备方法中,所述在所述钝化保护层远离所述衬底一侧形成钝化层,包括:通过化学气相沉积工艺在所述钝化保护层远离所述衬底一侧形成钝化层。

7、例如,在本公开一实施例提供的制备方法中,所述钝化层包括氮化硅、氧化硅、氮氧化硅或氧化铪中的至少一种。

8、例如,在本公开一实施例提供的制备方法中,所述晶体管为背栅晶体管。

9、例如,在本公开一实施例提供的制备方法中,所述在衬底上制备晶体管,包括:在所述衬底上形成栅极;在所述栅极远离所述衬底一侧覆盖栅极绝缘层;在所述栅极绝缘层远离所述衬底一侧形成所述半导体层;在所述半导体层远离所述衬底一侧形成源极和漏极,其中,所述源极和所述漏极被所述半导体层中用作沟道区的部分间隔开。

10、例如,在本公开一实施例提供的制备方法中,在所述通过物理气相沉积工艺在所述晶体管远离所述衬底一侧形成覆盖所述晶体管的钝化保护层之前,还包括:进行退火处理,其中,所述退火处理的温度范围为200摄氏度至300摄氏度。

11、本公开至少一个实施例提供一种半导体装置,所述半导体装置包括:衬底;晶体管,形成在所述衬底上,其中,所述晶体管的半导体层包括铟基氧化物;钝化保护层,通过物理气相沉积工艺形成且覆盖在所述晶体管远离所述衬底一侧;钝化层,覆盖在所述钝化保护层远离所述衬底一侧。

12、例如,在本公开一实施例提供的半导体装置,还包括:硅基半导体器件层,形成在所述衬底和所述晶体管之间,其中,所述衬底包括硅衬底,所述晶体管形成在所述硅基半导体器件层远离所述衬底一侧。

13、例如,在本公开一实施例提供的半导体装置中,所述晶体管为背栅晶体管。

14、本公开至少一个实施例提供一种电子设备,所述电子设备包括本公开任一实施例提供的半导体装置。

技术特征:

1.一种半导体装置的制备方法,包括:

2.根据权利要求1所述的制备方法,还包括:

3.根据权利要求1所述的制备方法,其中,所述铟基氧化物包括igzo或igo。

4.根据权利要求1所述的制备方法,其中,所述钝化保护层包括钇氧化物或铝氧化物。

5.根据权利要求1所述的制备方法,其中,所述物理气相沉积工艺包括溅射工艺或蒸镀工艺。

6.根据权利要求1所述的制备方法,其中,所述在所述钝化保护层远离所述衬底一侧形成钝化层,包括:

7.根据权利要求1所述的制备方法,其中,所述钝化层包括氮化硅、氧化硅、氮氧化硅或氧化铪中的至少一种。

8.根据权利要求1或2所述的制备方法,其中,所述在衬底上制备晶体管,包括:

9.根据权利要求1所述的制备方法,在所述通过物理气相沉积工艺在所述晶体管远离所述衬底一侧形成覆盖所述晶体管的钝化保护层之前,还包括:

10.一种半导体装置,包括:

11.根据权利要求10所述的半导体装置,还包括:

12.根据权利要求10所述的半导体装置,其中,所述晶体管为背栅晶体管。

13.一种电子设备,包括:

技术总结

一种半导体装置的制备方法、半导体装置和电子设备。该半导体装置的制备方法包括:在衬底上制备晶体管,其中,晶体管的半导体层包括铟基氧化物;通过物理气相沉积工艺在晶体管远离衬底一侧形成覆盖晶体管的钝化保护层;在钝化保护层远离衬底一侧形成钝化层。该半导体装置的制备方法可以提高半导体装置的性能和稳定性。

技术研发人员:唐建石,杨慧敏,李怡均,杜宜威,安然,高滨,钱鹤,吴华强

受保护的技术使用者:清华大学

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!