具有垂直晶体管的存储器件及其形成方法与流程

背景技术:

1、本公开的实施例涉及形成具有垂直晶体管的存储器件的方法、存储器件及其存储系统。

2、平面存储单元向更小尺寸的可缩放性取决于改进工艺技术、电路设计、编程算法和制造工艺。然而,随着存储单元的特征尺寸接近下限,平面工艺和制造技术变得越来越具有挑战性和昂贵。结果,平面存储单元的存储密度达到了上限。

3、为了解决平面存储单元中存储密度的限制,已经引入了三维(3d)存储架构。因此,3d存储架构的引入为平面存储单元的限制提供了有前途的解决方案。

技术实现思路

1、本文公开了3d存储器件及其形成方法的实施例。

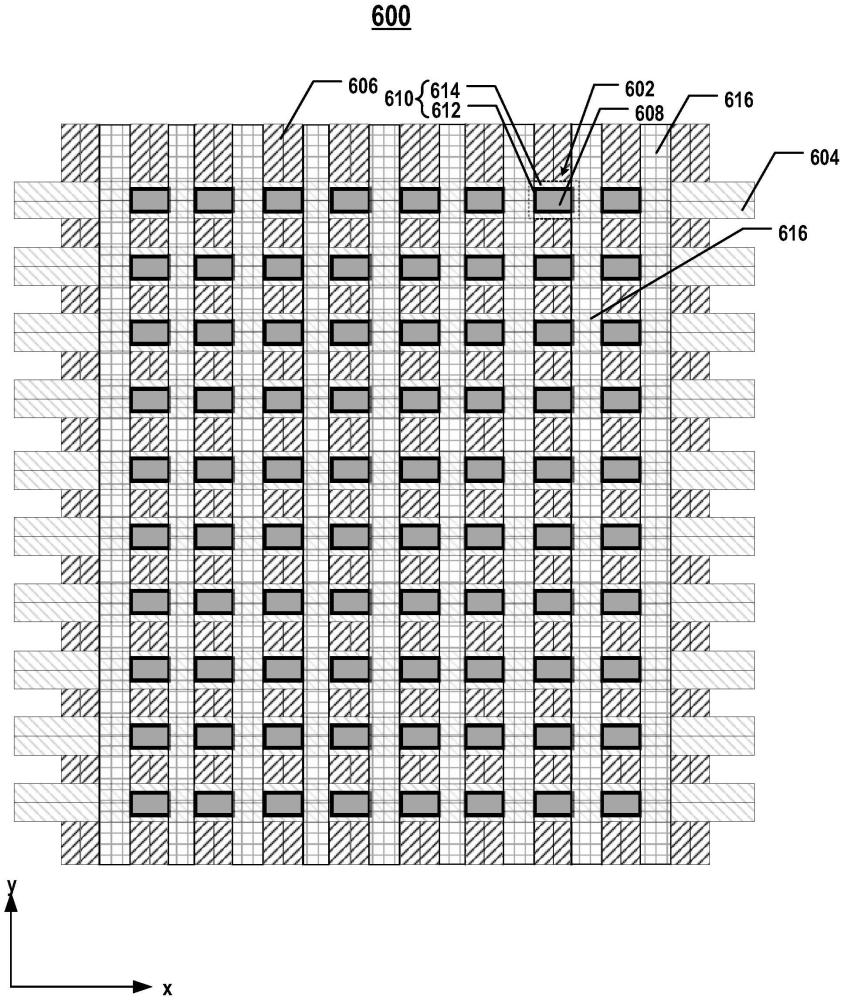

2、在一些方面,存储器件可以包括存储单元的阵列,每个存储单元包括垂直晶体管。沿第一方向,垂直晶体管中的一个垂直晶体管可以在平面图中布置在两个分隔结构之间。每个所述分隔结构可以包括突起,并且分隔结构和对应的突起可以是一体的。存储器件可以包括多条位线,所述多条位线包括至少一个导电层。至少一个导电层可以布置在两个分隔结构的两个突起之间并且在垂直晶体管中的所述一个垂直晶体管上,以将位线中的一条位线与垂直晶体管中的所述一个垂直晶体管耦合。

3、在一些实施方式中,平面图基于沿第一方向的第一平面。布置在两个突起之间的至少一个导电层在第二平面上的投影与两个分隔结构中的每个在第二平面上的投影基本不重叠,第二平面垂直于第一平面。

4、在一些实施方式中,存储器件还可以包括在第一方向上延伸并且被配置为连接垂直晶体管的栅极的多条字线,字线中的一条字线的深度小于分隔结构中的一个分隔结构的深度。

5、在一些实施方式中,存储器件还可以包括多个储存元件,所述多个储存元件中的一个储存元件在位线的相对侧处与垂直晶体管中的对应的垂直晶体管连接。

6、在一些实施方式中,所述多个储存元件中的所述一个储存元件可以包括电容结构。

7、在一些实施方式中,电容结构布置在位线的相对侧处的一个或多个层间电介质(idl)层中。

8、在一些实施方式中,存储单元的阵列布置在主存储器区域中。存储器件还可以包括电容结构触点,其布置在主存储器区域外部的外围区域中并与主存储器区域中的电容结构电连接,电容结构触点在垂直晶体管延伸的第三方向上延伸并且包括接合部分,并且电容结构触点的侧壁在接合部分处包括交错的轮廓。

9、在一些实施方式中,位线的至少一个导电层的表面与两个分隔结构的两个突起的表面基本平齐。

10、在一些实施方式中,至少一个导电层可以包括接触层,所述接触层布置在两个突起之间并且与垂直晶体管中的所述一个垂直晶体管接触;以及金属层,其布置在两个突起之间且位于接触层上。

11、在一些实施方式中,接触层可以包括硅化物;并且金属层可以包括钨。

12、在一些实施方式中,至少一个导电层可以包括布置在两个突起之间并且与垂直晶体管中的所述一个垂直晶体管接触的互连层。

13、在一些实施方式中,互连层布置在主存储器区域中并且被配置为与垂直晶体管中的所述一个垂直晶体管连接;并且牺牲层布置在主存储器区域外部的外围区域中,主存储器区域中的互连层的表面与外围区域中的牺牲层的表面基本平齐。

14、在一些实施方式中,氧化物焊盘层布置在外围区域中并且在牺牲层下方。

15、在一些实施方式中,互连层可以包括多晶硅。

16、在一些实施方式中,互连层的表面与两个分隔结构的两个突起的表面基本平齐。

17、在一些实施方式中,位线还可以包括在一个或多个层间电介质(ild)层中并且布置在互连层上并与互连层接触的金属层。

18、在一些实施方式中,互连层在垂直于第一方向的第二方向上并在垂直晶体管中的所述一个垂直晶体管上连续延伸。

19、在一些实施方式中,金属层可以包括设置在互连层上的金属点。

20、在一些实施方式中,互连层在垂直于第一方向的第二方向上断开;并且金属层可以包括连接互连层的金属线。

21、在一些实施方式中,存储单元的阵列布置在第一半导体结构中;并且存储器件还可以包括键合到第一半导体结构并且包括外围电路的第二半导体结构,外围电路耦合到存储单元的阵列并且被配置为通过位线控制存储单元的阵列。

22、在又一些方面,提供了一种存储系统。存储系统可以包括被配置为存储数据的存储器件,并且存储器件包括:具有外围电路的第一半导体结构;第二半导体结构,其键合到第一半导体结构并且包括存储单元的阵列,每个存储单元包括垂直晶体管,其中沿着第一方向,垂直晶体管中的一个垂直晶体管在平面图中布置在两个分隔结构之间,每个所述分隔结构包括突起,且分隔结构与对应的突起是一体的;以及多条位线,其包括至少一个导电层,其中至少一个导电层布置在两个分隔结构的两个突起之间以及垂直晶体管中的所述一个垂直晶体管上,以将位线中的一条位线与垂直晶体管中的所述一个垂直晶体管耦合,存储单元通过位线耦合到外围电路。存储系统还可以包括存储器控制器,其耦合到存储器件并且被配置为通过外围电路控制存储单元。

23、在又一些方面,提供了一种形成存储器件的方法。该方法可以包括:形成多个分隔结构;形成存储单元的阵列,每个存储单元包括垂直晶体管,其中沿垂直于多个分隔结构延伸的第二方向的第一方向,垂直晶体管中的一个垂直晶体管在平面图中布置在两个分隔结构之间;形成多个突起,其中每个突起在一个所述分隔结构上;以及形成包括至少一个导电层的多条位线,其中至少一个导电层布置在两个分隔结构的两个突起之间的凹陷中并且在垂直晶体管中的所述一个垂直晶体管上,以将位线中的一条位线与垂直晶体管中的所述一个垂直晶体管耦合。

24、在一些实施方式中,该方法还可以包括在一个或多个层间电介质(idl)层中形成多个电容结构,所述电容结构中的一个电容结构在位线的相对侧处与垂直晶体管中的对应的垂直晶体管连接。

25、在一些实施方式中,存储单元的阵列和电容结构布置在主存储器区域中;并且该方法还可以包括:在主存储器区域外部的外围区域中形成电容结构触点,并且电容结构触点与主存储器区域中的电容结构中的所述一个电容结构电连接,与垂直晶体管中的所述一个垂直晶体管连接,电容结构触点在垂直晶体管延伸的第三方向上延伸并且包括接合部分,并且电容结构触点的侧壁在接合部分处包括交错的轮廓。

26、在一些实施方式中,形成多个分隔结构可以包括制备衬底,衬底包括器件层、处理层以及器件层和处理层之间的掩埋氧化物(box)层;至少通过box层去除器件层和处理层的第一部分以沿第二方向形成多个第一沟槽;以及将第一电介质材料填充到多个第一沟槽中的每者中,以在衬底中形成多个分隔结构。

27、在一些实施方式中,该方法还可以包括去除器件层的第二部分以沿第一方向形成多个第二沟槽,其中:形成存储单元可以包括形成对应于多个第二沟槽的垂直晶体管;并且该方法还可以包括形成多条字线,每条字线对应于多个第二沟槽中的一个并且被配置为连接存储单元的阵列的一行中的垂直晶体管的栅极。

28、在一些实施方式中,多个第二沟槽中的一个第二沟槽的深度小于多个第一沟槽中的一个第一沟槽的深度。

29、在一些实施方式中,形成突起可以包括在衬底的正面将衬底键合到载体衬底;以及去除衬底的剩余的处理层以暴露box层和多个分隔结构,所述多个分隔结构中的每个分隔结构的一端形成突起,并且凹陷形成在两个分隔结构的两个突起之间。

30、在一些实施方式中,凹陷是沿第二方向延伸的第三沟槽。

31、在一些实施方式中,形成多条位线可以包括在第三沟槽中去除box层的位于垂直晶体管中的一个垂直晶体管上的一部分;以及在第三沟槽中沉积至少一个导电层,至少一个导电层的表面与多个分隔结构的两个突起的表面基本平齐。。

32、在一些实施方式中,至少一个导电层可以包括布置在第三沟槽中并与垂直晶体管中的所述一个垂直晶体管接触的接触层;以及金属层,其布置于第三沟槽中且在接触层上。

33、在一些实施方式中,接触层可以包括硅化物;并且金属层可以包括钨。

34、在一些实施方式中,形成多个分隔结构可以包括:制备包括硅衬底、硅衬底中的切割层和硅衬底上的氧化物焊盘层的转移衬底;在氧化物焊盘层上形成牺牲层;去除转移衬底的器件层中的氧化物焊盘层和牺牲层的部分,以沿第二方向形成多个第四沟槽;将第二电介质材料填充到多个第四沟槽中的每者中以形成多个分隔结构;沿切割层从转移衬底分离器件层;将器件层的正面键合到载体衬底以形成第一半导体结构;以及去除器件层的背面以暴露多个分隔结构。

35、在一些实施方式中,氧化物焊盘层和牺牲层的被去除的部分是氧化物焊盘层和牺牲层的第一部分;存储单元的阵列布置在主存储器区域中;并且氧化物焊盘层和牺牲层的第二部分保留在主存储器区域外部的外围区域中。

36、在一些实施方式中,该方法还可以包括将离子注入施加到转移衬底中的一定深度以在转移衬底中形成切割层。

37、在一些实施方式中,该方法还可以包括去除第一半导体结构的一部分以沿第一方向形成多个第五沟槽,其中:形成存储单元可以包括形成对应于多个第五沟槽的垂直晶体管;并且该方法还可以包括形成多条字线,每条字线对应于多个第五沟槽中的一个并且被配置为连接存储单元的阵列的一行中的垂直晶体管的栅极。

38、在一些实施方式中,形成突起可以包括:将第一半导体结构的正面键合到基底衬底以形成第二半导体结构;去除第二半导体结构的部分以暴露出牺牲层;以及使用掩模去除牺牲层和氧化物焊盘层的部分以暴露垂直晶体管和多个分隔结构,所述多个分隔结构中的每个分隔结构的一端形成突起,并且凹陷形成在两个分隔结构的两个突起之间。

39、在一些实施方式中,多个第五沟槽中的一个的深度小于多个分隔结构中的一个的深度。

40、在一些实施方式中,凹陷是沿第二方向延伸的第六沟槽。

41、在一些实施方式中,形成多条位线还可以包括:在第六沟槽中沉积与垂直晶体管中的所述一个垂直晶体管接触的互连层,互连层的表面与多个分隔结构的两个突起的表面基本平齐,至少一个导电层包括互连层;以及在一个或多个层间电介质(ild)层中并在互连层上形成金属层。

42、在一些实施方式中,互连层可以包括多晶硅,并且金属层可以包括钨。

43、在一些实施方式中,金属层可以包括互连层上的金属点。

44、在一些实施方式中,多个第五沟槽中的一个第五沟槽的深度大约等于多个分隔结构中的一个分隔结构的深度。

45、在一些实施方式中,形成多条位线可以包括:在凹陷中沉积并与垂直晶体管中的所述一个垂直晶体管接触的互连层,互连层的表面与多个分隔结构的两个突起的表面基本平齐,至少一个导电层包括互连层;以及在一个或多个层间电介质(ild)层中和互连层上形成金属层。

46、在一些实施方式中,互连层可以包括多晶硅,并且金属层可以包括钨。

47、在一些实施方式中,互连层在第二方向上断开;并且金属层可以包括连接互连层的金属线。

48、在一些实施方式中,形成多个分隔结构可以包括:制备包括硅衬底中的切割层和包括硅衬底上的氧化物焊盘层的器件层的转移衬底,并且在氧化物焊盘层上形成牺牲层;沿着切割层从转移衬底分离出器件层;将器件层的正面键合到载体衬底以形成第三半导体结构;去除第三半导体结构的部分以沿第二方向形成多个第七沟槽;以及将第三电介质材料填充到多个第七沟槽中的每者中,以形成多个分隔结构。

- 还没有人留言评论。精彩留言会获得点赞!