功率半导体器件的终端结构、制造方法及功率器件与流程

本发明涉及半导体器件,更具地地,涉及一种功率器件结终端结构、制造方法及功率器件。

背景技术:

1、在电力电子领域,功率半导体器件作为关键部件,其特性对系统性能的实现和改善有着至关重要的作用。功率半导体器件最主要的特点之一是其阻断高压的能力,根据应用场合的不同,硅器件的击穿电压可以从用于电源系统的25v以下到用于电力传输的8.5kv。功率半导体器件阻断高压的能力主要取决于器件结构中特定pn结的反偏击穿电压。但随着pn结外加反向偏压增大,会引起雪崩击穿现象,该现象是限制功率器件最大工作电压的主要因素。在功率半导体器件中,受pn结弯曲或pn结终止处表面非理想因素的影响,pn结表面附近或结弯曲处的局部区域往往相对于体内平行平面结提前出现击穿现象。结终端就是为了减小局部电场、提高表面击穿电压及可靠性、使器件实际击穿电压更接近平行平面结的理想值而专门设计的特殊结构。

2、普通晶闸管、相控晶闸管、gto和igct及其衍生器件都可称之为晶闸管类器件,这些器件都是由晶闸管发展而来,其导通的工作原理都与晶闸管一致。实际上,几乎所有的晶闸管类器件都采用了斜角终端造型技术。对于仅需要正向阻断特性的晶闸管类器件(例如逆导型晶闸管、非对称型gto、逆导型igct等),仅需要进行正面的斜角终端造型;对于需要正反向阻断特性的晶闸管类器件(例如普通晶闸管、逆阻型igct等),需要同时进行正面和背面的斜角终端造型。在6.5kv及以上电压等级,负斜角造型终端和双负斜角造型终端由于基区宽度小、可靠性高等优点,得到了广泛应用。

3、典型的负斜角造型终端如图1中所示,其主要工作原理是利用斜角造型展宽了p基区内的耗尽区(耗尽区宽度由wp变为ws),从而降低了表面电场,提升了阻断电压。典型的双负斜角造型终端如图2中所示,在承受正向阻断电压时,其耗尽区在j2结附近扩展;在承受反向阻断电压时,其耗尽区在j1结附近扩展,如图3中所示。在实际的制造工艺中,图2和图3中的p1区和p2区多采用扩散工艺同时形成,因此其掺杂浓度具有对称型;再对其正面和背面进行对称的角度造型,即可获得几乎相同的正向阻断电压和反向阻断电压。

4、由图1可知,p基区内的斜面耗尽区宽度ws主要由终端造型角度θ和p基区垂直方向的耗尽区宽度wp决定,而wp则主要取决于p基区结深和掺杂浓度。因此,对于高压和超高压的晶闸管类器件来说,为了实现更高的阻断电压,需求器件具有较深的p基区结深(高压器件通常要求p基区结深大于100μm)和较低的p基区掺杂浓度(峰值掺杂浓度通常小于1e16cm-3),同时终端造型角度θ要非常小(通常在10°以下)。但是目前主要存在以下问题:(1)p基区深结使得工艺过程中扩散所需时间大大增加,芯片承受的热应力也随之增加,容易在芯片中产生不必要的晶格损伤;(2)硅衬底通常具有固定且均匀的掺杂,较深的p基区结深和低p基区掺杂浓度对于热扩散工艺来说是矛盾的,为了达到此效果,通常需要进一步增加热扩散的时间,增加流片时间和工艺成本,同时芯片晶格损伤的风险进一步增加;(3)p基区结深增加使阴极侧npn晶体管放大系数减小,阴极侧发射极发射效率降低,芯片开通损耗和通态压降相应增加。

5、目前专利的解决方法主要是通过将晶闸管类器件的芯片有源区和终端区采用不同结深的p基区来改善芯片特性。如瑞士abb公司在2010年提出了一种浅p基区功率半导体器件(cn103222056b),如图4中所示,芯片总厚度减小,降低了导通压降,改进了反向恢复电荷、关断时间和最大浪涌电流。该器件的衬底厚度减薄,同时为了维持高的击穿电压,改进了终端结构。采用了负斜角终端结构,终端p基区较有源区p基区结深更深,浓度较有源区浓度低,终端区掺杂浓度较有源区在横向上有快速下降,增强了雪崩能力,提高了击穿电压。

6、清华大学在2020年提出了一种功率半导体器件(cn111755501a),该专利结构与abb专利类似,如图5中所示。该专利提出的芯片边缘终端结构增加了p-基区的厚度,同时终端区p基区的掺杂浓度小于有源区p基区的浓度,使得耗尽层宽度增加,且优化后的结构使耗尽层扩展不再受到高浓度p+基区的限制,可以使斜面边缘的耗尽层宽度增加至图5中的w5,从而降低峰值电场强度,提高芯片的耐压能力。

7、然而,现有专利结构芯片终端区的p基区结深并没有降低,仍然需要通过长时间的热扩散工艺形成,因此前面所述的问题1和问题2仍然存在,即:(1)p基区深结使得工艺过程中扩散所需时间大大增加,芯片承受的热应力也随之增加,容易在芯片中产生不必要的晶格损伤;(2)较深的p基区结深和低p基区掺杂浓度对于热扩散工艺来说是矛盾的,为了达到此效果,通常需要进一步增加热扩散的时间,增加流片时间和工艺成本,同时芯片晶格损伤的风险进一步增加。

8、此外,仿真研究中发现现有专利结构还存在问题(4),即:现有专利结构的负斜角终端p基区的深结是热扩散形成的,掺杂浓度通常呈高斯分布或余误差分布,在承受高阻断电压状态下其电场强度峰值集中在终端较集中的区域,如图6中所示,不利于器件的长期可靠性,且终端的效率不高。

技术实现思路

1、(一)要解决的技术问题

2、本发明要解决的技术问题包括:第一,p基区深结使得工艺过程中扩散所需时间大大增加,芯片承受的热应力也随之增加,容易在芯片中产生不必要的晶格损伤;第二,较深的p基区结深和低p基区掺杂浓度对于热扩散工艺来说是矛盾的,为了达到此效果,通常需要进一步增加热扩散的时间,增加流片时间和工艺成本,同时芯片晶格损伤的风险进一步增加;第三,现有专利结构的负斜角终端p基区的深结是热扩散形成的,掺杂浓度通常呈高斯分布或余误差分布,在承受高阻断电压状态下其电场强度峰值集中在终端较集中的区域,不利于器件的长期可靠性,且终端的效率不高。

3、(二)技术方案

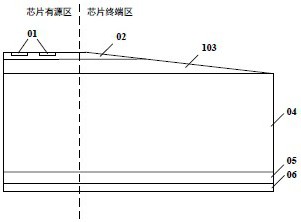

4、为了达到上述目的,本发明采用一种功率半导体器件的终端结构,所述终端结构位于功率半导体器件芯片的边缘部分,与芯片有源区相接;所述终端结构至少具有第一导电类型的第一基区,和位于第一基区一侧的第二基区,所述第二基区具有第二导电类型,所述第二导电类型与第一导电类型相反;所述终端结构中,至少在所述第二基区的远离第一基区的表面与芯片有源区所在的第一主面形成负角,使得所述终端结构部分的芯片厚度至少在所述第一主面上随着到芯片有源区的距离增加而减小;其中,所述第二基区至少具有一均匀掺杂的区域。

5、在一个优选方案中,仅在所述第二基区的远离第一基区的表面与芯片有源区所在的第一主面形成负角,使得所述终端结构部分的芯片厚度在所述第一主面上随着到芯片有源区的距离增加而减小;在相对于第一主面的第二主面侧为平面结构。

6、在一个优选方案中,所述终端结构在与第一主面相对的第二主面也形成一负角结构,使得所述终端结构部分的芯片厚度在第一主面和第二主面都随着到芯片有源区的距离增加而减小。

7、在一个优选方案中,所述终端结构在第二基区的与第一基区相对的另一侧,设置有第二导电类型的第三基区,所述第三基区具有均匀掺杂的杂质浓度,且杂质浓度与第二基区不同。

8、在一个优选方案中,所述第一基区为n-基区,所述第二基区为p基区,所述第三基区为p+基区,所述p基区的厚度范围为50-200μm,掺杂浓度为1e13-1e15cm-3,所述p+基区的厚度范围为10-70μm,掺杂浓度为1e15-5e17cm-3。

9、在一个优选方案中,所述终端结构在所述第二基区的与第一基区相对的另一侧,设置有第二导电类型的第三基区,所述第三基区的掺杂浓度沿芯片垂直方向改变。

10、在一个优选方案中,所述第一基区为n-基区,所述第二基区为p基区,所述第三基区为p+基区,所述p基区的厚度范围为50-200μm,掺杂浓度为1e13-1e15cm-3,所述p+基区的厚度范围为10-70μm,峰值掺杂浓度为1e16-5e18cm-3。

11、在一个优选方案中,所述第一基区为n-基区,所述第二基区为p基区,所述终端结构在第二基区的与第一基区相对的另一侧,设置有p+基区;所述n-基区的与p基区相对的另一侧,设置有均匀掺杂的p型阳极发射区,p型阳极发射区与n-基区相对应的另一侧,设置有p+阳极发射区。

12、在一个优选方案中,所述p+基区与所述p+阳极发射区为均匀掺杂的。

13、在一个优选方案中,所述p+基区的厚度范围为10-70μm,掺杂浓度为1e15-5e17cm-3;p基区和p型阳极发射区的厚度范围为50-200μm,掺杂浓度为1e13-1e15cm-3;p+阳极发射区的厚度范围为1-20μm,掺杂浓度为1e17-5e19cm-3。

14、在一个优选方案中,所述p+基区与所述p+阳极发射区的掺杂浓度沿芯片垂直方向改变。

15、在一个优选方案中,所述p+基区的厚度范围为10-70μm,峰值掺杂浓度为1e16-5e18cm-3;p基区和p型阳极发射区的厚度范围为50-200μm,掺杂浓度为1e13-1e15cm-3;p+阳极发射区的厚度范围为1-20μm,掺杂浓度为1e17-5e19cm-3。

16、在一个优选方案中,所述终端结构的斜角采用台面结构,至少所述第一基区和所述第二基区的交界面延伸至所述台面结构。

17、在一个优选方案中,所述终端结构的斜角采用台面结构,所述n-基区与所述p基区的交界面延伸至所述台面结构,且所述n-基区与所述p型阳极发射区的交界面延伸至所述台面结构。

18、本发明还提供一种垂直结构的半导体器件,所述半导体器件包含有源区及终端区,所述终端区采用如如上任一项所述的终端结构。

19、在一个优选方案中,所述半导体器件为普通晶闸管、相控晶闸管、门极可关断晶闸管、集成门极换流晶闸管或上述器件的衍生器件。

20、本发明还提供一种功率器件,所述功率器件采用如如上所述的半导体器件。

21、本发明还提供一种功率半导体器件的终端结构的制造方法,其中所述第二基区通过外延工艺或者硅-硅键合工艺形成。

22、(三)有益效果

23、本发明提出的p基区均匀掺杂的负斜角终端结构可以有效缓解常规负斜角终端结构电场易集中的缺点,平衡了负斜角终端近有源区一侧的电场强度,提高了终端的有效利用率和阻断电压。在相同的阻断电压下,该结构较传统结构能够有效降低电场强度峰值,提升了器件的长期可靠性。此外,该结构中均匀掺杂的p基区可以通过外延生长或硅-硅键合的工艺形成,能够避免长时间热扩散造成的硅片热应力和晶格损伤问题。

- 还没有人留言评论。精彩留言会获得点赞!