半导体器件及其制作方法与流程

本申请属于半导体,具体涉及一种半导体器件及其制作方法。

背景技术:

1、平面(2d)存储器,存储单元在一个平面上布置,随着存储容量的增加,每个存储单元的特征尺寸逐渐减小,导致制作大容量存储器的制作成本及难度显著增大。三维(3d)存储器,多层存储单元垂直堆叠,在存储单元的特征尺寸相同的条件下,三维存储器与平面存储器相比,可具有更大的存储容量。

2、三维存储器通常采用o/p堆叠结构,即多晶硅层(poly)和氧化物层(oxide)交替层叠,形成多层多晶硅层和多层氧化物层堆叠的叠层阶梯结构。其中,每一层多晶硅层均采用阶梯连接结构与外围电路连接。

3、由于每一层多晶硅层在堆叠结构中所处深度不同,形成接触孔时,不同多晶硅层上可能会形成刻蚀量不足、部分刻蚀及刻蚀穿通等问题。对于部分刻蚀,由于刻蚀损伤,在后续接触孔清洗制程,容易出现接触孔底面多晶硅层过薄甚至穿孔。形成阶梯连接结构时,阶梯连接结构底部没有足够多晶硅以制备金属硅化物,接触阻抗急剧增加。

技术实现思路

1、本申请的目的在于提供一种半导体器件及其制作方法,以增大阶梯连接结构与多晶硅层接触面面积,降低接触电阻电容。

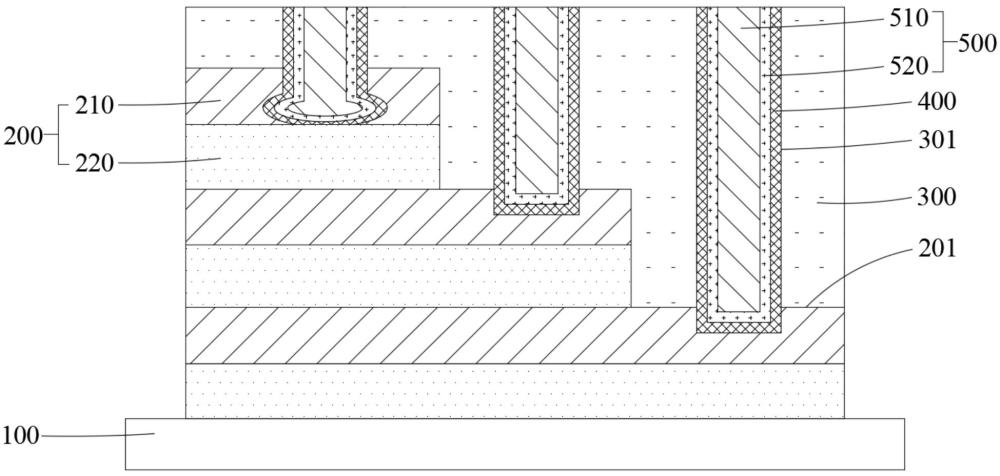

2、为了达到上述目的,本申请提供了一种半导体器件,包括:

3、衬底;

4、多个膜层对,竖直地堆叠在所述衬底一侧以形成堆叠结构,所述膜层对包括依次堆叠的隔离层和多晶硅层,所述堆叠结构至少一侧形成阶梯面;

5、覆盖层,形成在所述堆叠结构上并覆盖所述阶梯面,多个接触孔穿过所述覆盖层以分别连通多个所述多晶硅层;

6、金属硅化物层,形成在所述接触孔内且至少位于所述接触孔的底面,所述接触孔的底面为所述接触孔位于所述覆盖层的区段的竖直投影覆盖的部分内壁;

7、阶梯连接结构,填充在所述接触孔内,所述阶梯连接结构包括导电层,所述导电层通过所述金属硅化物层与所述多晶硅层连接。

8、可选的,所述金属硅化物层与所述多晶硅层直接连接;或

9、至少所述金属硅化物层靠近所述接触孔的所述底面一侧还形成有掺杂多晶材料层,所述掺杂多晶材料层形成于所述接触孔内,所述金属硅化物层与所述多晶硅层通过所述掺杂多晶材料层间接连接。

10、可选的,所述金属硅化物层与所述多晶硅层直接连接,所述接触孔延伸至所述多晶硅层中。

11、可选的,所述接触孔贯穿所述多晶硅层。

12、可选的,所述金属硅化物层与所述多晶硅层通过所述掺杂多晶材料层间接连接,所述接触孔延伸至所述多晶硅层中。

13、可选的,所述接触孔贯穿所述多晶硅层。

14、可选的,所述金属硅化物层至少还形成在所述接触孔位于所述覆盖层的区段的内壁。

15、可选的,至少所述金属硅化物层靠近所述接触孔的所述底面一侧以及所述覆盖层和所述金属硅化物层之间还形成有掺杂多晶材料层,所述掺杂多晶材料层形成于所述接触孔内,所述金属硅化物层与所述多晶硅层通过所述掺杂多晶材料层间接连接。

16、可选的,所述阶梯连接结构包括内衬层,所述内衬层至少形成在所述金属硅化物层和所述导电层之间。

17、可选的,所述内衬层包括氮化钛。

18、可选的,所述隔离层包括二氧化硅、氮化硅或氮氧化硅中至少一种,所述覆盖层包括二氧化硅、氮化硅或氮氧化硅中至少一种,所述金属硅化物层包括钛硅化物。

19、本申请还提供一种半导体器件的制作方法,包括:

20、在衬底上形成多个交替堆叠的多晶硅层和隔离层,刻蚀所述多晶硅层和所述隔离层形成堆叠结构,所述堆叠结构至少一侧形成有阶梯面;

21、在所述堆叠结构上形成覆盖层,所述覆盖层覆盖所述阶梯面,穿过所述覆盖层以形成分别连通多个所述多晶硅层的多个接触孔;

22、至少在所述接触孔的底面形成含硅材料层,所述接触孔的底面为其位于所述覆盖层的区段的竖直投影覆盖的部分内壁;

23、在所述接触孔内壁形成金属材料层,使所述金属材料层和所述含硅材料层反应形成金属硅化物层;

24、在所述接触孔内形成阶梯连接结构,所述阶梯连接结构通过所述金属硅化物层与所述多晶硅层连接。

25、可选的,所述含硅材料层包括非晶硅或掺杂的非晶硅,在形成所述金属硅化物层时,所述非晶硅或所述掺杂的非晶硅与所述金属材料层完全反应。

26、可选的,所述含硅材料层包括掺杂的非晶硅,所述含硅材料层中部分所述掺杂的非晶硅与所述金属材料层反应形成所述金属硅化物层,除所述部分所述掺杂的非晶硅之外的所述掺杂的非晶硅结晶形成掺杂多晶材料层。

27、可选的,所述金属材料层采用热沉积工艺形成。

28、可选的,所述掺杂的非晶硅采用原位掺杂工艺制作。

29、可选的,形成所述阶梯连接结构的方法包括:

30、在所述接触孔内依次形成内衬层和导电层,所述内衬层至少覆盖所述金属硅化物层,所述导电层填充所述接触孔,形成所述阶梯连接结构。

31、可选的,所述穿过所述覆盖层以形成分别连通多个所述多晶硅层的多个接触孔包括:

32、刻蚀所述覆盖层,形成连接孔,所述连接孔至少穿过所述覆盖层,并连通所述多晶硅层;

33、刻蚀清洗所述连接孔,在所述刻蚀清洗中至少去除所述连接孔底面的部分所述多晶硅层,从而形成所述接触孔。

34、可选的,刻蚀清洗所述连接孔时,将所述连接孔底面的所述多晶硅层部分或全部去除。

35、本申请公开的半导体器件及其制作方法具有以下有益效果:

36、本申请中,半导体器件包括衬底、堆叠结构、覆盖层、金属硅化物层和阶梯连接结构,堆叠结构形成在衬底一侧,堆叠结构包括多个交替堆叠的多晶硅层和隔离层,堆叠结构一侧形成阶梯面,覆盖层形成在堆叠结构上并覆盖阶梯面,覆盖层的多个接触孔分别连通多个多晶硅层,金属硅化物层形成在接触孔内且至少位于接触孔的底面,接触孔的底面为其位于覆盖层的区段的竖直投影覆盖的部分内壁,阶梯连接结构填充在接触孔内,阶梯连接结构包括导电层,导电层通过金属硅化物层与多晶硅层连接。至少形成在接触孔底面的金属硅化物层,增大了金属硅化物层和多晶硅层的接触面积,降低了阶梯连接结构和多晶硅层之间的接触阻抗。

37、本申请的其他特性和优点将通过下面的详细描述变得显然,或部分地通过本申请的实践而习得。

38、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

技术特征:

1.一种半导体器件,其特征在于,包括:

2.根据权利要求1所述的半导体器件,其特征在于,所述金属硅化物层与所述多晶硅层直接连接;或

3.根据权利要求2所述的半导体器件,其特征在于,所述金属硅化物层与所述多晶硅层直接连接,所述接触孔延伸至所述多晶硅层中。

4.根据权利要求3所述的半导体器件,其特征在于,所述接触孔贯穿所述多晶硅层。

5.根据权利要求2所述的半导体器件,其特征在于,所述金属硅化物层与所述多晶硅层通过所述掺杂多晶材料层间接连接,所述接触孔延伸至所述多晶硅层中。

6.根据权利要求5所述的半导体器件,其特征在于,所述接触孔贯穿所述多晶硅层。

7.根据权利要求1所述的半导体器件,其特征在于,所述金属硅化物层至少还形成在所述接触孔位于所述覆盖层的区段的内壁。

8.根据权利要求7所述的半导体器件,其特征在于,至少所述金属硅化物层靠近所述接触孔的所述底面一侧以及所述覆盖层和所述金属硅化物层之间还形成有掺杂多晶材料层,所述掺杂多晶材料层形成于所述接触孔内,所述金属硅化物层与所述多晶硅层通过所述掺杂多晶材料层间接连接。

9.根据权利要求1所述的半导体器件,其特征在于,所述阶梯连接结构包括内衬层,所述内衬层至少形成在所述金属硅化物层和所述导电层之间。

10.根据权利要求9所述的半导体器件,其特征在于,所述内衬层包括氮化钛。

11.根据权利要求1所述的半导体器件,其特征在于,所述隔离层包括二氧化硅、氮化硅或氮氧化硅中至少一种,所述覆盖层包括二氧化硅、氮化硅或氮氧化硅中至少一种,所述金属硅化物层包括钛硅化物。

12.一种半导体器件的制作方法,其特征在于,包括:

13.根据权利要求12所述的半导体器件的制作方法,其特征在于,所述含硅材料层包括非晶硅或掺杂的非晶硅,在形成所述金属硅化物层时,所述非晶硅或所述掺杂的非晶硅与所述金属材料层完全反应。

14.根据权利要求12所述的半导体器件的制作方法,其特征在于,所述含硅材料层包括掺杂的非晶硅,所述含硅材料层中部分所述掺杂的非晶硅与所述金属材料层反应形成所述金属硅化物层,除所述部分所述掺杂的非晶硅之外的所述掺杂的非晶硅结晶形成掺杂多晶材料层。

15.根据权利要求12~14任意一项所述的半导体器件的制作方法,其特征在于,所述金属材料层采用热沉积工艺形成。

16.根据权利要求14所述的半导体器件的制作方法,其特征在于,所述掺杂的非晶硅采用原位掺杂工艺制作。

17.根据权利要求12所述的半导体器件的制作方法,其特征在于,形成所述阶梯连接结构的方法包括:

18.根据权利要求12所述的半导体器件的制作方法,其特征在于,所述穿过所述覆盖层以形成分别连通多个所述多晶硅层的多个接触孔包括:

19.根据权利要求18所述的半导体器件的制作方法,其特征在于,刻蚀清洗所述连接孔时,将所述连接孔底面的所述多晶硅层部分或全部去除。

技术总结

本申请属于半导体技术领域,具体涉及一种半导体器件及其制作方法,半导体器件包括衬底、堆叠结构、覆盖层、金属硅化物层和阶梯连接结构,堆叠结构形成在衬底一侧,堆叠结构包括多个交替堆叠的多晶硅层和隔离层,堆叠结构至少一侧形成阶梯面;覆盖层形成在堆叠结构上并覆盖阶梯面,多个接触孔穿过覆盖层以分别连通多个多晶硅层;金属硅化物层形成在接触孔内且至少位于接触孔的底面;阶梯连接结构填充在接触孔内,阶梯连接结构包括导电层,导电层通过金属硅化物层与多晶硅层连接。至少形成在接触孔底面的金属硅化物层,增大了金属硅化物层和多晶硅层的接触面积,降低了阶梯连接结构和多晶硅层之间的接触阻抗。

技术研发人员:李军辉,杨乾

受保护的技术使用者:深圳市昇维旭技术有限公司

技术研发日:

技术公布日:2024/5/10

- 还没有人留言评论。精彩留言会获得点赞!