MIM电容的制造方法及MIM电容与流程

本发明涉及半导体领域,具体地涉及一种mim电容的制造方法及mim电容。

背景技术:

1、在大规模集成电路中电容的集成结构大致可分为以下四类:mos(metal-oxide-semiconductor)电容、p-n结电容、pip(poly-insulator-poly)电容及mim(metal-insulator-metal)电容。基于衬底和底层器件的mos电容和p-n结电容受晶体管工作电压电流影响较大,在电路中表现不稳定。pip电容的电极板为多晶硅,接触电阻大、寄生电容大,需要热工艺多,对器件影响大。mim电容器件是一种平板电容结构,通过采用金属电极,有效降低了电容器与互连线的接触电阻和寄生电容,因此导电性强。mim电容成为替代传统集成电路电容的新型电容器件。

2、当电容的介质层在偏压条件下工作时,其漏电流会逐渐增加,最后导致击穿,从而使介质层失去绝缘功能。一般情况下,介质层的可靠性测试是在恒定电压下进行的,这种失效模式被称为经时介电层击穿(time dependent dielectric breakdown,简称tddb)。

3、目前,射频、混合或模拟集成电路经常用到大电容值的mim电容,通常是通过减小mim电容介质厚度来得到更大的mim电容值。然而,过薄的电容介质厚度会使mim电容产生比较大的漏电,并导致可靠性中tddb寿命不足的问题,比如,现有的1ff/μm2的mim电容结构中sin厚度为600~700a(埃),但是在芯片设计中为了减少mim的面积而保持电容值不变,需要将介质层sin厚度减薄至300~400a,以将电容密度提高至2ff/μm2。介质层的减薄,带来的坏处是非常容易击穿失效。2ff/μm2的mim,一般使用电压为6v,若失效标准为1000ppm(0.1%)时,其tddb寿命能达到10年,满足消费级电子产品的要求。但是,如果工作电压提高,或者失效标准提高至100ppm甚至10ppm,则mim的tddb寿命会出现数量级的降低,远远达不到10年的要求。

4、现有的mim电容结构通过减薄电介质层厚度来提高mim电容,或者减小布线面积,导致tddb的寿命处在一个瓶颈位置。如果继续提高使用电压,电容则会过早击穿而达不到信赖性的要求;如果应用于工业级或者车规级,失效的标准比例降低,面对tddb寿命20年的苛刻要求,目前的mim电容无法满足。

技术实现思路

1、为了解决现有技术缺陷,本发明提供一种mim电容的制造方法,以提高mim电容的tddb寿命。

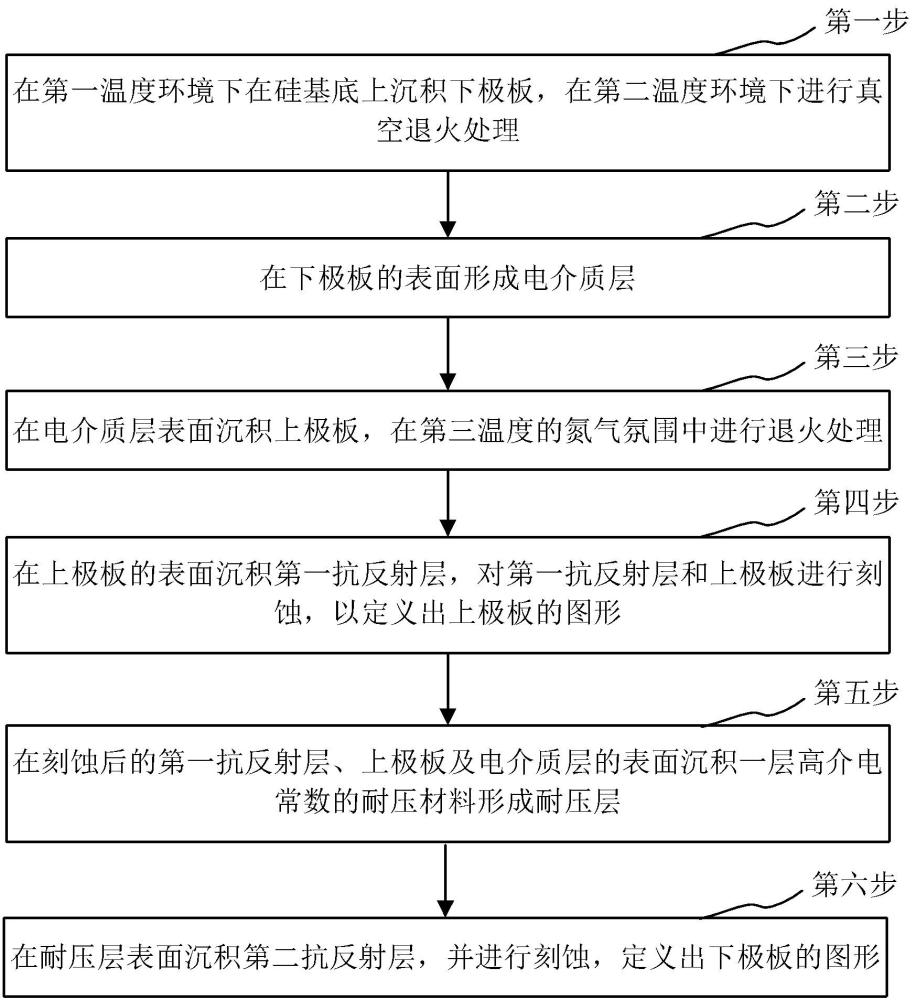

2、本发明一方面提供一种mim电容的制造方法,包括:

3、在第一温度环境下在硅基底上沉积下极板,在第二温度环境下进行真空退火处理;

4、在下极板的表面形成电介质层;

5、在电介质层的表面沉积上极板,在第三温度的氮气氛围中进行退火处理;

6、在上极板的表面沉积第一抗反射层,对第一抗反射层和上极板进行刻蚀,以定义出上极板的图形;

7、在刻蚀后的第一抗反射层、上极板及电介质层的表面沉积一层高介电常数的耐压材料形成耐压层,以填充刻蚀过程中因负载效应导致电介质层产生的凹陷;

8、在耐压层的表面沉积第二抗反射层,并进行刻蚀,以定义出下极板的图形。

9、本发明实施例中,在第一温度环境下在硅基底上沉积下极板,包括:

10、在低于80℃的温度环境下在硅基底表面依次沉积tin、al、tin,形成tin/al/tin的三明治结构,作为下极板;或者

11、在低于80℃的温度环境下在硅基底表面依次沉积tan、al、tan,形成tan/al/tan的三明治结构,作为下极板。

12、本发明实施例中,在第二温度环境下进行真空退火处理,包括:

13、在350~450℃的温度环境下对下极板进行真空退火处理,退火时间不少于30分钟。

14、本发明实施例中,在下极板的表面形成电介质层,包括:

15、将具有下极板的硅基底放入n2、nh3、sih4气体的环境中,在400℃温度条件下,在下极板的表面沉积si3n4,形成电介质层。

16、本发明实施例中,在电介质层的表面沉积上极板,在第三温度的氮气氛围中进行退火处理,包括:

17、在低于100℃的温度环境下,采用溅射工艺在电介质层的表面沉积tin或tan,形成上极板;

18、在350~450℃的氮气氛围中进行退火处理,退火时间不少于30分钟。

19、本发明实施例中,在上极板的表面沉积第一抗反射层,对第一抗反射层和上极板进行刻蚀,包括:

20、在上极板的表面沉积sion,作为第一抗反射层;

21、将电介质层作为刻蚀停止层,对第一抗反射层和上极板进行刻蚀,以定义出上极板的图形。

22、本发明实施例中,在刻蚀后的第一抗反射层、上极板及电介质层的表面沉积一层高介电常数的耐压材料形成耐压层,包括:

23、沉积厚度为100~400埃的si3n4、sicn或sion,形成覆盖第一抗反射层、电介质层以及上极板的侧壁的耐压层。

24、本发明实施例中,在耐压层的表面沉积第二抗反射层并进行刻蚀,包括:

25、在耐压层的表面沉积sion,作为第二抗反射层;

26、对第二抗反射层、耐压层、第一抗反射层、上极板、电介质层以及下极板的两端进行刻蚀,以定义出下极板的图形,使下极板的垂直投影面积大于上极板的垂直投影面积。

27、本发明实施例中,所述方法还包括:

28、从上极板的垂直投影区域对应的第二抗反射层向上极板打孔,形成贯穿第二抗反射层、耐压层和第一抗反射层的过孔连线,作为上极板的过孔连线;

29、从上极板的垂直投影区域之外的第二抗反射层向下极板打孔,形成贯穿第二抗反射层、耐压层和电介质层的过孔连线,作为下极板的过孔连线。

30、本发明另一方面提供一种mim电容,包括:下极板、上极板以及下极板与上极板之间的电介质层,还包括:第一抗反射层、耐压层以及第二抗反射层;

31、所述下极板是在第一温度环境下在硅基底上沉积金属材料,并在第二温度环境下进行真空退火处理后形成的;

32、所述上极板是在所述电介质层的表面沉积金属材料,并在第三温度的氮气氛围中进行退火处理后形成的;

33、所述第一抗反射层形成于上极板的表面;

34、所述耐压层是在刻蚀后的第一抗反射层、上极板及电介质层的表面沉积高介电常数的耐压材料形成的,用于填充刻蚀过程中因负载效应导致电介质层产生的凹陷;

35、所述第二抗反射层形成于耐压层的表面。

36、本发明实施例中,所述下极板为tin/al/tin或tan/al/tan的三明治结构;

37、所述下极板的形成方式具体为:

38、在低于80℃的温度环境下在硅基底表面依次沉积tin、al、tin,形成tin/al/tin的三明治结构;或者

39、在低于80℃的温度环境下在硅基底表面依次沉积tan、al、tan,形成tan/al/tan的三明治结构。

40、本发明实施例中,所述上极板的形成方式具体为:

41、在低于100℃的温度环境下,采用溅射工艺在电介质层的表面沉积tin或tan,在350~450℃的氮气中进行退火处理,退火时间不少于30分钟。

42、本发明实施例中,所述耐压层的形成方式具体为:

43、在刻蚀后的第一抗反射层、上极板及电介质层的表面沉积厚度为100~400埃的si3n4、sicn或sion,形成覆盖第一抗反射层、电介质层以及上极板的侧壁的耐压层。

44、本发明实施例中,下极板的垂直投影面积大于上极板的垂直投影面积。

45、本发明实施例中,mim电容还包括:上极板的过孔连线以及下极板的过孔连线;

46、所述上极板的过孔连线的形成方式为:从上极板的垂直投影区域对应的第二抗反射层向上极板打孔,形成贯穿第二抗反射层、耐压层和第一抗反射层的过孔连线;

47、所述下极板的过孔连线的形成方式为:从上极板的垂直投影区域之外的第二抗反射层向下极板打孔,形成贯穿第二抗反射层、耐压层和电介质层的过孔连线。

48、上述方法,通过低温沉积下极板,能够得到平坦的电极板,使后续形成的电介质层不至于高低不平导致薄弱处早早被电击穿。下极板沉积完成后进行真空退火处理,可以消除应力,提高了薄膜的结晶质量和稳定性。在上极板沉积后进行350至450℃氮气氛围退火处理,可以消除应力,修复介质层和上下极板的界面缺陷,减少漏电的途径,提高耐击穿能力,还提高了si3n4介质层中si-n键含量,提高介电特性,使mim结构本身tddb寿命提高。在上极板刻蚀完成之后,沉积一层高介电常数材料,可以填充刻蚀上极板过程中因负载效应导致的电容边缘凹陷,保护mim电容的四周,可以预防边缘击穿,进一步提高mim电容的tddb寿命。

49、本发明技术方案的其它特征和优点将在下文的具体实施方式部分予以详细说明。

- 还没有人留言评论。精彩留言会获得点赞!