数字隔离器和数字信号传输方法与流程

1.本发明涉及电路技术领域,具体涉及一种数字隔离器和数字信号传输方法。

背景技术:

2.数字隔离器是电子系统中,数字信号和模拟信号进行传递时,使其具有很高的电阻隔离特性,以实现电子系统与用户之间的隔离的一种器件。电路设计人员引入隔离,是为了满足安全要求或者降低接地环路的噪声等。电流隔离确保数据传输不是通过电气连接或泄漏路径,从而避免安全风险。

技术实现要素:

3.有鉴于此,本发明实施例提供一种数字隔离器和数字信号传输方法,以改善数字信号传输过程中的抗干扰能力差的问题。

4.第一方面,本发明实施例提供一种数字隔离器,所述数字隔离器包括:

5.编码电路,用于接收输入数字信号,并将所述输入数字信号的上升沿和下降沿分别编码为不同的编码信号;

6.隔离元件,与所述编码电路连接,用于以电气隔离方式传输所述编码信号;

7.解码电路,与所述隔离元件连接,用于接收所述编码信号并解码输出上升沿和下降沿,以得到与所述输入数字信号一致的输出数字信号;

8.其中,所述上升沿被编码为第一脉冲序列,所述下降沿被编码为第二脉冲序列;

9.所述第一脉冲序列包括多个第一脉冲组,所述第一脉冲组之间的时长间隔为第一时长;所述第二脉冲序列包括多个第二脉冲组,所述第二脉冲组之间的时长间隔为第二时长,所述第一时长和第二时长不同,所述第一脉冲组和第二脉冲组包括至少一个脉冲。

10.进一步地,所述编码电路用于在检测到所述上升沿或下降沿后开始输出所述编码信号;

11.所述解码电路用于在接收到第一脉冲序列后控制输出上升沿,以及在接收到第二脉冲序列后控制输出下降沿。

12.进一步地,所述第一脉冲序列中第一脉冲组的数量与第二脉冲序列中第二脉冲组的数量相同。

13.进一步地,所述第一脉冲序列包括多个相同的第一脉冲组,以及所述第二脉冲序列包括多个相同的第二脉冲组。

14.进一步地,所述第一脉冲组和第二脉冲组在脉冲的数量、幅值、宽度、极性和排列方式中的至少一项不同。

15.进一步地,所述第一脉冲组和第二脉冲组中脉冲的数量相同。

16.进一步地,所述第一脉冲组包括多个相同的脉冲,以及所述第二脉冲组包括多个相同的脉冲。

17.进一步地,所述第一脉冲组和第二脉冲组均包括一个脉冲。

18.进一步地,所述第一脉冲组的脉冲或与所述第二脉冲组的脉冲在脉冲的极性、宽度和幅值中的至少一项不同。

19.进一步地,所述第一脉冲组包括多个脉冲,所述多个脉冲的极性、宽度和幅值中的至少一项不同。

20.进一步地,所述第二脉冲组包括多个脉冲,所述多个脉冲的极性、宽度和幅值中的至少一项不同。

21.第二方面,本发明实施例提供一种数字信号传输方法,所述方法包括:

22.接收输入数字信号;

23.将所述输入数字信号的上升沿和下降沿分别编码为不同的编码信号;

24.以电气隔离方式传输所述编码信号;

25.接收所述编码信号并解码输出上升沿和下降沿,以得到与所述输入数字信号一致的输出数字信号;

26.其中,所述上升沿被编码为第一脉冲序列,所述下降沿被编码为第二脉冲序列;

27.所述第一脉冲序列包括多个第一脉冲组,所述第一脉冲组之间的时长间隔为第一时长;所述第二脉冲序列包括多个第二脉冲组,所述第二脉冲组之间的时长间隔为第二时长,所述第一时长和第二时长不同,所述第一脉冲组和第二脉冲组包括至少一个脉冲。

28.进一步地,所述将所述输入数字信号的上升沿和下降沿分别编码为不同的编码信号包括:在检测到所述上升沿或下降沿后开始输出所述编码信号;

29.所述接收所述编码信号并解码输出上升沿和下降沿包括:在接收到第一脉冲序列后控制输出上升沿,以及在接收到第二脉冲序列后控制输出下降沿。

30.本发明实施例的技术方案通过编码电路将输入数字信号的上升沿和下降沿分别编码为第一脉冲序列和第二脉冲序列,通过包括时间间隔为第一时长的多个第一脉冲组表征第一脉冲序列,时间间隔为第二时长的多个第二脉冲组表征第二脉冲序列,由于编码信号中加入了更多的信息,因此,可以精确地通过隔离元件传递上升沿和下降沿对应的编码信息,在实现输入数字信号的编码和传输的同时,提高了数字隔离器的抗干扰性能。

附图说明

31.通过以下参照附图对本发明实施例的描述,本发明的上述以及其它目的、特征和优点将更为清楚,在附图中:

32.图1是本发明实施例的数字隔离器的示意图;

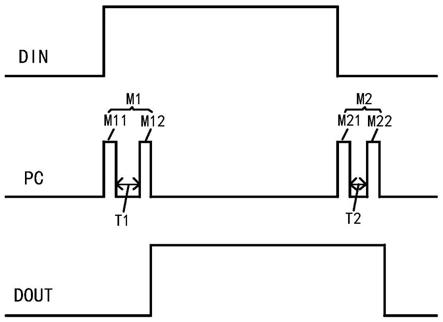

33.图2是相关技术的一种数字隔离器的工作波形图;

34.图3是本实施例的一个可选实现方式的数字隔离器的工作波形图;

35.图4是本实施例的另一个可选实现方式的数字隔离器的工作波形图;

36.图5是本实施例的另一个可选实现方式的数字隔离器的工作波形图;

37.图6是本实施例的另一个可选实现方式的数字隔离器的工作波形图;

38.图7是本发明实施例的数字信号传输方法的流程图。

具体实施方式

39.以下基于实施例对本发明进行描述,但是本发明并不仅仅限于这些实施例。在下

文对本发明的细节描述中,详尽描述了一些特定的细节部分。对本领域技术人员来说没有这些细节部分的描述也可以完全理解本发明。为了避免混淆本发明的实质,公知的方法、过程、流程、元件和电路并没有详细叙述。

40.此外,本领域普通技术人员应当理解,在此提供的附图都是为了说明的目的,并且附图不一定是按比例绘制的。

41.同时,除非上下文明确要求,否则在说明书的“包括”、“包含”等类似词语应当解释为包含的含义而不是排他或穷举的含义;也就是说,是“包括但不限于”的含义。

42.在本发明的描述中,需要理解的是,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性。此外,在本发明的描述中,除非另有说明,“多个”的含义是两个或两个以上。

43.图1是本发明实施例的数字隔离器的示意图。如图1所示,本发明实施例的数字隔离器包括编码电路1、隔离元件2和解码电路3。其中,编码电路1用于接收输入数字信号,并将输入数字信号的上升沿和下降沿分别编码为不同的编码信号。隔离元件2与编码电路1连接,用于以电气隔离方式传输编码信号。解码电路3与隔离元件2连接,用于接收编码信号并解码输出上升沿和下降沿,以得到与输入数字信号一致的输出数字信号。由此,实现输入数字信号的编码和传输。

44.进一步地,在本实施例中,编码电路1在检测到上升沿或下降沿后开始输出编码信号。具体地,编码电路1将输入数字信号din的上升沿编码为第一脉冲序列,将下降沿编码为第二脉冲序列。其中,第一脉冲序列包括多个第一脉冲组,多个第一脉冲组之间的时间间隔为第一时长。第二脉冲序列包括多个第二脉冲组,多个第二脉冲组之间的时间间隔为第二时长,第二时长与第一时长不同,且第一脉冲组和第二脉冲组均包括至少一个脉冲,既可以是单个脉冲,也可以是由多个连续脉冲组成的脉冲序列。由此,通过将脉冲按照一定方式组成脉冲组,再按照预设的时间间隔排列多个脉冲组形成对应的脉冲序列,并通过不同的脉冲序列分别表征输入数字信号的上升沿和下降沿,使得编码信号中同时包括脉冲信息、脉冲组信息以及脉冲序列信息,信息量更加丰富,能够提高编码信号的抗干扰能力。

45.同时,由于第一脉冲序列和第二脉冲序列之间存在差异,隔离元件2采用电气隔离的方式(也即输入端和输出端不共地)将脉冲序列(也即,经过对于上升沿位置和下降沿位置的编码信号)传输至解码电路3。解码电路3接收到第一脉冲序列后控制输出上升沿,并在接收到第二脉冲序列后控制输出下降沿。

46.具体地,由于第一脉冲序列和第二脉冲序列具有不同的时间间隔,且第一脉冲序列和第二脉冲序列对应的时间间隔均是确定的,解码电路在编码信号中检测到脉冲序列的时间间隔为第一时长时,确定检测到第一脉冲序列,并在输出端输出上升沿。在编码信号中检测到脉冲序列的时间间隔为第二时长时,确定检测到第二脉冲序列,并在输出端输出下降沿。由此,解码电路可以根据脉冲序列对应的时间间隔准确输出上升沿和下降沿,进而输出与输入数字信号波形一致的输出数字信号,并提高数字信号传输过程中的抗干扰能力。

47.可选地,本实施例中的编码电路1和解码电路3可以通过边沿检测电路、信号调制器和载波发生器来构成。隔离元件2可以采用电容或微型变压器。并且,当编码电路输出的是单路脉冲信号时,对应地,采用单端传输式的隔离元件。当编码电路输出的是双路差分信号时,对应地,采用差分传输式的隔离元件,以进一步提高脉冲序列传输过程中的抗干扰能

力和数字隔离器的抗干扰性能。

48.本发明实施例的技术方案通过编码电路将输入数字信号的上升沿和下降沿分别编码为第一脉冲序列和第二脉冲序列,通过包括时间间隔为第一时长的多个第一脉冲组表征第一脉冲序列,时间间隔为第二时长的多个第二脉冲组表征第二脉冲序列,使得编码信号中加入了更多的关联信息,提高了编码信息的抗干扰能力。同时,通过隔离元件传递上升沿和下降沿对应的编码信息,经由解码电路根据编码信号中的脉冲信号的时间间隔确定输出上升沿和下降沿,在实现输入数字信号的编码和传输的同时,提高编码信号的抗干扰能力和数字隔离器的抗干扰性能。

49.图2是相关技术的一种数字隔离器的工作波形图。如图2所示,在该相关技术的数字隔离器中,将输入数字信号din的上升沿对应编码为6个连续的脉冲,下降沿对应编码为4个连续的脉冲。由此,在解码端,通过对预定周期内的连续脉冲数量计数就可以识别上升沿和下降沿,并得到输出数字信号dout。但是,采用这种编码方式的数字隔离器抗干扰能力较差,如果传递过程中出现电磁干扰,导致连续脉冲的数量变化,则可能导致解码端的解码错误。

50.图3是本实施例的一个可选实现方式的数字隔离器的工作波形图。如图3所示,在本实现方式中,和输入数字信号din的上升沿对应的第一脉冲序列m1包括2个第一脉冲组,分别为第一脉冲组m11和第一脉冲组m12。其中,第一脉冲组m11和第一脉冲组m12均包括一个脉冲。第一脉冲组m11和第一脉冲m12之间的时间间隔为t1。和输入数字信号din的下降沿对应的第二脉冲序列m2包括2个第二脉冲组,分别为第二脉冲组m21和第二脉冲组m22,其中,第二脉冲组m21和第二脉冲组m22均包括一个脉冲,第二脉冲组m21和第二脉冲组m22之间的时间间隔为t2。由此,通过采用具有不同时间间隔的脉冲组来组成脉冲序列,使得编码信号中的信息量更加丰富,进而提高编码信号的抗干扰能力。

51.在图3中,编码电路的输出信号为编码信号pc。解码电路通过隔离元件接收编码信号pc,在编码信号pc中检测到第一脉冲序列m1时在输出端输出上升沿,在编码信号pc中检测到第二脉冲序列m2时在输出端输出下降沿。

52.进一步地,由于第一脉冲序列和第二脉冲序列具有不同的时间间隔,且第一脉冲序列和第二脉冲序列对应的时间间隔均是确定的,解码电路在编码信号pc中检测到脉冲序列的时间间隔为t1时,确定检测到第一脉冲序列m1,并在输出端输出上升沿。在编码信号pc中检测到脉冲序列的时间间隔为t2时,确定检测到第二脉冲序列m2,并在输出端输出下降沿。由此,解码电路可以根据脉冲序列对应的时间间隔准确输出上升沿和下降沿,进而输出与输入数字信号din波形一致的输出数字信号dout,并提高数字信号传输过程中的抗干扰能力。

53.可选地,为方便编码信号的输出以及上升沿和下降沿的检测,本实施例中的第一脉冲序列中第一脉冲组的数量与第二脉冲序列中第二脉冲组的数量相同。

54.应理解,本实施例中的第一脉冲组和第二脉冲组的数量不限于2个,还可以是两个以上。第一脉冲组和第二脉冲组的数量和类型都可以根据实际需要进行设置,设置的较多,较复杂,则电路的复杂程度相对会提升,抗干扰性能进一步得到提升。

55.进一步地,第一脉冲序列中包括多个相同的第一脉冲组,第二脉冲序列中包括多个相同的第二脉冲组。具体地,第一脉冲序列中的各第一脉冲组也可以与第二脉冲序列中

的各第二脉冲组采用相同形式。当各第一脉冲组采用相同形式,各第二脉冲组采用相同形式,以及各第一脉冲组和各第二脉冲组采用相同形式时,各第一脉冲组和第二脉冲组中的脉冲的数量、极性、宽度、幅值和排列方式均是相同的。由此,通过设置相同的脉冲组,为编码信号的输出以及上升沿下降沿的检测提供方便。

56.如图3所示,在本实现方式中,和输入数字信号的上升沿对应的第一脉冲序列m1包括两个相同的第一脉冲组,分别为第一脉冲组m11和第一脉冲组m12,第一脉冲组m11和第一脉冲组m12之间的时间间隔为t1。同时,和输入数字信号的下降沿对应的第二脉冲序列m2包括两个相同的第二脉冲组,分别为第二脉冲组m21和第二脉冲组m22,第二脉冲组m21和第二脉冲组m22之间的时间间隔为t2。其中,第一脉冲组m11、第一脉冲组m12、第二脉冲组m21和第二脉冲组m22均采用相同形式。由此,通过上述设置方式,在提高抗干扰性能的同时,通过设置相同形式的第一脉冲组和相同形式的第二脉冲组,有利于减少信号传输的延时时间,提升数字隔离器的整体使用性能。

57.具体地,当第一脉冲序列包括多个相同的第一脉冲组以及第二脉冲序列包括多个相同的第二脉冲组时,第一脉冲组和第二脉冲组可以采用相同的形式,也可以采用不同的形式。当第一脉冲组和第二脉冲组采用不同形式时,第一脉冲组和第二脉冲组在脉冲的数量、宽度、极性、幅值和排列方式中的至少一项不同。

58.进一步地,在本实施例中,第一脉冲序列可以包括多个不同第一脉冲组,第二脉冲序列可以包括多个不同的第二脉冲组。其中,“多个不同”表征的是存在至少两个不同的第一脉冲组或第二脉冲组。当存在不同的第一脉冲组或第二脉冲组时,各第一脉冲组中的脉冲在脉冲的数量、宽度、极性、幅值和排列方式中的至少一项不同,各第二脉冲组中的脉冲在脉冲的数量、宽度、极性、幅值和排列方式中的至少一项不同。

59.图4是本实施例的另一个可选实现方式的数字隔离器的工作波形图。如图4所示,在本实现方式中,和输入数字信号din的上升沿对应的第一脉冲序列m1包括两个不同的第一脉冲组,分别为第一脉冲组m11和第一脉冲组m12,第一脉冲组m11和第一脉冲组m12之间的时间间隔为t1。其中,第一脉冲组m11和第一脉冲组m12中的脉冲数量均为1个,第一脉冲组m11和第一脉冲组m12中的脉冲宽度相同,极性和幅值均不同。同时,和输入数字信号din的下降沿对应的第二脉冲序列m2包括两个不同的第二脉冲组,分别为第二脉冲组m21和第二脉冲组m22,第二脉冲组m21和第二脉冲组m22之间的时间间隔为t2。其中,第二脉冲组m21和第二脉冲组m22中的脉冲数量均为1个,第二脉冲组m21和第二脉冲组m22中的脉冲极性相同,宽度和幅值均不同。由此,通过具有不同脉冲宽度、极性和幅值属性的脉冲形成对应的脉冲组,通过将不同的脉冲组按照预设的时间间隔以预定排布方式设置,形成对应的脉冲序列,并通过不同的脉冲序列分别表示输入数字信号的上升沿和下降沿,由于第一脉冲序列和第二脉冲序列中均包括对应脉冲极性、宽度和幅值的属性信息以及脉冲组的排列信息和时间间隔信息等,使得编码信号中的信息量更加丰富,进而提高编码信号的抗干扰能力。

60.进一步地,在图4中,由于第一脉冲序列m1和第二脉冲序列m2具有不同的时间间隔t1和t2,且第一脉冲序列m1和第二脉冲序列m2对应的时间间隔t1和t2均是确定的,解码电路在编码信号pc中检测到脉冲序列内脉冲组的时间间隔为t1时,确定检测到第一脉冲序列m1,并在输出端输出上升沿。在编码信号pc中检测到脉冲序列内脉冲组的时间间隔为t2时,确定检测到第二脉冲序列m2,并在输出端输出下降沿。由此,解码电路可以根据脉冲序列对

应的时间间隔准确输出上升沿和下降沿,进而输出与输入数字信号din波形一致的输出数字信号dout,并提高数字信号传输过程中的抗干扰能力。

61.可选地,为方便编码信号的输出以及上升沿和下降沿的检测,本实施例中第一脉冲组和第二脉冲组中脉冲的数量相同。

62.应理解,第一脉冲组和第二脉冲组中脉冲的数量可以为一个,也可以为多个。第一脉冲组和第二脉冲组中脉冲的数量可以根据实际需要进行设置,脉冲数量设置的较多,则电路的复杂程度会相对提升,抗干扰能力也会进一步得到提升。

63.进一步地,第一脉冲组包括多个相同的脉冲,以及第二脉冲组包括多个相同的脉冲。当第一脉冲组和第二脉冲组均包括多个相同的脉冲时,各脉冲组中的各脉冲采用相同的形式时,各脉冲的极性、宽度和幅值等属性均相同。由此,通过设置较多数量的脉冲,进一步丰富脉冲序列中的编码信息,提升数字信号传输过程中的抗干扰能力。并且,通过将第一脉冲组中的脉冲以及第二脉冲组中的脉冲设置为相同形式,在提高抗干扰能力的同时,有利于降低电路的整体复杂度,减少信号传输的延时时间,提高数字隔离器的整体性能。

64.图5是本实施例的另一个可选实现方式的数字隔离器的工作波形图。如图5所示,在本实现方式中,和输入数字信号din的上升沿对应的第一脉冲序列m1包括两个第一脉冲组,分别为第一脉冲组m11和第一脉冲组m12。其中,第一脉冲组m11和第一脉冲m12之间的时间间隔为t1,第一脉冲组m11和第一脉冲组m12采用相同形式的脉冲序列,均包括三个脉冲,且各脉冲的极性、宽度、幅值和排列方式均相同。和输入数字信号din的下降沿对应的第二脉冲序列m2包括两个第二脉冲组,分别为第二脉冲组m21和第二脉冲组m22。其中,第二脉冲组m21和第二脉冲组m22之间的时间间隔为t2,第二脉冲组m21和第二脉冲组m22采用相同形式的脉冲序列,均包括三个脉冲,且各脉冲的极性、宽度、幅值和排列方式均相同。同时,第一脉冲组m11和第二脉冲组m21中的脉冲在脉冲幅值上是不同的,但脉冲的宽度和极性是相同的。由此,通过具有相同脉冲极性、宽度和幅值的三个脉冲形成的脉冲序列构成对应的脉冲组,通过将相同的脉冲组按照预设的时间间隔进行排列形成对应的第一脉冲序列和第二脉冲序列,并通过不同的脉冲序列分别表示输入数字信号的上升沿和下降沿,由于第一脉冲序列和第二脉冲序列中均包括对应脉冲的极性、宽度和幅值的属性信息以及脉冲组的排列信息和时间间隔信息等,使得编码信号中的信息量更加丰富,进而提高编码信号的抗干扰能力。并且,通过设置相同形式的第一脉冲组和相同形式的第二脉冲组,在提高抗干扰性能的同时,有利于减少信号传输的延时时间,提升数字隔离器的整体使用性能。

65.在图5中,编码电路的输出信号为编码信号pc。解码电路通过隔离元件接收编码信号pc,在编码信号pc中检测到第一脉冲序列m1时在输出端输出上升沿,在编码信号pc中检测到第二脉冲序列m2时在输出端输出下降沿。

66.进一步地,解码电路在编码信号pc中检测到脉冲序列内脉冲组的时间间隔为t1时,确定检测到第一脉冲序列m1,并在输出端输出上升沿。在编码信号pc中检测到脉冲序列内脉冲组的时间间隔为t2时,确定检测到第二脉冲序列m2,并在输出端输出下降沿。由此,解码电路可以根据脉冲序列对应的时间间隔准确输出上升沿和下降沿,进而输出与输入数字信号din波形一致的输出数字信号dout,并提高数字信号传输过程中的抗干扰能力。

67.具体地,在第一脉冲组包括多个相同的脉冲,以及第二脉冲组包括相同数量的多个相同的脉冲时,第一脉冲组中的脉冲与第二脉冲组中的脉冲可以是相同的,也可以是不

同的。当第一脉冲组与第二脉冲组中的脉冲相同时,脉冲组中相互对应的各脉冲的极性、宽度和幅值等属性均相同。当第一脉冲组与第二脉冲组中的脉冲不同时,脉冲组中相互对应的各脉冲的极性、宽度和幅值等属性中的至少一项不同。其中,相互对应的脉冲在各自所属的脉冲序列中的出现顺序是相同的。

68.进一步地,第一脉冲组包括多个不同的脉冲,第一脉冲组中的各脉冲采用不同的形式时,第一脉冲组中的多个脉冲对应的极性、宽度和幅值中的至少一项不同。进一步地,第二脉冲组包括多个不同的脉冲,第二脉冲组中的各脉冲采用不同的形式时,第二脉冲组中的多个脉冲对应的极性、宽度和幅值中的至少一项不同。其中,“多个不同”指的是存在至少两个不同的脉冲。

69.图6是本实施例的另一个可选实现方式的数字隔离器的工作波形图。如图6所示,在本实现方式中,和输入数字信号din的上升沿对应的第一脉冲序列m1包括两个不同的第一脉冲组,分别为第一脉冲组m11和第一脉冲组m12。其中,第一脉冲组m11和第一脉冲组m12之间的时间间隔为t1。第一脉冲组m11由三个脉冲组成,第一脉冲组m11中的脉冲的极性和宽度相同,但幅值不同。第一脉冲组m12与第一脉冲组m11中的脉冲数量相同,并且第一脉冲组m12中的三个脉冲的脉冲极性相同,但幅值不同,第一脉冲组m12中的最后一个脉冲的宽度也与前面两个脉冲不同。

70.同时,和输入数字信号din的下降沿对应的第二脉冲序列m2包括两个不同的第二脉冲组,分别为第二脉冲组m21和第二脉冲组m22。其中,第二脉冲组m21和第二脉冲组m22之间的时间间隔为t2,两个第二脉冲组均包括三个不同的脉冲。第二脉冲组m21中的三个脉冲的宽度相同,但幅值均不相同。并且,第二脉冲组m21中的第一个脉冲为负脉冲,后两个脉冲为正脉冲。也即,第二脉冲组m21中的脉冲的极性是不同的。第二脉冲组m22中的三个脉冲的宽度和极性相同,但脉冲的幅值均不相同。由此,通过上述设置方式,使得编码信号中的信息量更加丰富,进而提高编码信号的抗干扰能力。

71.进一步地,在图6中,由于第一脉冲序列m1和第二脉冲序列m2具有不同的时间间隔t1和t2,且第一脉冲序列m1和第二脉冲序列m2对应的时间间隔t1和t2均是确定的,解码电路在编码信号pc中检测到脉冲序列内脉冲组的时间间隔为t1时,确定检测到第一脉冲序列m1,并在输出端输出上升沿。在编码信号pc中检测到脉冲序列内脉冲组的时间间隔为t2时,确定检测到第二脉冲序列m2,并在输出端输出下降沿。由此,解码电路可以根据脉冲序列对应的时间间隔准确输出上升沿和下降沿,进而输出与输入数字信号din波形一致的输出数字信号dout,并提高数字信号传输过程中的抗干扰能力。

72.图7是本发明实施例的数字信号传输方法的流程图。如图7所示,本实施例的数字信号传输方法包括以下步骤:

73.在步骤s100,接收输入数字信号。

74.本实施例中,通过编码电路的输入端接收输入数字信号。

75.在步骤s200,将输入数字信号的上升沿和下降沿分别编码为不同的编码信号。

76.本实施例中,通过编码电路对输入数字信号的上升沿和下降沿进行编码。编码电路可以通过边沿检测电路、信号调制器和载波发生器来构成。编码电路将输入数字信号的上升沿和下降沿分别编码为不同的编码信号包括:在检测到上升沿或下降沿后开始输出编码信号。编码电路在输出编码信号时,可以输出单路脉冲信号或双路差分信号。

77.进一步地,本实施例中的上升沿被编码为第一脉冲序列,下降沿被编码为第二脉冲序列。其中,第一脉冲序列包括多个第一脉冲组,第一脉冲组之间的时长间隔为第一时长。第二脉冲序列包括多个第二脉冲组,第二脉冲组之间的时长间隔为第二时长,第一时长和第二时长不同,第一脉冲组和第二脉冲组包括至少一个脉冲。

78.具体地,第一脉冲序列和第二脉冲序列的设置方式可以采用前述脉冲序列设置方式中的任意一种,此处不再赘述。

79.在步骤s300,以电气隔离方式传输编码信号。

80.本实施例中,通过隔离元件以电气隔离方式传输编码信号。隔离元件可以采用电容或微型变压器。隔离元件可以采用电容或微型变压器。当编码电路输出的是单路脉冲信号时,采用单端传输式的隔离元件。当编码电路输出的是双路差分信号时,采用差分传输式的隔离元件,以进一步提高脉冲序列传输过程中的抗干扰能力和数字隔离器的抗干扰性能。

81.在步骤s400,接收编码信号并解码输出上升沿和下降沿,以得到与输入数字信号一致的输出数字信号。

82.本实施例中,通过解码电路接收编码信号并解码输出上升沿和下降沿。解码电路可以通过边沿检测电路、信号调制器和载波发生器来构成。

83.进一步地,解码电路接收编码信号并解码输出上升沿和下降沿包括:在接收到第一脉冲序列后控制输出上升沿,以及在接收到第二脉冲序列后控制输出下降沿。

84.进一步地,由于第一脉冲序列和第二脉冲序列具有不同的时间间隔,且第一脉冲序列和第二脉冲序列对应的时间间隔均是确定的,解码电路在编码信号中检测到脉冲序列的时间间隔为第一时长时,确定检测到第一脉冲序列,并在输出端输出上升沿。在编码信号中检测到脉冲序列的时间间隔为第二时长时,确定检测到第二脉冲序列,并在输出端输出下降沿。由此,解码电路可以根据脉冲序列对应的时间间隔准确输出上升沿和下降沿,进而输出与输入数字信号波形一致的输出数字信号,并提高数字信号传输过程中的抗干扰能力。

85.本实施例的技术方案通过对于输入数字信号的上升沿和下降沿进行冗余编码,通过时间间隔为第一时长的第一脉冲组组成的第一脉冲序列和时间间隔为第二时长的第二脉冲组组成的第二脉冲序列分别表征上升沿和下降沿。由于编码信息中加入了更多的信息,因此,可以精确地通过隔离元件传递上升沿和下降沿信息,提高抗干扰性能。同时,通过解码电路根据脉冲序列对应的时间间隔准确输出上升沿和下降沿,进而输出与输入数字信号波形一致的输出数字信号,进一步提高数字信号传输过程中的抗干扰能力。

86.以上所述仅为本发明的优选实施例,并不用于限制本发明,对于本领域技术人员而言,本发明可以有各种改动和变化。凡在本发明的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1