具有字线结构以避免短路的半导体存储器装置及其制造方法与流程

大体来说,本申请涉及半导体存储器装置。特定来说,本申请涉及具有字线结构以避免短路的半导体存储器装置及其制造方法。

背景技术:

1、对于半导体存储器装置,正开发较精细的几何形状以增加例如动态随机存取存储器(dram)等半导体存储器装置的数据存储容量。举例来说,例如dram的字线等布线的重复间距的大小减小,且字线之间的距离也减小。然而,如果在形成待连接到字线的接触电极时发生字线未对准,则接触电极可能断开或可能变为短接到邻近的字线。

技术实现思路

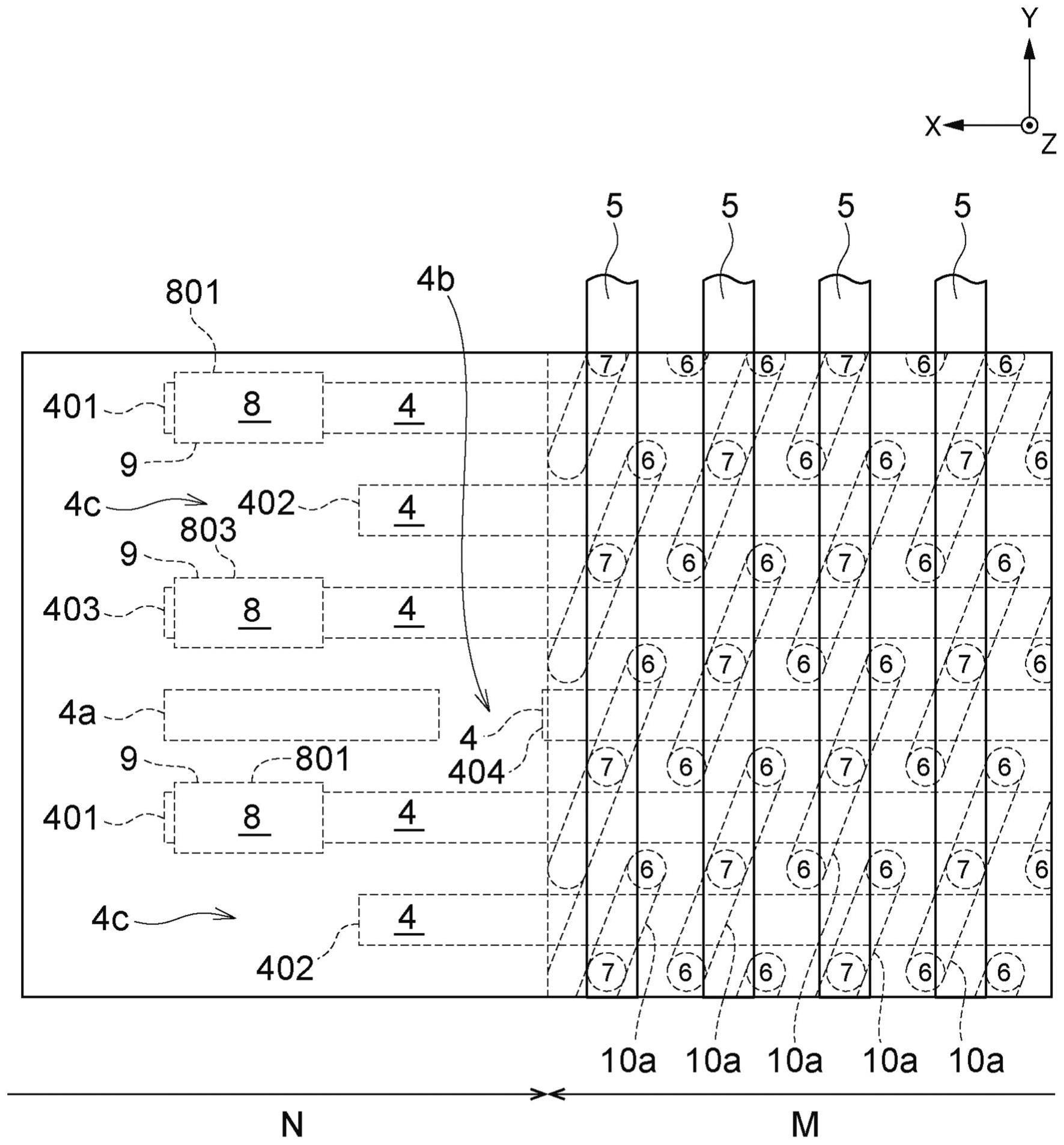

1、在一个方面中,本申请提供一种设备,所述设备包括:衬底;存储器单元区,其提供于所述衬底上方;外围区,其提供于所述衬底上方且邻近于所述存储器单元区;以及第一、第二、第三、第四和第五字线,其各自以数值次序跨所述存储器单元区和所述外围区平行地延伸;其中所述第二字线的边料插入于所述第一和第三字线的边缘部分之间;且其中所述第四字线没有边料插入于所述第三和第五字线的边缘部分之间。

2、在另一方面中,本申请提供一种设备,所述设备包括:衬底;存储器单元区,其提供于所述衬底上方;外围区,其提供于所述衬底上方,所述外围区邻近于所述存储器单元区而提供;以及多个字线,其通过重复包含第一、第二、第三和第四字线的群组而布置,所述多个字线中的每一个跨所述存储器单元区和所述外围区延伸;其中所述第一和所述第三字线邻近地提供在所述第二和第四字线之间;其中所述外围区中的所述第一和所述第三字线的第一长度长于所述外围区中的所述第二字线的第二长度;且其中所述外围区中的所述第二字线的所述第二长度长于所述外围区中的所述第四字线的第三长度。

3、在另一方面中,本申请提供一种制造设置于衬底上的设备的方法,所述衬底包含存储器单元区和邻近于所述存储器单元区提供的外围区,所述方法包括;在所述衬底上方在所述存储器单元区和所述外围区中形成第一掩模,所述第一掩模包含以数值次序布置的线形第一、第二和第三缝隙;在所述外围区中形成第二掩模,所述第二掩模包含提供在所述第一掩模的所述第一缝隙的边缘部分上方的第一部分,以及提供在与所述第一掩模的所述第三缝隙的边缘部分不同的部分上方的第二部分;以及用所述第一掩模和所述第二掩模蚀刻所述衬底以便在所述衬底上形成沟槽。

技术特征:

1.一种设备,其包括:

2.根据权利要求1所述的设备,其进一步包括分别在所述第一、第三和第五字线的所述边缘部分上的第一、第二和第三接触件。

3.根据权利要求1所述的设备,其进一步包括:

4.根据权利要求1所述的设备,其中所述第二字线的所述边料为电浮动的。

5.根据权利要求3所述的设备,其中所述第五字线的额外边料为电浮动的,且所述第三字线没有边料为电浮动的。

6.根据权利要求1所述的设备,其中所述存储器单元区包含多个存储器单元。

7.根据权利要求6所述的设备,其中所述第一、第二、第三、第四和第五字线耦合到所述多个存储器单元中的相应存储器单元以控制对所述多个存储器单元中的所述相应存储器单元的存取。

8.根据权利要求1所述的设备,其中所述第一、第二、第三、第四和第五字线中的每一个包含嵌入于所述衬底的沟槽中的导电材料。

9.一种设备,其包括:

10.根据权利要求9所述的设备,其进一步包括分别连接到所述外围区中的所述第一和第三字线的边缘部分的第一和第二接触件。

11.根据权利要求9所述的设备,

12.根据权利要求9所述的设备,其中所述第一、第二、第三和第四字线分别耦合到所述多个存储器单元中的相应存储器单元以控制对所述多个存储器单元中的所述相应存储器单元的存取。

13.根据权利要求9所述的设备,其中所述第一、第二、第三和第四字线中的每一个嵌入于设置于所述衬底上的沟槽中。

14.一种制造设置于衬底上的设备的方法,所述衬底包含存储器单元区和邻近于所述存储器单元区提供的外围区,所述方法包括:

15.根据权利要求14所述的方法,其中没有沟槽形成于所述衬底上在所述第二掩模的所述第一部分和所述第二部分下方。

16.根据权利要求14所述的方法,其中通过光刻技术使包含所述第一部分和所述第二部分的所述第二掩模图案化。

17.根据权利要求14所述的方法,其中通过所述蚀刻在所述衬底上在所述外围区中在所述第二缝隙下方形成第二沟槽。

18.根据权利要求17所述的方法,其中通过所述蚀刻在所述衬底上在所述外围区中在所述第一缝隙下方形成短于所述第二沟槽的第一沟槽。

19.根据权利要求18所述的方法,其中通过所述蚀刻在所述衬底上在所述外围区中在所述第三缝隙下方形成短于所述第一沟槽的第三沟槽和岛状沟槽。

20.根据权利要求19所述的方法,其进一步包括将导电材料嵌入在所述第一、第二和第三沟槽以及所述岛状沟槽的每一下部部分中。

技术总结

本申请涉及一种具有字线结构以避免短路的半导体存储器装置及其制造方法。一种设备包含衬底、提供在所述衬底上方的存储器单元区、提供在所述衬底上方且邻近于所述存储器单元区的外围区,以及第一、第二、第三、第四和第五字线,每一字线以数值次序跨所述存储器单元区和所述外围区平行地延伸。所述第二字线的边料插入于所述第一和第三字线的边缘部分之间,且所述第四字线没有边料插入于所述第三和第五字线的边缘部分之间。

技术研发人员:佐佐木隆,铃木淳也

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!