忆阻器及其制备方法与流程

1.本发明涉及忆阻器器件领域,具体涉及一种忆阻器及其制备方法。

背景技术:

2.电阻、电容与电感是三种广为人知的无源电路元件。蔡少棠教授于1971年由对称性论证推断出,应该存在第四种电路基本元件,他称之为忆阻器。电荷或磁通流经忆阻器时,忆阻器的电阻值会发生变化,并且忆阻器会将这种电阻值的变化记录下来。2008年,惠普公司首次在实验室里通过一个“导体-绝缘体-导体”的结构实现了忆阻器的构建。在纳米尺度系统中,固态电子和离子输运在外部偏置电压下耦合,忆阻就会自然产生。

3.目前,存在多种类型的忆阻器结构,但现有忆阻器依然普遍存在开关比低的问题。

技术实现要素:

4.为实现上述目的,本发明提供一种忆阻器,包括:

5.衬底;

6.所述衬底表面具有第一金属电极和第二金属电极,所述第一金属电极和第二金属电极在同一直线上且相隔离;

7.所述第一金属电极和第二金属电极表面具有碲线,所述碲线表面具有氧化碲薄层,所述碲线将所述第一金属电极和第二金属电极相连接。

8.可选的,所述第一金属电极和第二金属电极材料为惰性金属电极。

9.可选的,所述第一金属电极和第二金属电极材料为金。

10.可选的,所述碲线的直径范围为0.1微米~2微米,所述氧化碲薄层的厚度范围为1纳米~5纳米。

11.可选的,所述忆阻器的设置电压与恢复电压均小于5v。

12.本发明还提供一种忆阻器的制备方法,包括:

13.提供衬底;

14.在所述衬底表面形成第一金属电极和第二金属电极,所述第一金属电极和第二金属电极在同一直线上且相隔离;

15.转移碲线到所述第一金属电极和第二电表面,所述碲线表面具有氧化碲薄层,所述碲线将所述第一金属电极和第二金属电极相连接。

16.可选的,所述第一金属电极和第二金属电极通过热蒸镀工艺进行制备。

17.可选的,所述碲线采用物理气相沉积的方法制备,所述碲线的制备方法具体包括:取一定质量的碲粉平铺于石英舟内;选用单抛氧化硅片,将所述单抛氧化硅片的二氧化硅面朝向石英舟,并覆盖在石英舟上;将覆盖有单抛氧化硅片的石英舟送入管式炉中,将管式炉内部抽为真空,再缓缓通入氢气和氩气的混合气体,使得管式炉内部的压强回到标准大气压;控制生长温度和生长时间,进行碲线生长;碲线生长结束后,等待管式炉自然冷却至室温,再将单抛氧化硅片从管式炉中取出,此时的单抛氧化硅片上具有生长的碲线,最终完

成碲线的生长,所述碲粉的质量范围为200毫克~300毫克,碲粉的纯度为99.99%;使用真空泵将管式炉内部抽为真空,然后向管式炉内通入h2和ar混合气体,流速范围为70~90标况毫升每分,所述碲线的生长温度的范围为510摄氏度~530摄氏度,所述碲线的生长时间的范围为10分钟~20分钟。

18.可选的,所述碲线放置在空气中1~7天,使得所述碲线表面形成氧化碲薄层。

19.可选的,所述氧化碲薄层的厚度范围为1纳米~5纳米。

20.综上所述,本发明的优点及有益效果为:

21.本发明提供一种忆阻器及其制备方法,包括衬底,位于衬底表面的第一金属电极和第二金属电极,以及位于所述第一金属电极和第二金属电极表面的碲线,所述碲线表面具有氧化碲薄层。所述氧化碲薄层附着在碲线上,使得所述忆阻器具有良好的忆阻性能。

22.由于所述碲线表面具有氧化碲薄层,具有良好的忆阻性能,但如果先在衬底表面形成碲线,再在所述碲线的两侧形成第一金属电极和第二金属电极,形成金属电极的工艺(包括热蒸镀工艺、或其他)会使得形成金属电极时的金属渗透进入氧化碲薄层,影响忆阻器的忆阻窗口的稳定性。而本发明通过先形成金属电极,利用转移的工艺将所述碲线放置于所述第一金属电极和第二金属电极表面,避免了上述问题,且利用转移的工艺将碲线放置在上面,由于碲线本身具备一定硬度,碲线和金属电极的接触面积小于先形成碲线再蒸镀金属电极的接触面积,通过将氧化碲薄层调整为合适的厚度,使得接触位置的碲线、氧化碲薄层、金属电极之间兼具忆阻器的开、关两种状态,且忆阻窗口稳定可重复。

23.本发明的忆阻器从高阻态模式,即忆阻器关态,切换为低阻态模式,即忆阻器开态时,所述忆阻器低阻态模式的电流大小与高阻态模式的电流大小的比,即所述忆阻器的开关比约为105,使得所述忆阻器能够更好的区分出所述忆阻器的高阻态模式以及低阻态模式,忆阻器的性能更优越。

附图说明

24.图1所示为本发明实施例中的一种忆阻器的制作方法的流程图;

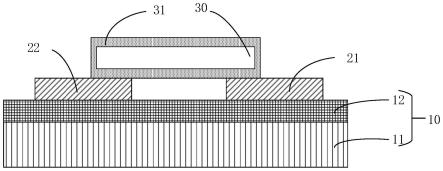

25.图2~图4所示为本发明实施例中的一种忆阻器的制作方法结构示意图;

26.图5所述为本发明实施中的一种忆阻器电流-电压特性曲线。

具体实施方式

27.为了便于本领域技术人员的理解,下面将结合具体实施例对本发明作进一步详细说明。

28.本发明提供一种忆阻器,包括:

29.衬底10;

30.所述衬底10表面具有第一金属电极21和第二金属电极22,所述第一金属电极21和第二金属电极22在同一直线上且相隔离;

31.所述第一金属电极21和第二金属电极22表面具有碲线30,所述碲线30表面具有氧化碲薄层31,所述碲线30将所述第一金属电极21和第二金属电极22相连接。

32.在本发明实施例中,所述衬底10尺寸为1厘米

×

1厘米的方块形,其他实施例中,所述衬底10尺寸为其他适合的尺寸。

33.本发明实施例中,所述衬底10具有硅层11和所述硅层11表面的二氧化硅层12。

34.所述硅层11的厚度范围为485微米~515微米,所述二氧化硅层12的厚度范围为285纳米~315纳米。

35.在其他实施例中,所述衬底也可以采用其他的衬底材料。

36.所述第一金属电极21和第二金属电极22材料为惰性金属电极。本发明实施例中,所述第一金属电极21和第二金属电极22材料为金属金。

37.所述第一金属电极21和第二金属电极22的厚度范围为50纳米~170纳米,所述第一金属电极21和第二金属电极22间的距离范围为0.5微米~15微米。

38.本发明实施例中,所述第一金属电极21和第二金属电极22的间距为3.6微米~3.7微米。

39.所述碲线30的直径范围为0.1微米~2微米,长度范围为5微米~150微米。

40.本发明实施例中,所述碲线30的直径范围为0.5微米~0.6微米,长度范围为41微米~43微米。

41.所述氧化碲薄层的厚度范围为1纳米~2纳米。

42.本发明的忆阻器的结构简单,有利于忆阻器实现商用化与小型化。

43.本发明还提供一种忆阻器的制备方法,请参考图1,包括:

44.步骤s100,提供衬底;

45.步骤s200,在所述衬底表面形成第一金属电极和第二金属电极,所述第一金属电极和第二金属电极在同一直线上且相隔离;

46.步骤s300,转移碲线到所述第一金属电极和第二电表面,所述碲线表面具有氧化碲薄层,所述碲线将所述第一金属电极和第二金属电极相连接。

47.具体的,执行步骤s100,请参考图2,提供衬底10,并清洗所述衬底10。

48.本发明实施例中,所述衬底10具有硅层11和所述硅层11表面的二氧化硅层12。

49.本发明实施例中,所述衬底10大小为1厘米

×

1厘米的方块形,其他实施例中,所述衬底10尺寸为其他适合的尺寸。

50.所述硅层11的厚度范围为485微米~515微米,所述二氧化硅层12的厚度范围为285纳米~315纳米。

51.本发明实施例中,对所述衬底10进行清洗,除去所述衬底10表面的污染物。

52.本发明实施例中,所述衬底10清洗的步骤包括,首先将所述衬底10浸入丙酮中进行清洗,其次将所述衬底10浸入异丙醇中清洗,再将所述衬底10再使用去离子水进行冲洗;最后将所述衬底10干燥处理。

53.本发明实施例中,所述衬底10清洗过程使用超声清洗机进行清洗。

54.本发明实施例中,所述衬底10干燥处理采用氮气喷枪将所述衬底10吹干,在其他实施例中,所述衬底10干燥处理可以选用空气吹尘枪吹干或者其他适合的方法。

55.执行步骤s200,请参考图3,在所述衬底10表面形成第一金属电极21和第二金属电极22,所述第一金属电极21和第二金属电极22在同一直线上且相隔离。

56.所述第一金属电极21和第二金属电极22材料为惰性金属电极。在本发明实施例中,所述第一金属电极21和第二金属电极22材料为金。

57.所述第一金属电极21和第二金属电极22的厚度范围为50纳米~170纳米,所述第

一金属电极21和第二金属电极22间的距离范围为0.5微米~15微米。具体的,在本实施例中,所述第一金属电极21和第二金属电极22的间距为3.6微米~3.7微米。

58.本发明实施例中,所述第一金属电极21和第二金属电极22通过热蒸镀工艺进行制备。所述第一金属电极21和第二金属电极22的制备过程具体包括:先在所述衬底10表面旋涂光刻胶,并对所述光刻胶进行烘干,再将所述衬底10依次进行曝光、显影,使得光刻的图案在所述衬底10表面显现出来;再通过热蒸镀工艺,在具有光刻图案衬底10表面形成金属层;最后去除光刻胶和光刻胶表面的多余的金属层,使得所述衬底10表面形成第一金属电极21和第二金属电极22。

59.本发明实施例中,去除所述衬底10表面多余的金属层的步骤包括:使用丙酮浸泡形成有金属层的衬底10去除光刻胶和光刻胶表面的多余的金属层,再将所述衬底10依次经过异丙醇清洗和去离子水冲洗,最后使用氮气枪吹干。

60.在转移碲线30之前,先在衬底10上制备所述第一金属电极21和第二金属电极22,可以更好的提升忆阻器的忆阻窗口的稳定性,避免了转移碲线30后再蒸镀金属电极,会使得金属原子蒸发到碲线30表面,由于碲线30表面的氧化碲比较稀疏,蒸发到碲线30表面的金属原子会渗透入碲线30表面的氧化碲,使得忆阻窗口的稳定性下降。

61.执行步骤s300,请参考图4,转移碲线30到所述第一金属电极21和第二电表面,所述碲线30表面具有氧化碲薄层31,所述碲线30将所述第一金属电极21和第二金属电极22相连接。

62.所述碲线30的直径范围为0.1微米~2微米,长度范围为5微米~150微米。

63.本发明实施例中,所述碲线30的直径范围为0.5微米~0.6微米,长度范围为41微米~43微米。

64.本发明实施例中,所述碲线30用物理气相沉积的方法制备。

65.通过物理气相沉积的方法制备的碲线30的直径在几百纳米的范围,碲线30表面的碲原子被氧化,但碲线内部仍有充足的碲形成导电回路,使得忆阻器的开态电流足够大。当所述第一金属电极21和第二金属电极22之间施加的电压较小时,由于所述氧化碲薄层31阻隔在金属电极和碲线之间,使得忆阻器并不导通,忆阻器处于关态;当所述第一金属电极21和第二金属电极22之间施加的电压较大时,碲线30在电场作用下形成导电细丝,导电细丝穿透氧化碲薄层31连接到第一金属电极21和第二金属电极22上,此时忆阻器导通,忆阻器处于开态;当电压减小时,导电细丝断开,忆阻器重新回到关态。由于碲的熔点较低,使得导电细丝更容易形成和熔断,忆阻器的操作电压较小,使得忆阻器的性能增强。

66.本发明实施例中,所述碲线30的制备过程包括:取一定质量的碲粉平铺于石英舟内;选用单抛氧化硅片,将所述单抛氧化硅片的二氧化硅面朝向石英舟,并覆盖在石英舟上;将覆盖有单抛氧化硅片的石英舟送入管式炉中,将管式炉内部抽为真空,再缓缓通入氢气和氩气的混合气体,使得管式炉内部的压强回到标准大气压;控制生长温度和生长时间,进行碲线30生长;碲线30生长结束后,等待管式炉自然冷却至室温,再将单抛氧化硅片从管式炉中取出,此时的单抛氧化硅片上具有生长的碲线30,最终完成碲线30的生长。

67.本发明实施例中,所述碲粉的质量范围为200毫克~300毫克,所述碲粉的纯度为99.99%。

68.使用真空泵将管式炉内部抽为真空,抽真空的时长范围为4分钟~6分钟,然后向

管式炉内通入h2和ar混合气体的流速范围为70~90标况毫升每分,所述碲线30的生长温度的范围为510摄氏度~530摄氏度,所述碲线30的生长时间的范围为10分钟~20分钟。

69.本发明实施例中,所述碲线30的生长时间的范围为16分钟~20分钟。

70.制备好的所述碲线30裸露在空气中一段时间,使得所述碲线30表面形成一层氧化碲薄层31,所述氧化碲薄层31附着在碲线30上,使得所述忆阻器具有良好的忆阻性能。

71.本发明实施例中,所述碲线放置在空气中1~7天,使得所述碲线表面形成氧化碲薄层,所述氧化碲薄层的厚度范围为1纳米~2纳米。

72.本发明实施例中,所述碲线30通过pdms(聚二甲基硅氧烷)转移至所述第一金属电极21和第二金属电极22的表面。

73.所述碲线30与所述第一金属电极21和第二金属电极22相接的接触面处,由于碲线30表面的氧化薄层31将所述碲线30和所述第一金属电极21和第二金属电极22的接触变为非直接接触,通过调整氧化碲薄层的厚度,使得接触位置的碲线、氧化碲薄层、金属电极之间兼具忆阻器的开、关两种特性。

74.本发明实施例中,所述碲线30转移到所述第一金属电极21和第二金属电极22表面的步骤包括:先将pdms裁成2毫米

×

2毫米大小的正方形,将剪裁好的pdms粘到制备有碲线30的单抛氧化硅片表面,快速揭下所述pdms,使得碲线30粘贴在所述pdms表面;再使用三维微位移平台将所述pdms上的碲线30与衬底10表面的所述第一金属电极21和第二金属电极22对准,将所述碲线30压在所述第一金属电极21和第二金属电极22表面,缓慢揭下所述pdms,使得所述碲线30留在所述第一金属电极21和第二金属电极22表面,完成碲线30的转移,此时所述碲线30将所述第一金属电极21和第二金属电极22连接。

75.如果先在衬底表面形成碲线,再在所述碲线的两侧形成第一金属电极和第二金属电极,形成金属电极的工艺(包括热蒸镀工艺、或其他)会使得形成金属电极时的金属渗透进氧化碲薄层,对氧化碲薄层造成破坏,影响忆阻器的忆阻窗口的稳定性。而本发明通过先形成金属电极,再利用转移的工艺将所述碲线放置于所述第一金属电极和第二金属电极表面,避免了上述问题,且利用转移的工艺将碲线放置在上面,由于碲线本身具备一定硬度,碲线和金属电极的接触面积小于先形成碲线再蒸镀金属电极的接触面积,这会使忆阻窗口更稳定地出现。通过调整氧化碲薄层的厚度,使得接触位置的碲线、氧化碲薄层、金属电极之间兼具忆阻器的开、关两种状态。

76.本发明实施例中,所述忆阻器的设置电压与恢复电压均小于5v。

77.本发明实施例中,所述忆阻器工作时,请参考图5,电压由0v扫描到-0.5v附近时,所述忆阻器由高阻态模式切换为低阻态模式,电压继续由-0.5v扫描到-1v,忆阻器在此过程中处于低阻态模式;电压由-1v扫描到-0.15v附近时,忆阻器由低阻态模式切换回高阻态模式。本发明提供的忆阻器从高阻态模式切换为低阻态模式的电压为设置电压,所述忆阻器从低阻态模式切换回高阻态模式的电压为恢复电压,所述忆阻器的设置电压为-0.5v,此时电路中的电流为-5.51

×

10-6

a,所述忆阻器的恢复电压为-0.15v,此时电路中的电流为-6.69

×

10-12

a。

78.本发明实施例中,低阻态模式的电流范围为-2.70

×

10-7

a~-5.51

×

10-6

a,对应相同电压下,高阻态模式的电流范围为-6.69

×

10-12

a~-2.17

×

10-11

a。经计算得到所述忆阻器低阻态模式电流大小与高阻态模式电流大小的比值约为105,使得所述忆阻器能够更好

的区分出所述忆阻器的高阻态模式以及低阻态模式,忆阻器的性能更优越。

79.同时,本发明提供的所述忆阻器从高阻态模式切换回低阻态模式的电压,即设置电压为-0.5v,从低阻态模式切换回高阻态模式的电压,即恢复电压为-0.15v,使得所述忆阻器具有极低的功耗,更有利于器件在未来的发展和应用。

80.最后说明,任何依靠本发明装置结构以及所述实施例的技术方案,进行的部分或者全部技术特征的修改或者等同替换,所得到的本质不脱离本发明的相应技术方案,都属于本发明装置结构以及所述实施方案的专利范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1