一种基于施密特触发器的抗干扰一线通讯接收方法及系统与流程

本发明属于电动车充电信息通讯,涉及一种基于施密特触发器的抗干扰一线通讯接收方法。

背景技术:

1、目前电动车行业在硬件设计上有收发电路分别使用两个io口一个作为输入一个作为输出来设计的;也有将一个io口复用,通过切换io口的输入输出设置将发送和接收功能分时设计的。为了节省成本,在实际中常会采用一个io口分时复用作为一线通信号的收发端,因为一线通是双向单工通讯既能满足通讯要求又能节省成本。实际应用中,大都采用了一线通方式进行充电器和电池bms及控制器等的信息通讯。其中,一线通采用国际标准的sif通讯协议,电平逻辑遵从ttl规范。

2、ttl(transi stor-transi sitor logic)结构,大多采用vcc 5v的,以vcc 5v为例进行说明:端口输入电平逻辑:0v≤vl≤0.8v,2v≤vh≤5v;即输入信号大于2v为高电平代表逻辑1,低于0.8v为低电平代表逻辑0。当电平介于0.8v与2v之间时,无法确定逻辑,如图2所示。

3、一线通应用中,使用一条通讯线来传送方波信号,约定用脉冲时间宽度(以下简称宽度)或宽度比来表达送载的信息单元,如图1所示,通过t1和t2的时间宽度或宽度比,加上事先约定好的定义(协议)就可以解读出信息。如起始、停止、位信息1、位信息0等,从而达到传递通讯的目的。其典型精简电路如图3所示,其中,当只有一个发送和一个接收的固定的联接通讯时,电路上是不设计隔离二极管d1进去的。当多独立节点相联结通讯时才会将隔离二极管d1设计进去,如图4所示,一个节点发送两个节点接收,如果在联接状态下,当(未接隔离二极管d1)的接收节点1没有供电(5v未工作)时,节点1的电路会将一线通总线上的电平一直拉低,导致总线上的接收节点2无法收到通讯数据。所以隔离二极管d1必须使用,用来隔离未上电的设备对总线的影响,其中电容c1在电路上起到滤除通讯信号线上杂波的作用。但其在实际操作中仍存在以下问题:在使用隔离二极管d1的情况下,由于二极管有压差(最小0.4v),外部的一线通信号上发送的逻辑0信号,如信号的最低电平为0v,经上述电路传输到mcu的io引脚时,最低电平变为0.4v,这就使得可识别的低电平空间由0v≤vl≤0.8v变为0.4v≤vl≤0.8v。而且,作为发送节点,总是有硬件电路来实现发送高低电平逻辑的,经电路控制的低电平不再是绝对的0v,也会有零点几伏电压存在,一般为0.2v-0.4v,以最小0.2v计,加上隔离二极管d1的压差0.4v,接收方逻辑0可识别的低电平空间被压缩到0.6v≤vl≤0.8v,识别空间变的更狭窄;如果一线通通讯总线上有杂波干扰引起电平波动,还会加大低电平逻辑0的识别难度,甚至识别不到。同时,电容c1的不同电容值都有适用的滤波频段,如:0.1uf适用10k-100k赫兹频段,10nf适合100k-1m赫兹频段,1nf适合1m-10m赫兹频段,电路中的电容c1的滤波频段带宽是有限的,那么势必无法完全将一线通通讯总线上的杂波过滤掉,会收到一定的杂波干扰,从而会造成上述提到的引起电平波动,会加大低电平逻辑0的识别难度,甚至识别不到,而为了做到更宽的频段滤波,需增加滤波电路和印刷线路板空间,引起产品成本上升,同时也无法达到完全消除杂波。同时,如果电容c1电容值增大时,会造成通讯信号方波上升沿削波过大(如图5所示),延迟高电平信号的接收,影响高电平宽度t2的采集测量。因此,具体通讯协议会根据t2的时间宽度对此上升延迟做出最大时间要求。根据此要求,在电路设计中,滤波电容c1会有最大取值限制,因此电容c1也无法通过硬件设计无限制做宽频段滤波。

技术实现思路

1、本发明的目的是为了解决上述技术问题,提出了一种基于施密特触发器的抗干扰一线通讯接收方法。

2、本发明的目的可通过下列技术方案来实现:一种基于施密特触发器的抗干扰一线通讯接收方法,其特征在于,包括如下步骤:

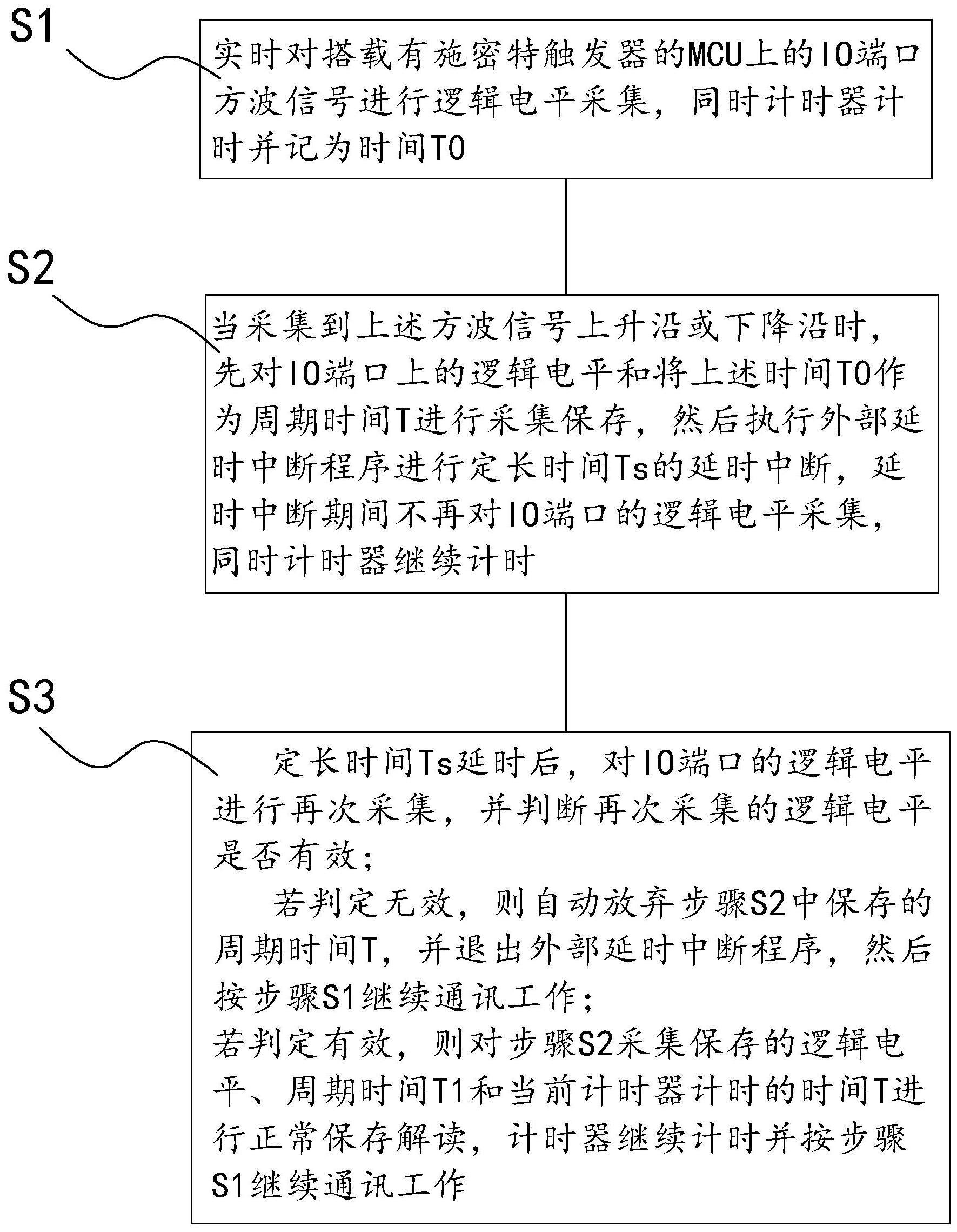

3、s1、实时对搭载有施密特触发器的mcu上的io端口方波信号进行逻辑电平采集,同时计时器计时并记为时间t0;

4、s2、当采集到上述方波信号上升沿或下降沿时,先对io端口上的逻辑电平和将上述时间t0作为周期时间t进行采集保存,然后执行外部延时中断程序进行定长时间ts的延时中断,延时中断期间不再对io端口的逻辑电平采集,同时计时器继续计时;

5、s3、定长时间ts延时后,对io端口的逻辑电平进行再次采集,并判断再次采集的逻辑电平是否有效;

6、若判定无效,则自动放弃步骤s2中保存的周期时间t,并退出外部延时中断程序,然后按步骤s1继续通讯工作;

7、若判定有效,则对步骤s2采集保存的逻辑电平、周期时间t1和当前计时器计时的时间t进行正常保存解读,计时器继续计时并按步骤s1继续通讯工作;

8、其中,判断再次采集的逻辑电平是否有效具体为:若采集的逻辑电平与步骤s2中保存的逻辑电平一致时,则判定为有效;反之,则判定为无效;所述对当前计时器计时的时间t进行正常保存解读具体为:将当前计时器计时的时间t0减去步骤s2中的周期时间t后的时间值赋值给当前计时器计时的时间t0并在此基础上继续计时。

9、在上述的一种基于施密特触发器的抗干扰一线通讯接收方法中,所述的计时器配置为一个对系统时钟进行分频计数的计时器。

10、在上述的一种基于施密特触发器的抗干扰一线通讯接收方法中,所述步骤s2中的定长时间ts可根据实际进行调整。

11、在上述的一种基于施密特触发器的抗干扰一线通讯接收方法中,所述逻辑电平为高电平或低电平。

12、在上述的一种基于施密特触发器的抗干扰一线通讯接收方法中,所述步骤s1之前还包括有设置步骤,具体为:将收发一线通对应的端口设置为数字信号接收模式,同时设置该io端口为外部中断接收端口,中断模式为上升沿和下降沿触发模式。

13、一种基于施密特触发器的抗干扰一线通讯接收系统,包括充电器和电池上的mcu,其特征在于:还包括施密特触发器,所述施密特触发器连接在充电器和mcu上io端口之间,所述mcu包括计时器、定时器、采集单元、存储单元和处理单元,所述采集单元用于采集mcu上io端口的逻辑电平信号并将该逻辑电平信号反馈给处理单元;所述计时器用于计时并记为时间t0;所述定时器用于定长时间ts的定时;所述存储单元用于储存上述的逻辑电平、计时时间t0和延时中断程序;所述处理单元用于当接收到采集单元反馈的方波信号上升沿或下降沿时,先控制存储单元储存当前采集到的io端口逻辑电平和上述计时时间t0,此时计时时间t0作为周期时间t进行储存,然后执行延时中断程序进行定长时间ts的延时中断,延时中断期间控制采集单元不工作,并在延时中断结束后控制采集单元再次对io端口进行逻辑电平采集,根据再次采集到的io端口逻辑电平作出是否有效的判断,若判定无效,则控制存储单元自动放弃保存的周期时间t,并退出外部延时中断程序,然后控制继续通讯工作,若判定有效,则对采集保存的逻辑电平、周期时间t1和当前计时器计时的时间t进行正常保存解读,并控制计时器继续计时并继续通讯工作。

14、在上述的一种基于施密特触发器的抗干扰一线通讯接收系统中,所述施密特触发器为外设施密特触发电路,或集成在io端口上。

15、在上述的一种基于施密特触发器的抗干扰一线通讯接收系统中,所述根据再次采集到的io端口逻辑电平作出是否有效的判断具体为:若采集的逻辑电平与之前存储单元保存的逻辑电平一致时,则判定为有效;反之,则判定为无效。

16、在上述的一种基于施密特触发器的抗干扰一线通讯接收系统中,所述对当前计时器计时的时间t进行正常保存解读具体为:将当前计时器计时的时间t0减去周期时间t后的时间值赋值给当前计时器计时的时间t0并在此基础上继续计时。

17、在上述的一种基于施密特触发器的抗干扰一线通讯接收系统中,所述的计时器配置为一个对系统时钟进行分频计数的计时器。

18、与现有技术相比,本抗干扰一线通讯接收系统及方法具有如下优点:

19、1、采用施密特触发器进行触发工作,可使得mcu的io端逻辑0可识别的低电平逻辑阈值可提高,比如5v电压时其低电平逻辑阈值可提升至1.5v,这样大大拓宽了识别空间,降低识别难度;同时,施密特触发器还具有一定的杂波抗干扰能力,也一定程度上降低杂波干扰,从而降低低电平逻辑电平的识别难度;

20、2、当检测到触发信号(上升沿或下降沿)时,执行延时中断程序,此时,采集单元不再对i0端口进行逻辑电平采集,相当于该段时间内io口上的杂波干扰不会被读取到,又由于在中断响应程序内,该io口上的杂波干扰也不会被中断响应,从而达到了软件滤波的效果,通过软件滤波的方式进行杂波滤波,从而无需增加电容c1的电容值,以避免造成通讯信号方波上升沿削波过大;同时,也无需增加电容电路和印刷线路板,从而降低产品成本。

- 还没有人留言评论。精彩留言会获得点赞!