一种中子发生器的控制装置的制作方法

1.本实用新型涉及控制工程技术领域,特别涉及一种中子发生器的控制装置。

背景技术:

2.中子发生器被广泛应用于石油测井、核物理实验以及航天点火等技术领域,在使用中子发生器时,通常需要中子发生器中的中子管产生中子才能进行相关的实验研究。请参见图1,图1为中子发生器的结构示意图。其中,中子发生器是由高压变压器、倍压电路、取样电路以及中子管所组成。由于中子管所需要的工作电压很高,所以,在实际应用中,需要在中子发生器内部填充惰性气体来增加中子发生器的内部绝缘,并防止中子发生器内部出现高压打火的现象。此外,由于中子具有很强的辐射性,所以,中子发生器的高压控制电路对于中子发生器的安全运行而言,具有极为重要的影响。

3.由于新中子管的产额会比较高,所以,当中子发生器内设置有新的中子管时,此时不需要向高压变压器提供很高的供电电压就可以达到相关的测试要求。但是,随着中子管的不断使用,产额逐渐降低,向高压变压器提供的电压就需要逐渐增高,此时就需要向高压变压器提供较高的供电电压才能让中子管产生中子。

4.在现有技术中,考虑到中子管的使用损耗,通常是采用pwm(pulse width modulation,脉冲宽度调制)技术,向高压变压器的初级中心抽头t-2提供90v的直流电压,并向高压变压器的另外两个抽头t-1和t-3提供频率固定、脉冲宽度随控制电压变化而变化的触发振荡脉冲来对中子发生器进行高压控制。但是,在此供电方式下,由于向高压变压器的初级中心抽头t-2提供的供电电压已经达到了中子管所需供电电压的极限值,这样就极易使得中子发生器产生高压尖脉冲,并将中子发生器内的部分器件击穿,从而毁坏中子发生器。目前,针对上述问题,还没有较为有效的解决办法。

技术实现要素:

5.有鉴于此,本实用新型的目的在于提供一种中子发生器的控制装置,以防止中子发生器产生高压尖脉冲,并降低中子发生器发生故障的概率。其具体方案如下:

6.一种中子发生器的控制装置,包括:输出电压为0~80v的电压生成模块、第一电感、第一电容以及能够输出占空比为50%且频率可调pwm信号的触发脉冲生成器;

7.其中,所述电压生成模块的输出端与所述第一电感的第一端相连,所述第一电感的第二端分别与所述第一电容的第一端和中子发生器中高压变压器初级侧的中心抽头相连,所述第一电容的第二端接地,所述触发脉冲生成器的第一输出端和第二输出端分别与所述高压变压器初级侧除去所述中心抽头的另外两个抽头相连。

8.优选的,所述触发脉冲生成器包括:电位调节器、第一电阻、第二电阻、第三电阻、第四电阻、第五电阻、第二电容、第三电容、第四电容、第一nmos管、第二nmos管以及能够输出频率可调且相位互补的两路pwm信号的ic芯片;

9.其中,所述ic芯片的ct端和rt端分别与所述第二电容的第一端和所述第一电阻的

第一端相连,所述第二电容的第二端分别与所述电位调节器的控制端和输入端相连,所述电位调节器的输入端接地,所述电位调节器的输出端与所述第一电阻的第二端相连,所述ic芯片的in+端和vref端分别与所述第三电阻的第一端和第二端相连,所述ic芯片的in-端和comp端分别与所述第二电阻的第一端和第二端相连,所述ic芯片的电压输入端均用于接收15v的电压,所述ic芯片的sd端、g端、cs-端和cs+端均接地,所述ic芯片的第一输出端和第二输出端分别与所述第三电容的第一端和所述第四电容的第一端相连,所述第三电容的第二端分别与所述第四电阻的第一端和所述第一nmos管的栅极相连,所述第四电容的第二端分别与所述第五电阻的第一端和所述第二nmos管的栅极相连,所述第四电阻的第二端、所述第五电阻的第二端、所述第一nmos管的源极和所述第二nmos管的源极均接地,所述第一nmos管的漏极与第一抽头相连,所述第二nmos管的漏极与第二抽头相连;所述第一抽头和所述第二抽头均为所述高压变压器初级侧除去所述中心抽头之外的抽头。

10.优选的,所述ic芯片具体为lm1524。

11.优选的,所述电位调节器具体为能够承受大于预设温度值的贴片电位调节器。

12.优选的,所述电压生成模块包括:

13.用于生成占空比可调的pwm电路;

14.用于根据目标输入信号和目标电压采样信号生成目标控制信号,并利用所述目标控制信号对所述pwm电路进行控制的输入控制电路;

15.用于根据90v的直流输入信号和所述pwm电路的输出信号生成0~80v电压的dcdc降压电路;

16.用于对所述dcdc降压电路的输出电压进行采样,得到所述目标电压采样信号的输出采样电路。

17.优选的,所述输入控制电路包括:第一运放、第二运放、第三运放、第四运放、第六电阻、第七电阻、第八电阻、第九电阻、第十电阻、第十一电阻、第十二电阻和第十三电阻;

18.其中,所述第一运放的正输入端分别与所述第六电阻的第一端和所述第七电阻的第一端相连,所述第六电阻的第二端用于接收12v的电压,所述第七电阻的第二端接地,所述第一运放的负输入端分别与所述第一运放的输出端和所述第八电阻的第一端相连,所述第八电阻的第二端分别与所述第九电阻的第一端和所述第三运放的正输入端相连,所述第二运放的负输入端分别与所述第二运放的输出端和所述第十电阻的第一端相连,所述第十电阻的第二端分别与所述第三运放的负输入端和所述第十一电阻的第一端相连,所述第十一电阻的第二端分别与所述第三运放的输出端和所述第十二电阻的第一端相连,所述第九电阻的第二端分别与所述第四运放的负输入端和所述第四运放的输出端相连,所述第四运放的正输入端与所述第十三电阻的第一端相连;

19.相应的,所述第二运放的正输入端用于接收所述目标输入信号,所述第十三电阻的第二端用于接收所述目标电压采样信号,所述第十二电阻的第二端用于输出所述目标控制信号。

20.优选的,所述pwm电路包括:pwm芯片、第十四电阻、第十五电阻、第十六电阻、第五电容、第六电容和第七电容;

21.其中,所述pwm芯片的cmp端分别与所述第十四电阻的第一端和所述第五电容的第一端相连,所述第十四电阻的第二端分别与所述第五电容的第二端和所述pwm芯片的vfb端

相连,所述pwm芯片的vref端分别与所述第十五电阻的第一端和所述第六电容的第一端相连,所述第十五电阻的第二端分别与所述pwm芯片的rt/ct端和所述第七电容的第一端相连,所述第七电容的第二端和所述第六电容的第二端均接地,所述pwm芯片的isen端与所述第十六电阻的第一端相连,所述第十六电阻的第二端接地,所述pwm芯片的vdd端用于接收12v的电压;

22.相应的,所述pwm芯片的drv端为所述pwm电路的输出端。

23.优选的,所述pwm芯片具体为uc1845。

24.优选的,所述dcdc降压电路包括:pmos管、第十七电阻、第十八电阻、第十九电阻、第三nmos管、二极管、第二电感、第一钽电解电容和第二钽电解电容;

25.其中,所述第三nmos管的栅极和源极分别与所述第十七电阻的第一端和所述第十八电阻的第一端相连,所述第三nmos管的漏极接地,所述第十八电阻的第二端分别与所述pmos管的栅极和所述第十九电阻的第一端相连,所述第十九电阻的第二端与所述pmos管的源极相连,所述pmos管的漏极分别与所述二极管的负极和所述第二电感的第一端相连,所述二极管的正极接地,所述第二电感的第二端分别与所述第一钽电解电容的第一端和所述第二钽电解电容的第一端相连,所述第一钽电解电容的第二端和所述第二钽电解电容的第二端均接地;

26.相应的,所述第十七电阻的第二端用于接收所述pwm电路的输出信号,所述第十九电阻的第二端用于接收90v的直流电压,所述第一钽电解电容的第一端为所述dcdc降压电路的输出端。

27.优选的,所述输出采样电路包括:第二十电阻和第二十一电阻;

28.其中,所述第二十一电阻的第一端与所述第二十电阻的第一端相连,所述第二十一电阻的第二端接地;

29.相应的,所述第二十电阻的第二端为所述输出采样电路的输入端,所述第二十电阻的第一端为所述输出采样电路的输出端。

30.可见,在本实用新型所提供中子发生器的控制电路中,由于电压生成模块所输出的电压范围为0~80v,触发脉冲生成器能够生成占空比为50%且频率可调的pwm信号,并且,电压生成模块所输出0~80v的直流电压是通过第一电感和第一电容来向中子发生器内高压变压器初级侧的中心抽头进行供电,这样就使得高压变压器所接收到的供电电压不会发生突变,且不会超过高压变压器所需要的极限电压,所以,在此设置方式下,中子发生器内部的高压变压器就不会产生高压尖脉冲,这样就可以显著减少中子发生器发生故障的概率。

附图说明

31.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

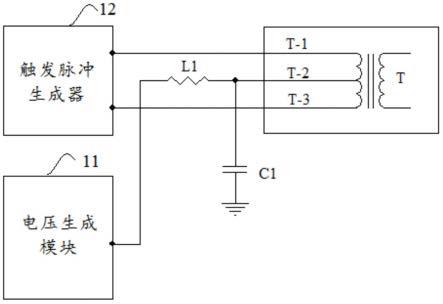

32.图1为中子发生器的结构示意图;

33.图2为本实用新型实施例所提供的一种中子发生器的控制装置的结构图;

34.图3为本实用新型实施例所提供的一种触发脉冲生成器的结构图;

35.图4为使用本实用新型所提供中子发生器的控制装置对中子发生器进行高压控制时,高压变压器初级侧中心抽头的输出波形变化图;

36.图5为本实用新型实施例所提供的一种电压生成模块的原理示意图;

37.图6为dcdc降压电路对输入电压进行处理时的原理示意图;

38.图7为本实用新型实施例所提供的一种输入控制电路的结构图;

39.图8为本实用新型实施例所提供的一种pwm电路的结构图;

40.图9为本实用新型实施例所提供的一种dcdc降压电路的结构图;

41.图10为本实用新型实施例所提供的一种输出采样电路的结构图;

42.图11为本实用新型实施例所提供电压生成模块的整体结构图。

具体实施方式

43.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

44.请参见图2,图2为本实用新型实施例所提供的一种中子发生器的控制装置的结构图,该控制装置包括:输出电压为0~80v的电压生成模块11、第一电感l1、第一电容c1以及能够输出占空比为50%且频率可调pwm信号的触发脉冲生成器12;

45.其中,电压生成模块11的输出端与第一电感l1的第一端相连,第一电感l1的第二端分别与第一电容c1的第一端和中子发生器中高压变压器t初级侧的中心抽头t-2相连,第一电容c1的第二端接地,触发脉冲生成器12的第一输出端和第二输出端分别与高压变压器t初级侧除去中心抽头的另外两个抽头t-1、t-3相连。

46.在本实施例中,是提供了一种新型的中子发生器的控制装置,利用该控制装置来对中子发生器进行高压控制,可以防止中子发生器产生高压尖脉冲,并降低中子发生器出现故障的概率。

47.在该控制装置中,是设置有能够输出电压为0~80v的电压生成模块11、第一电感l1、第一电容c1以及能够输出占空比为50%且频率可调pwm信号的触发脉冲生成器12。在本实施例中,假设中子发生器内部高压变压器的变比为1:n,倍压电路的变比为m,触发脉冲生成器12的输出占空比d为50%。如果高压变压器t的输入电压为vin,中子管的输出电压为hv,那么就会存在以下关系式:

48.hv=vin*n*m*(2*d)=vin*n*m

49.式中,m和n均为固定值,vin的取值范围为0~80v。

50.可以理解的是,由于电压生成模块11是通过第一电感l1和第一电容c1向中子发生器内部的高压变压器进行供电,并且,供电电压的取值范围为0~80v,在此设置方式下,高压变压器t初级中心抽头t-2的供电电压就会由零逐渐缓慢上升至中子发生器所需要的合适工作电压,在此工作机制下,中子发生器内部就不会产生高压尖脉冲。由于触发脉冲生成器12所输出的pwm信号频率可调,这样就可以使得中子发生器内部的高压变压器能够工作在最佳的谐振状态。此外,在实际应用中,可以将第一电感l1的取值参数设定为2mh、1a,并

将第一电容c1的容值设定为4700p,耐压值设定为2000v。

51.换言之,由于中子发生器内部高压变压器t初级侧中心抽头t-2的供电电压是由零逐渐缓慢上升,直至达到中子发生器合适的工作电压,所以,中子发生器内部就不会产生非常高的高压尖脉冲,这样就达到了对中子发生器内部倍压电路进行保护的目的。并且,由于高压变压器初级侧另外两个抽头t-1和t-3所输出的频率可以调节,所以,通过调节高压变压器t-1和t-3抽头的频率就可以使得不同类型的中子发生器均可以工作在最佳状态,这样就可以相对减少中子发生器的工作电流。经过大量实践证明,采用本技术所提供的中子发生器控制电路不仅使得中子发生器的工作电流较小,而且,也可以显著降低中子发生器发生故障的概率。

52.可见,在本实施例所提供中子发生器的控制电路中,由于电压生成模块所输出的电压范围为0~80v,触发脉冲生成器能够生成占空比为50%且频率可调的pwm信号,并且,电压生成模块所输出0~80v的直流电压是通过第一电感和第一电容来向中子发生器内高压变压器初级侧的中心抽头进行供电,这样就使得高压变压器所接收到的供电电压不会发生突变,且不会超过高压变压器所需要的极限电压,所以,在此设置方式下,中子发生器内部的高压变压器就不会产生高压尖脉冲,这样就可以显著减少中子发生器发生故障的概率。

53.基于上述实施例,本实施例对技术方案作进一步的说明与优化,请参见图3,图3为本实用新型实施例所提供的一种触发脉冲生成器的结构图。作为一种优选的实施方式,上述触发脉冲生成器12包括:电位调节器w、第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第五电阻r5、第二电容c2、第三电容c3、第四电容c4、第一nmos管n1、第二nmos管n2以及能够输出频率可调且相位互补的两路pwm信号的ic芯片;

54.其中,ic芯片的ct端和rt端分别与第二电容c2的第一端和第一电阻r1的第一端相连,第二电容c2的第二端分别与电位调节器w的控制端和输入端相连,电位调节器w的输入端接地,电位调节器w的输出端与第一电阻r1的第二端相连,ic芯片的in+端和vref端分别与第三电阻r3的第一端和第二端相连,ic芯片的in-端和comp端分别与第二电阻r2的第一端和第二端相连,ic芯片的电压输入端均用于接收15v的电压,ic芯片的sd端、g端、cs-端和cs+端均接地,ic芯片的第一输出端和第二输出端分别与第三电容c3的第一端和第四电容c4的第一端相连,第三电容c3的第二端分别与第四电阻r4的第一端和第一nmos管n1的栅极相连,第四电容c4的第二端分别与第五电阻r5的第一端和第二nmos管n2的栅极相连,第四电阻r4的第二端、第五电阻r5的第二端、第一nmos管n1的源极和第二nmos管n2的源极均接地,第一nmos管n1的漏极与第一抽头相连,第二nmos管n2的漏极与第二抽头相连;第一抽头和第二抽头均为高压变压器t初级侧除去中心抽头t-2之外的抽头。

55.需要说明的是,在本实施例中,ic(integrated circuit chip)芯片的电压输入端是指ic芯片的vi端、ca端和cb端。触发脉冲生成器的核心是ic芯片,并且,ic芯片是一个具有双路输出、相位互补且输出频率可调的高温pwm器件。具体的,可以将ic芯片设置为lm1524。

56.其中,ic芯片的输出频率表达式为:

57.f=1/(rt*ct)

58.式中,ct为ic芯片ct端的对地电阻,在图3中ct为第二电容c2对地的阻值,rt为ic

芯片rt端的对地电阻,在图3中rt=r2+w,r2为第二电阻r2的阻值,w为电位调节值w的阻值。

59.由ic芯片输出频率的表达式可以看出,通过对电位调节器的阻值进行调节就可以对ic芯片的输出频率进行调整,并使得高压变压器t工作于最佳谐振状态,此时中子发生器内部的工作电流较小,不会产生高压尖脉冲。具体请参见图4,图4为使用本实用新型所提供中子发生器的控制装置对中子发生器进行高压控制时,高压变压器初级侧中心抽头的输出波形变化图。

60.可以理解的是,因为ic芯片的in+端是通过第三电阻r3与ic芯片的vref端相连,ic芯片的in-端是通过第二电阻r2与ic芯片的comp端相连,这样就可以使得ic芯片输出频率的占空比为50%。此外,利用ic芯片的第一输出端ea和第二输出端eb可以实现ic芯片输出信号的相位互补。

61.在实际应用中,第二电容c2可以选用2700p、0805封装的高温贴片电容,第一电阻r1可以选用30k、0805封装的高温贴片电阻,第三电容c3和第四电容c4均选用0.1u、0805封装的高温贴片电容,第二电阻r2和第三电阻r3均选用1k、0805封装的高温贴片电阻,第四电阻r4和第五电阻r5均选用100k、0805封装的高温贴片电阻,第一nmos管n1和第二nmos管n2均选用30n120;此外,电位调节器w可以选用能够承受大于预设温度值的贴片电位调节器。具体的,电位调节器w可以选用10k的高温贴片电位器。

62.基于上述实施例,本实施例对技术方案作进一步的说明与优化,请参见图5,图5为本实用新型实施例所提供的一种电压生成模块的原理示意图。作为一种优选的实施方式,电压生成模块11包括:

63.用于生成占空比可调的pwm电路101;

64.用于根据目标输入信号和目标电压采样信号生成目标控制信号,并利用目标控制信号对pwm电路101进行控制的输入控制电路102;

65.用于根据90v的直流输入信号和pwm电路101的输出信号生成0~80v电压的dcdc降压电路103;

66.用于对dcdc降压电路103的输出电压进行采样,得到目标电压采样信号的输出采样电路104。

67.在本实施例中,为了使得电压生成模块能够输出0~80v的直流电压,是在电压生成模块中设置了pwm电路101、输入控制电路102、dcdc降压电路103以及输出采样电路104。

68.其中,dcdc降压电路103是电压生成模块11的核心,通过向dcdc降压电路103输入90v的直流电压以及0~5v的直流电压就可以使得电压生成模块输出0~80v的直流电压。具体请参见图6,图6为dcdc降压电路对输入电压进行处理时的原理示意图。

69.请参见图7,图7为本实用新型实施例所提供的一种输入控制电路的结构图。作为一种优选的实施方式,输入控制电路102包括:第一运放u1、第二运放u2、第三运放u3、第四运放u4、第六电阻r6、第七电阻r7、第八电阻r8、第九电阻r9、第十电阻r10、第十一电阻r11、第十二电阻r12和第十三电阻r13;

70.其中,第一运放u1的正输入端分别与第六电阻r6的第一端和第七电阻r7的第一端相连,第六电阻r6的第二端用于接收12v的电压,第七电阻r7的第二端接地,第一运放u1的负输入端分别与第一运放u1的输出端和第八电阻r8的第一端相连,第八电阻r8的第二端分别与第九电阻r9的第一端和第三运放u3的正输入端相连,第二运放u2的负输入端分别与第

二运放u2的输出端和第十电阻r10的第一端相连,第十电阻r10的第二端分别与第三运放u3的负输入端和第十一电阻r11的第一端相连,第十一电阻r11的第二端分别与第三运放u3的输出端和第十二电阻r12的第一端相连,第九电阻r9的第二端分别与第四运放u4的负输入端和第四运放u4的输出端相连,第四运放u4的正输入端与第十三电阻r13的第一端相连;

71.相应的,第二运放u2的正输入端用于接收目标输入信号,第十三电阻r13的第二端用于接收目标电压采样信号,第十二电阻r12的第二端用于输出目标控制信号。

72.在本实施例中,是对输入控制电路102的设置方式进行了具体说明。其中,输入控制电路102的作用是用于接收目标输入信号vin和输出采样电路104所采样得到的目标采样信号vsamp,并根据目标输入信号vin和目标采样信号vsamp向pwm电路101输出相应的控制信号。实际上,输入控制电路102是一个加减法电路,这样就可以相对降低输入控制电路102的结构复杂度。

73.请参见图8,图8为本实用新型实施例所提供的一种pwm电路的结构图。作为一种优选的实施方式,pwm电路101包括:pwm芯片、第十四电阻r14、第十五电阻r15、第十六电阻r16、第五电容c5、第六电容c6和第七电容c7;

74.其中,pwm芯片的cmp端分别与第十四电阻r14的第一端和第五电容c5的第一端相连,第十四电阻r14的第二端分别与第五电容c5的第二端和pwm芯片的vfb端相连,pwm芯片的vref端分别与第十五电阻r15的第一端和第六电容c6的第一端相连,第十五电阻r15的第二端分别与pwm芯片的rt/ct端和第七电容c7的第一端相连,第七电容c7的第二端和第六电容c6的第二端均接地,pwm芯片的isen端与第十六电阻r16的第一端相连,第十六电阻r16的第二端接地,pwm芯片的vdd端用于接收12v的电压;

75.相应的,pwm芯片的drv端为pwm电路的输出端。

76.在本实施例中,pwm电路101的作用是用于接收输入控制电路102所输出的控制信号,并根据输入控制电路所发送的控制信号输出相应的脉冲信号,然后,再控制dcdc降压电路103中mos管的导通与截止。具体的,在实际应用中,可以将pmw电路的核心器件pwm芯片设置为uc1845的高温贴片控制器。

77.请参见图9,图9为本实用新型实施例所提供的一种dcdc降压电路的结构图。作为一种优选的实施方式,dcdc降压电路103包括:pmos管p、第十七电阻r17、第十八电阻r18、第十九电阻r19、第三nmos管n3、二极管d、第二电感l2、第一钽电解电容c01和第二钽电解电容c02;

78.其中,第三nmos管n3的栅极和源极分别与第十七电阻r17的第一端和第十八电阻r18的第一端相连,第三nmos管n3的漏极接地,第十八电阻r18的第二端分别与pmos管p的栅极和第十九电阻r19的第一端相连,第十九电阻r19的第二端与pmos管p的源极相连,pmos管p的漏极分别与二极管d的负极和第二电感l2的第一端相连,二极管d的正极接地,第二电感l2的第二端分别与第一钽电解电容c01的第一端和第二钽电解电容c02的第一端相连,第一钽电解电容c01的第二端和第二钽电解电容c02的第二端均接地;

79.相应的,第十七电阻r17的第二端用于接收pwm电路的输出信号,第十九电阻r19的第二端用于接收90v的直流电压,第一钽电解电容c01的第一端为dcdc降压电路的输出端。

80.在本实施例中,为了降低输出采样电路104的结构复杂度,是使用两个电阻来搭建输出采样电路。请参见图10,图10为本实用新型实施例所提供的一种输出采样电路的结构

图。作为一种优选的实施方式,输出采样电路104包括:第二十电阻r20和第二十一电阻r21;

81.其中,第二十一电阻r21的第一端与第二十电阻r20的第一端相连,第二十一电阻r21的第二端接地;

82.相应的,第二十电阻r20的第二端为输出采样电路的输入端,第二十电阻r20的第一端为输出采样电路的输出端。

83.为了使得本领域技术人员能够清楚地知悉到本技术所提供电压生成模块的工作原理,本实施例对电压生成模块内部所设置各个电路单元的工作流程进行详细说明。请参见图11,图11为本实用新型实施例所提供电压生成模块的整体结构图。其中,电压生成模块包括输入控制电路、pwm电路、dcdc降压电路以及输出采样电路。

84.1、输出采样电路

85.由于输出采样电路的结构比较简单,所以,先对输出采样电路的信号采样过程进行具体说明。可以理解的是,因为输出采样电路是由第二十电阻r20和第二十一电阻r21所组成,所以,输出采样电路采样得到的目标电压采样信号vsamp的表达式为:

86.vsamp=r21/(r20+r21)*vout;

87.式中,r20为第二十电阻r20的阻值,r21为第二十一电阻r21的阻值,vout为dcdc降压电路的输出电压。

88.可以理解的是,由于dcdc降压电路输出电压vout的取值范围为0~80v,而dcdc降压电路的输出电压是由90v的直流输入电压和输入控制电路中的目标输入信号vin进行控制,而vin的取值范围为0~5v,所以,目标电压采样信号vsamp的表达式即为:r21/(r20+r21)=5/80=1/16。

89.在实际应用中,可以将第二十电阻r20选择为阻值为150k、0805封装的高温贴片电阻,并第二十一电阻r21选择为阻值为10k、0805封装的高温贴片电阻。

90.2、输入控制电路

91.输入控制电路的作用是用于接收目标输入信号vin和输出采样电路所采样得到的目标采样信号vsamp,并根据输出采样电路所反馈的目标电压采样信号vsamp输出对pwm电路进行控制的控制信号。根据图11所示输入控制电路的结构图可知,输入控制电路实际上是一个加减法电路,其输出信号的表达式为:

92.v2.5=2.5+vsamp-vin

93.式中,v2.5为输入控制电路的输出信号,vsamp为输出采样电路所采集得到的目标电压采样信号,vin为输入控制电路所接收到的目标输入信号,并且,0≤vin≤5v。

94.当vin=0时,v2.5≥2.5v,此时pwm电路的输出信号为零,dcdc降压电路中的pmos管处于截止状态,dcdc降压电路的输出为零,输出采样电路所采集到的目标电压采样信号vsamp为零;

95.当vin》0时,vsamp《vin,此时v2.5《2.5v,pwm电路正常运行,dcdc降压电路中的pmos管处于导通状态,输出采样电路所采样到的目标电压采样信号vsamp就会逐渐增加;

96.当vsamp=vin时,v2.5=2.5v,pwm电路的输出信号为零,dcdc降压电路中的pmos管处于截止状态,在此情况下,输出采样电路所采样到的目标电压采样信号vsamp就不会增加,此时vsamp=16*vin。

97.在实际应用中,第一运放u1、第二运放u2、第三运放u3和第四运放u4可以选用高温

贴片的lm124,第六电阻r6可以选用阻值为38k、0805封装的高温贴片电阻,第七电阻r7可以选用阻值为10k、0805封装的高温贴片电阻,第八电阻r8、第九电阻r9、第十电阻r10、第十一电阻r11、第十二电阻r12和第十三电阻r13均可以选择为阻值为1k、0805封装的高温贴片电阻。

98.当将第六电阻r6的阻值设定为38k、第七电阻r7的阻值设定为10k时,第一运放u1的正输入端就会接收到2.5v的电压,第一运放对2.5v电压进行跟随,作为加减法电路的一路加法输入端,目标电压采样信号vsamp经过第十三电阻r13和第四运放u4的跟随,作为加减法电路的另一路加法输入端,目标输入信号vin经过第二运放u2的跟随,作为加减法电路的减法输入端,这样第八电阻r8、第九电阻r9、第十电阻r10、第十一电阻r11和第三运放u3就组成了一个加减法电路,该加减法电路的输出信号经过第十二电阻r12会直接接入到pwm电路中。

99.3、pwm电路

100.pwm电路的作用是用于接收输入控制电路所输出的控制信号,并根据输入控制电路的控制信号输出相应的脉冲信号来控制dcdc降压电路中mos管的导通与截止。

101.由于pwm芯片为pwm电路的核心,所以,当pwm芯片vfb端的输入电压大于等于2.5v时,ic芯片处于截止状态,也即,整个pwm电路都没有信号输出;当pwm芯片vfb端的输入电压小于2.5v时,ic芯片的drv端输出脉冲宽度可以调节的脉冲信号,并且,该脉冲信号的宽度会随着pwm芯片vfb端输入电压的变化而变化。具体而言,pwm芯片vfb端的输入电压越小,脉冲宽度的占空比就会越大,但其最大占空比会小于50%。

102.其中,pwm电路输出频率的表达式为:

103.f=1.72/(rt*rc);

104.式中,f为pwm电路的输出频率,rt等于第十五电阻r15的阻值、ct等于第七电容c7的容值。

105.在实际应用中,第十五电阻r15选用电阻值为10k、0805封装的高温贴片电阻;第七电容c7选用电容值为2200p、0805封装的高温贴片电容,所以,pwm电路输出信号的频率f约为80k。第十四电阻r14选用电阻值为51k、0805封装的高温贴片电阻,第十六电阻r16选用电阻值为1k、0805封装的高温贴片电阻,第十七电阻r17选用电阻值为100欧、0805封装的高温贴片电阻,第五电容c5选用容值为100p、0805封装的高温贴片电容,第六电容c6选用容值为0.1u、0805封装的高温贴片电容。

106.4、dcdc降压电路

107.dcdc降压电路会接收到90v的直流电压,并在pwm电路输出控制信号的作用下控制dcdc降压电路内部的pmos管不断导通和截止,然后,通过第二电感l2、第一钽电解电容c01和第二钽电解电容c02就会获取得到整个电压生成模块的输出电压。

108.可以理解的是,由于流过第二电感l2的电流不能突变、第一钽电解电容c01和第二钽电解电容c02两端的电压也不能突变,所以,dcdc降压电路的输出电压是一点一点增加的,其输出电压的增加过程不会发生突变。

109.当输出采样电路采样得到的目标电压采样信号vsamp与目标输入信号vin一致时,dcdc降压电路中第三nmos管n3处于截止状态,dcdc降压电路的输出电压不再增加;当负载消耗,使得输出采样电路采样得到的目标电压采样信号vsamp小于目标输入信号vin时,

dcdc降压电路中的第三nmos管n3处于导通状态,从而使得dcdc降压电路的输出电压增加;当输出采样电路采样得到的目标电压采样信号vsamp与目标输入信号vin一致时,dcdc降压电路中的第三nmos管n3又会处于截止状态。

110.由于pwm电路的输出频率f约为80k,频率很高,所以,pwm电路的输出纹波较小,其输出电压会较为稳定。在实际应用中,pmos管可以选用irf9640,第二电感l2可以选用1mh、1a的电感,第一钽电解电容c01和第二钽电解电容c02选用150u、耐压135v的高温钽电容,二极管d选用贴片整流二极管in4004。

111.此外,由于pwm电路的输出信号为正脉冲,当pwm电路处于截止状态时,pwm电路输出零电平,而dcdc降压电路中pmos管的源极与栅极之间的电压vsg大于5v时,pmos管又会导通,所以,为了保证电路的安全运行,还需要在dcdc降压电路中增加一个由第十七电阻r17、第十八电阻r18、第十九电阻r19和第三nmos管n3组成的反向电路。

112.当dcdc降压电路中第十七电阻r17所接收到的信号为零电平时,第三nmos管n3截止,pmos管p栅极和源极之间的电压均为90v,此时pmos管栅极与源极之间的压差为零,pmos管p处于截止状态;当dcdc降压电路中第十七电阻r17所接收到的信号为高电平时,第三nmos管n3导通,pmos管p栅极电压vg的表达式为:

113.vg=90*r18/(r18+r19);

114.式中,r18为第十八电阻r18的阻值,r19为第十九电阻r19的阻值。

115.在实际应用中,第十八电阻r18选用阻值为36k、1w的高温贴片电阻,第十九电阻r19选用阻值为5k、1w的高温贴片电阻,第十七电阻r17选用阻值为100欧、0805封装的高温贴片电阻,第三nmos管n3选用irf430。

116.显然,通过本技术所提供的电压生成模块,就可以让电压生成模块能够稳定的输出取值范围在0~80v的直流电压,同时在触发脉冲生成器的配合作用下就可以对中子发生器进行安全、可靠的高压控制。

117.对所公开的实施例的上述说明,使本领域技术人员能够实现或使用本实用新型。对这些实施例的多种修改对本领域技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本实用新型的精神或范围的情况下,在其它实施例中实现。因此,本实用新型将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1