静电抑制器的制作方法

1.本实用新型涉及静电抑制器。

背景技术:

2.当静电抑制器的静电电压超过触发电压(trigger voltage),其电阻值会急遽下降而导走电荷,进而达到保护电路的效果。因应着5g/6g无线传输与工业4.0的需求,静电抑制器朝向小尺寸的方向发展。小尺寸的组件可提高电路设计的灵活度,然而却伴随着耐静电能力降低的问题。此外,静电抑制器的电容会尽量设计地越低越好,以降低高速信号传输过程所造成的信号失真。

3.因此,如何在缩小组件尺寸的同时,降低静电抑制器的电容,为本实用新型欲解决的问题之一。

技术实现要素:

4.本公开的实施例涉及一种静电抑制器。所述静电抑制器包括衬底、传导层及保护层。所述传导层设置在所述衬底上并具有间隙。所述保护层设置在所述传导层上并在所述间隙上方界定气室。

5.本公开的实施例涉及一种静电抑制器。所述静电抑制器包括衬底及传导层。所述传导层设置在所述衬底上并具有间隙。所述传导层具有暴露到气体、空气或真空环境的部分。

附图说明

6.在下文具体实施方式中将参考随附图式讨论本公开实施例的各种方面,所述图式并非依比例绘制。在所述图式及具体实施方式中的技术特征以组件符号标记,所述组件符号是用以帮助理解本公开实施例的各种方面,但不限制本公开的权利要求书。在所述图式中:

7.图1a所示为根据本公开的部分实施例的静电抑制器的侧视图;

8.图1b所示为根据本公开的部分实施例的静电抑制器的局部侧视图;

9.图2a所示为根据本公开的部分实施例的静电抑制器的制造方法中的一或更多步骤中的俯视图;

10.图2b所示为根据本公开的部分实施例的静电抑制器的制造方法中的一或更多步骤中的侧视图;

11.图3a所示为根据本公开的部分实施例的静电抑制器的制造方法中的一或更多步骤中的俯视图;

12.图3b所示为根据本公开的部分实施例的静电抑制器的制造方法中的一或更多步骤中的侧视图;

13.图4a所示为根据本公开的部分实施例的静电抑制器的制造方法中的一或更多步

骤中的俯视图;

14.图4b所示为根据本公开的部分实施例的静电抑制器的制造方法中的一或更多步骤中的侧视图;

15.图5a所示为根据本公开的部分实施例的静电抑制器的制造方法中的一或更多步骤中的俯视图;

16.图5b所示为根据本公开的部分实施例的静电抑制器的制造方法中的一或更多步骤中的侧视图;

17.图6a所示为根据本公开的部分实施例的静电抑制器的制造方法中的一或更多步骤中的俯视图;

18.图6b所示为根据本公开的部分实施例的静电抑制器的制造方法中的一或更多步骤中的侧视图;

19.图7a所示为根据本公开的部分实施例的静电抑制器的制造方法中的一或更多步骤中的俯视图;及

20.图7b所示为根据本公开的部分实施例的静电抑制器的制造方法中的一或更多步骤中的侧视图。

具体实施方式

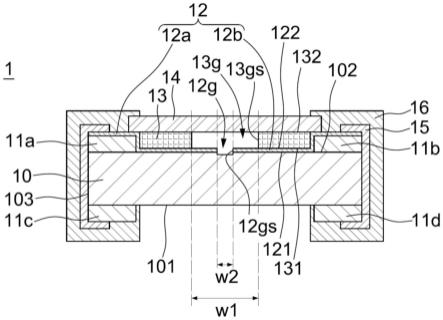

21.图1a所示为根据本公开的部分实施例的静电抑制器1的侧视图。静电抑制器1包括衬底10、电极11a、11b、11c、11d、传导层12、保护层13、保护层14、晶种层15及端电极16。

22.衬底10可包括(但不限于)硼硅酸盐玻璃(borophosphosilicate glass,bpsg)、经掺杂硅酸盐玻璃(undoped silicate glass,usg)、硅(silicon)、氧化硅(silicon oxide)、氮化硅(silicon nitride)、氮氧化硅(silicon oxynitride)、氧化铝(aluminium oxide)、氮化铝(aluminium nitride)、聚酰亚胺(polyimide,pi)、abf基材(ajinomoto build-up film,abf)、模塑胶(molding compounds)、预浸渍复合纤维(pre-impregnated composite fibers)(例如,预浸材料)、及其中的组合、或其它类似物。模塑胶的实例可包括(但不限于)环氧树脂(epoxy resin)(包含分散其中的填料(fillers))。预浸材料的实例可包括(但不限于)通过堆叠或层压(laminating)多个预浸渍材料及/或片料(sheets)所形成的多层结构。在一些实施例中,衬底10可包括(但不限于)电路板(如fr4)。

23.如图1a所示,衬底10可包括表面101、与表面101相对的表面102、及延伸在表面101与表面102之间的表面(或侧表面)103。

24.电极11a、11b、11c及11d可设置在衬底10的表面101及表面102的两端。在一些实施例中,电极11a、11b、11c及11d(但不限于)铜(cu)、金(au)、银(ag)或其它金属或合金。在一些实施例中,电极11a、11b、11c及11d的厚度可介于约0.2微米(micrometer,μm)到约30.0μm之间。然而,本公开不限于此。在一些实施例中,电极11a、11b、11c及11d可依装置规格或工艺要求而设置在其它位置,可具有任意数量,且可依装置规格或工艺要求而具有其它厚度。例如,在一些实施例中,电极可仅设置在衬底10的表面的两端。

25.传导层12可设置在衬底10及电极11a、11b上。在一些实施例中,传导层12可设置在衬底10的表面102上。在一些实施例中,传导层12可接触电极11a、电极11b及/或衬底10的表面102。在一些实施例中,传导层12可包括(但不限于)铜(cu)、金(au)、银(ag)、铝(al)、镍

(ni)、钛(ti)、钨(w)、铬(cr)、锡(sn)、或其它金属或合金。例如,在一些实施例中,合金可包括镍铬合金(如镍铬铝、镍铬硅)、镍铜合金(如镍铜锰)等。在一些实施例中,传导层12的厚度可介于约0.1μm到约5.0μm之间。然而,本公开不限于此。在一些实施例中,传导层12可依装置规格或工艺要求而具有其它厚度。

26.在一些实施例中,传导层12可包括表面121及与表面121相对的表面122。在一些实施例中,传导层12可具有间隙12g。在一些实施例中,间隙12g可穿透传导层12。例如,间隙12g可延伸在表面121与表面122之间。在一些实施例中,间隙12g可具有侧壁12gs。侧壁12gs可延伸在表面121与表面122之间。

27.在一些实施例中,衬底10的表面102可透过间隙12g而局部地从传导层12暴露出来。在一些实施例中,衬底10的表面102可透过间隙12g而暴露到气体、空气或真空环境。

28.在大致上平行于衬底10的表面102的方向上,间隙12g可具有宽度w2。在一些实施例中,间隙12g的宽度w2可小于约15.0μm。例如,间隙12g的宽度w2可介于约1.0μm到约15.0μm之间。然而,本公开不限于此。在一些实施例中,间隙12g可依装置规格或工艺要求而具有其它宽度。

29.在一些实施例中,传导层12可包括透过间隙12而彼此隔开的部分12a及部分12b。例如,部分12a可未接触部分12b。例如,部分12a可未连接部分12b。例如,从图4a的俯视图可见,间隙12g可将部分12a及部分12b隔开。在一些实施例中,当静电抑制器1的静电电压未超过触发电压(trigger voltage),部分12a及部分12b可彼此电性绝缘。在一些实施例中,间隙12g可具有如图4a所示的直线图案。然而,本公开不限于此。在一些实施例中,间隙12g可依装置规格或工艺要求而具有其它图案。

30.保护层13可设置在传导层12的表面122上。在一些实施例中,保护层13可接触传导层12的表面122。在一些实施例中,传导层12可局部地从保护层13暴露出来。例如,保护层13可未覆盖传导层12的至少一部分。在一些实施例中,保护层13可包括(但不限于)陶瓷材料、玻璃材料或高分子材料。在一些实施例中,保护层13可包括(但不限于)光致抗蚀剂,例如干膜光致抗蚀剂或其它玻璃转换温度(glass transition temperature,tg)与韧性高的材料。

31.在一些实施例中,保护层13可包括表面131及与表面131相对的表面132。在一些实施例中,表面131可接触传导层12的表面122。在一些实施例中,保护层13可具有侧壁13gs。侧壁13gs可延伸在表面131与表面132之间。在一些实施例中,侧壁13gs可为或可界定气室13g的侧壁。

32.保护层14可设置在保护层13上。在一些实施例中,保护层14可接触保护层13的表面132。在一些实施例中,保护层14未接触传导层12。在一些实施例中,保护层13可将保护层14与传导层12隔开。在一些实施例中,保护层13可位于保护层14与传导层12之间。

33.在一些实施例中,保护层14可包括(但不限于)陶瓷材料、玻璃材料或高分子材料。在一些实施例中,保护层14可包括(但不限于)光致抗蚀剂,例如湿膜光致抗蚀剂(或液态光致抗蚀剂)。在一些实施例中,保护层13与保护层14可具有相同的材料。在一些实施例中,保护层13与保护层14可具有不同的材料。在一些实施例中,保护层13与保护层14可在同一步骤中形成。例如,保护层13与保护层14可一体成形。

34.保护层13与保护层14可界定静电抑制器1的气室13g。气室13g中可含有气体、空气

或可经抽真空。气室13g中可位于间隙12g上方。气室13g与间隙12g可彼此气体流通。在本公开中,间隙12g形成在传导层12中,而气室13g是在传导层12上方。然而由于气室13g与间隙12g可彼此气体流通,因此还可将间隙12g与气室13g一起视为静电抑制器1的气室。在一些实施例中,静电抑制器1的气室为由衬底10、传导层12、保护层13及保护层14所围绕而成的内部空间。

35.在一些实施例中,衬底10的表面102可透过间隙12g而暴露到气室13g中的气体、空气或真空环境。在一些实施例中,保护层13可在工艺中界定气室13g的空间,以确保传导层12有足够的空间可以进行静电放电。在一些实施例中,保护层13可界定气室13g的侧壁13gs,而保护层14可界定气室13g的顶部。例如,保护层14可覆盖气室13g。

36.在一些实施例中,在大致上水平于衬底10的表面102的方向上,保护层13可界定气室13g的宽度w1。在一些实施例中,宽度w1可大于间隙12g的宽度w2。

37.晶种层15可设置在衬底10的两端且位于传导层12上。在一些实施例中,晶种层15可覆盖传导层12的表面122的一部分。

38.端电极16可设置在衬底10的两端且位于晶种层15上。在一些实施例中,晶种层15及端电极16可包括(但不限于)上述针对传导层12所列举的材料,在此不再赘述。

39.图1b所示为根据本公开的部分实施例的静电抑制器的局部侧视图。在一些实施例中,图1b所示的局部侧视图可为图1a的静电抑制器1的局部侧视图。在本文中,相同或相似的组件以相同的符号表示。

40.在一些实施例中,衬底10的表面102可具有部分102a、部分102b及部分102c。在一些实施例中,部分102a可相对于部分102c凸出。在一些实施例中,部分102c可相对于部分102a朝表面101的方向凹陷。在一些实施例中,部分102b可延伸在部分102a与部分102c之间。在一些实施例中,部分102b可大致上垂直于部分102a及/或部分102c。在一些实施例中,部分102c可透过间隙12g而暴露到气室13g中的气体、空气或真空环境。

41.在一些实施例中,传导层12的间隙12g可具有侧壁12gs。侧壁12gs可延伸在传导层12的表面121与表面122之间。在一些实施例中,侧壁12gs可暴露到气室13g中的气体、空气或真空环境。

42.在一些实施例中,氧化物12o可形成在间隙12g的侧壁12gs上。在一些实施例中,以激光蚀刻的方式移除传导层12所产生的热能可使传导层12氧化,而在传导层12的边缘处形成氧化物。例如,在一些实施例中,氧化物可包括传导层12的氧化物。在一些实施例中,氧化物可沿着间隙12g的侧壁12gs形成。在一些实施例中,氧化物12o可完全地或局部地覆盖侧壁12gs。在一些实施例中,氧化物12o可暴露到气室13g中的气体、空气或真空环境。在一些实施例中,氧化物12o可避免传导层12短路。

43.在一些实施例中,间隙12g可从传导层12向下凹陷到衬底10。在一些实施例中,间隙12g的侧壁12gs可与衬底10的表面102的部分102b大致上共平面。在一些实施例中,间隙12g的侧壁12gs与衬底10的表面102的部分102b可形成连续的表面。

44.根据本公开的部分实施例,本公开提供的静电抑制器1具有气室13g。由于气室13g的介电常数低于高分子材料,相较于不包括气室13g的静电抑制器(其传导层通常由高分子材料覆盖),本公开提供的静电抑制器1可达到更低的电容值。例如,当静电抑制器1的静电电压超过触发电压,气室13g中可产生等离子体,使电荷能被导走,达到以空气放电的方式

抑制静电放电冲击的效果。

45.相较于不包括气室13g的静电抑制器,当受到静电放电冲击时,静电抑制器1的触发电压较低、箝制电压(clamping voltage)较低、动态电阻远低于受保护的电路并且具有较快的反应时间。

46.根据本公开的部分实施例,本公开提供的静电抑制器1的电容值可低于0.05皮法(picofarad,pf),触发电压可低于450伏特(volts,v),且箝制电压低于约35伏特(volts,v)。在正常运作的工作电压(working voltage)下,漏电流(leakage current)可低于约0.1微安(microampere,μa)。

47.此外,本公开的实施例提供工艺方法(详述于图2a到图7b),是透过溅镀(sputtering)(如真空溅镀)的方式形成传导层12,并以激光蚀刻的方式在传导层12中形成间隙12g。以溅镀的方式形成传导层12,可精准地控制传导层12的厚度。以溅镀的方式形成传导层12可不受工艺材料的限制,因此材料的选择性较高。根据本公开的部分实施例,溅镀的材料可选用铜(cu)、金(au)、银(ag)、铝(al)、镍(ni)、钛(ti)、钨(w)、铬(cr)、锡(sn)、镍铬合金、镍铜合金等,以达到前述较低的触发电压与箝制电压。

48.另外,相较于黄光光刻工艺,使用激光蚀刻可增加传导层12尺寸(如宽度w2)的精准度,提升产品的稳定度,进而达到控制触发电压并减少漏电流的效果。此外,使用激光蚀刻可同时在传导层12的边缘处形成氧化物12o,进而避免传导层12短路。根据本公开的部分实施例,传导层12尺寸的误差小于等于约

±

2%。

49.再者,根据本公开的部分实施例,本公开的实施例提供工艺方法导入合金热处理技术(例如对传导层12进行退火处理),以提升组件信赖性,并通过iec(international electoral commission)所制定的iec61000-4-2level 4标准。

50.图2a及图2b到图7a及图7b所示为根据本公开的部分实施例的发火电阻的制造方法。在一些实施例中,图2b、图3b、图4b、图5b、图6b及图7b分别为图2a、图3a、图4a、图5a、图6a及图7a的结构沿切线aa'截面的剖面图。根据本公开的部分实施例,图2a及图2b到图7a及图7b所公开的制造方法可用以制造如图1a与图1b所示的静电抑制器1。根据本公开的部分实施例,图2a及图2b到图7a及图7b所公开的制造方法还可用以制造其它静电抑制器。

51.参照图2a及图2b,提供衬底10,并在衬底10上形成电极11a、11b、11c及11d。在一些实施例中,可以激光切割的方式在衬底10中形成切割道。在一些实施例中,切割道的深度可占衬底10的厚度约20%到约60%的比例。

52.在一些实施例中,电极11a、11b、11c及11d可通过溅镀、无电电镀(electroless plating)、电镀(plating)、印刷(printing)或其它可行的方式而形成。在一些实施例中,如图2b所示,电极11a、11b、11c及11d可设置在衬底10的表面101及表面102的两端。

53.参照图3a及图3b,在衬底10上形成传导层12。传导层12可覆盖衬底10及电极11a及11b。在一些实施例中,传导层12可保型地(comformally)形成在衬底10及电极11a及11b上。在一些实施例中,传导层12可通过溅镀(如真空溅镀)的方式而形成。在一些实施例中,部分的衬底10及电极11a及11b可从传导层12暴露出来。然而在其它实施例中,衬底10及电极11a及11b可完全被传导层12所覆盖。

54.参照图4a及图4b,在传导层12中形成间隙12g。在一些实施例中,衬底10的表面102可透过间隙12g而局部地从传导层12暴露出来。在一些实施例中,间隙12g从传导层12向下

凹陷到衬底10。在一些实施例中,间隙12g可经由激光蚀刻的方式移除部分的传导层12(或图案化传导层12)及/或衬底10而形成。在一些实施例中,由于激光蚀刻可形成大致上平整的切割面,因此间隙12g可具有大致上平整的侧壁。如图4b所示,衬底10的表面102的部分102b及间隙12g的侧壁12gs可大致上共平面。在一些实施例中,衬底10的表面102的部分102b及间隙12g的侧壁12gs可形成连续的表面。

55.在一些实施例中,以激光蚀刻的方式移除传导层12所产生的热能可使传导层12氧化,而在传导层12的边缘处形成氧化物(如图1b的氧化物12o)。例如,在一些实施例中,氧化物可包括传导层12的氧化物。在一些实施例中,氧化物可沿着间隙12g的侧壁12gs形成。在一些实施例中,氧化物可完全地或局部地覆盖侧壁12gs。

56.在其它实施例中,传导层12的图案还可以干式蚀刻(dry etching)、离子撞击(ion bumping)、曝光显影、印刷时遮蔽图案或其它可行的方式形成。

57.例如,以曝光显影方式定义传导层12的图案,透过变更传导层12的图案调整组件特性,并经溅镀传导层12后,依传导层12的材料种类选择以剥离或蚀刻方式制作出间隙12g。

58.例如,以印刷遮蔽涂料方式定义传导层12的图案,并经溅镀传导层12后,将遮蔽涂料剥离,以产生间隙12g。

59.例如,以激光蚀刻结合可行的其它蚀刻方式图案化传导层12,并不限于本公开中所列举的方式。

60.在形成间隙12g之后,传导层12的部分12a与部分12b分离。

61.在一些实施例中,可进一步对传导层12进行退火处理,以提升稳定度。

62.参照图5a及图5b,在传导层12上形成保护层13。在一些实施例中,可透过涂布(coating)、层压(lamination)、或其它适合的方式形成保护层13。在一些实施例中,传导层12可局部地从保护层13暴露出来。例如,保护层13可未覆盖传导层12的至少一部分。例如,如图5a所示,保护层13可围绕间隙12g的四周。

63.在一些实施例中,可利用黄光光刻工艺图案化保护层13而形成保护层13的侧壁13gs。在一些实施例中,保护层13可界定接下来形成的气室13g的空间,以确保传导层12有足够的空间可以进行静电放电。在一些实施例中,保护层13可界定接下来形成的气室13g的宽度w1。

64.参照图6a及图6b,在保护层13上形成保护层14。在一些实施例中,可透过涂布、层压、或其它适合的方式形成保护层14。在一些实施例中,保护层14可覆盖气室13g。在一些实施例中,保护层14未接触传导层12。

65.在其它实施例中,保护层13及保护层14可一体成形。在其它实施例中,保护层13可预先成行后透过自动化设备粘着在保护层13上。

66.参照图7a及图7b,在传导层12上形成晶种层15覆盖传导层13的一部分。在一些实施例中,晶种层15可通过溅射nicr、nicrsi、nicrcu、钛及铜(ti/cu)或tiw而形成。在一些实施例中,晶种层15可通过端涂银或铜而形成。在一些实施例中,在形成晶种层15之前,可将衬底10沿着经由激光划线而形成的切割道而分离成多个独立的组件,以露出衬底10的表面103。因此,在一些实施例中,晶种层15可形成在衬底10的表面103。

67.接下来,在衬底10的两端形成端电极16。在一些实施例中,端电极16可通过电镀

ni、cu、ag、au或其它金属而形成。在一些实施例中,端电极16可通过无电电镀ni、pb或其它金属而形成。在一些实施例中,端电极16可通过印刷cu、ag、au或其它金属而形成。在一些实施例中,透过图2a及图2b到图7a及图7b所示方法而形成的静电抑制器可与图1a所示的静电抑制器1相同。

68.在本公开中讨论的结构及方法的实施例,并不限于具体实施方式及随附图式中描述及绘示的构造或布置,而是能以各种方式实践或执行。

69.此外,在本公开中使用的措辞及术语是出于描述的目的且不应视为限制。例如,单数形式或复数形式的措辞不意在限制当前所公开的结构及方法。本公开中使用的“包含”、“包括”、“具有”、“含有”、“涉及”等涵盖在其后列出的项目、其等效物、及额外项目。本公开中使用的“或”可视为指示所描述的一个以上的项目中的任一者。前及后、左及右、顶部及底部、上部及下部、及垂直及水平等意在方便描述,而不应视为将结构及方法限制于一个位置、空间、或方向。

70.因此,本实用新型技术领域的一般技术人员根据本公开中所载的特定实施例应可想到各种更改、修改、及改进。这些更改、修改、及改进仍落入本公开的范围内。

71.符号说明

72.1:静电抑制器

73.10:衬底

74.11a:电极

75.11b:电极

76.11c:电极

77.11d:电极

78.12:传导层

79.12a:部分

80.12b:部分

81.12g:间隙

82.12gs:侧壁

83.12o:氧化物

84.13:保护层

85.13g:气室

86.13gs:侧壁

87.14:保护层

88.15:晶种层

89.16:端电极

90.101:表面

91.102:表面

92.102a:部分

93.102b:部分

94.102c:部分

95.103:表面

96.121:表面

97.122:表面

98.131:表面

99.132:表面

100.aa':切线

101.w1:宽度

102.w2:宽度。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1