三维存储器及制造三维存储器的方法与流程

本发明涉及半导体器件及其制造方法,尤其是包括储器阵列芯片和外围电路芯片的三维存储器及其制造方法。

背景技术:

1、随着三维存储器集成程度越来越高,三维存储器已经从32层发展到64层甚至更高的层数,随着层数的增加,存储阵列的复杂度增加,这导致所对应的外围电路的设计复杂度增加。一般而言,存储密度的增加将导致在有限面积内设计外围电路的工艺难度增大而使得外围电路的面积增大。

技术实现思路

1、本发明提供包括外围电路芯片的三维存储器及其制造方法,其可至少部分地解决现有技术中存在的上述问题。

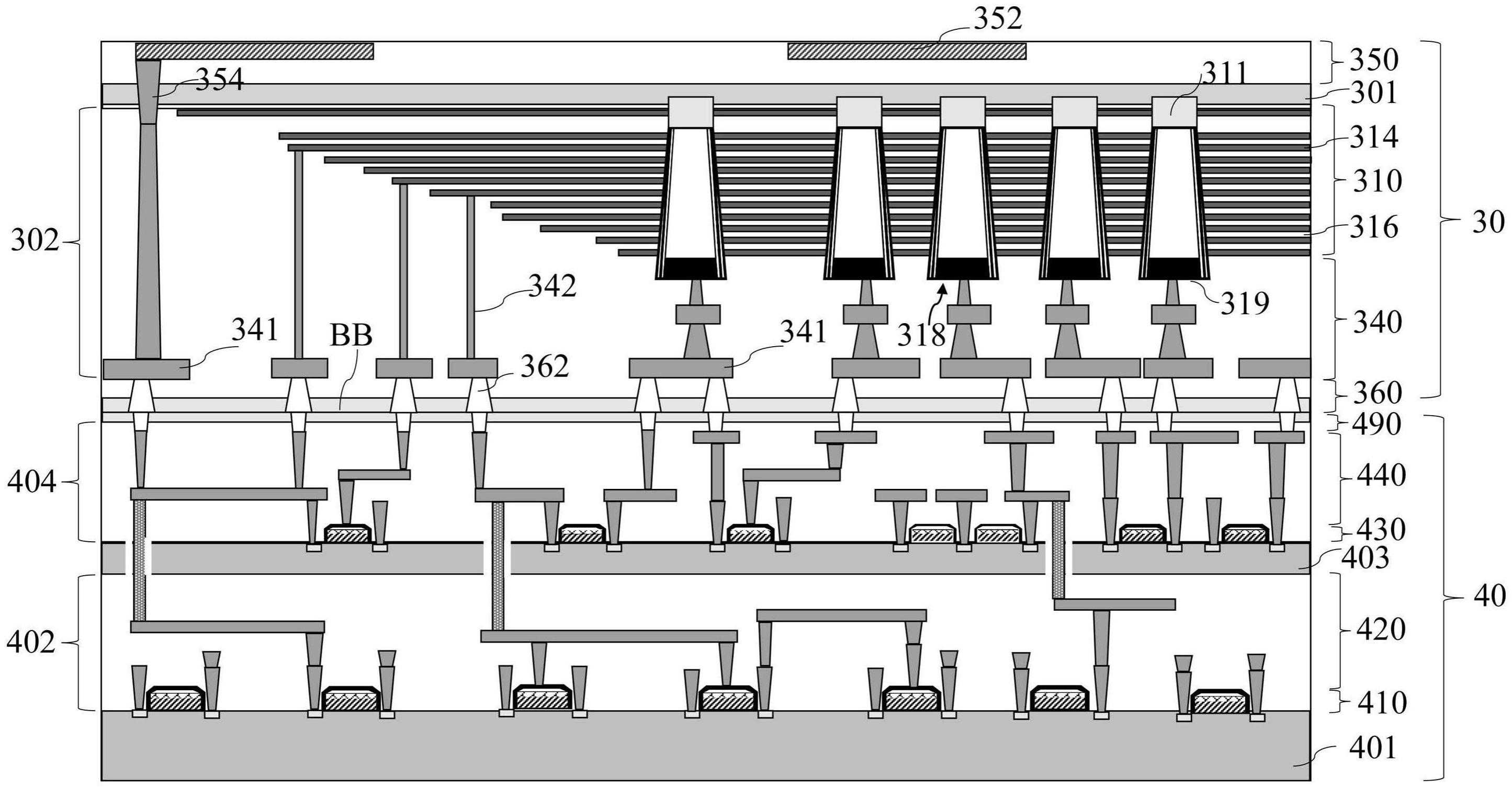

2、根据本发明的一方面,提供了包括外围电路芯片的三维存储器,其中,外围电路芯片包括:第一衬底;第一电路元件层,设置在第一衬底上,并且包括第一器件层和第一连接层,第一连接层用于第一器件层的信号传输;第二衬底,设置在第一电路元件层上;以及第二电路元件层,设置在第二衬底上,并且包括第二器件层和第二连接层,第二连接层用于第二器件层的信号传输。

3、在实施方式中,第一器件层可包括多个第一晶体管,第二器件层包括多个第二晶体管,并且第一晶体管的工作电压可大于第二晶体管的工作电压。

4、在实施方式中,第一晶体管的尺寸可大于第二晶体管的尺寸。

5、在实施方式中,第一连接层和第二连接层中的每个可包括导电材料,并且第一连接层的导电材料的熔点可大于或等于第二连接层的导电材料的熔点。

6、在实施方式中,第一连接层的导电材料可为wsi或tisi,并且第二连接层的导电材料可为tisi或cosi。

7、在实施方式中,外围电路芯片还可包括:第三衬底,设置在第二电路元件层上;第三电路元件层,设置在第三衬底上,并且包括第三器件层和第三连接层,第三连接层用于第三器件层的信号传输。

8、在实施方式中,外围电路芯片还可包括第一互连层、第二互连层和第三互连层中的至少一个。第一互连层可将第一连接层与第二连接层电连接以用于第一器件层和第二器件层之间的信号传输。第二互连层可将第三连接层与第一连接层和第二连接层中的一个连接层电连接,以用于第三连接层和一个连接层之间的信号传输。第三互连层可将第三连接层与第一连接层和第二连接层中的另一个连接层电连接,以用于第三连接层与另一个连接层之间的信号传输。

9、在实施方式中,第一互连层、第二互连层和第三互连层中的至少之一可包括w。

10、在实施方式中,第一器件层可包括多个第一晶体管,第二器件层包括多个第二晶体管,第三器件层可包括多个第三晶体管。在实施方式中,至少一个第一晶体管的工作电压可大于至少一个第二晶体管的工作电压,并且至少一个第二晶体管的工作电压可大于至少一个第三晶体管的工作电压。

11、在实施方式中,至少一个第一晶体管的尺寸可大于至少一个第二晶体管的尺寸,并且至少一个第二晶体管的尺寸可大于至少一个第三晶体管的尺寸。

12、在实施方式中,第一晶体管、第二晶体管和第三晶体管中的至少之一可为金属氧化物半导体场效应晶体管。

13、在实施方式中,第一连接层、第二连接层和第三连接层中的每个可包括导电材料,第一连接层的导电材料的熔点可大于或等于第二连接层的导电材料的熔点,并且第二连接层的导电材料的熔点可大于或等于第三连接层的导电材料的熔点。

14、在实施方式中,第一连接层的导电材料可为wsi或tisi,第二连接层的导电材料可为tisi或cosi,并且第三连接层的导电材料可为nisi。

15、在实施方式中,第一连接层还可包括第一电介质层,第一电介质层用于电隔离第一连接层的导电材料,第二连接层还可包括第二电介质层,第二电介质层用于电隔离第二连接层的导电材料,并且第三连接层还可包括第三电介质层,第三电介质层用于电隔离第三连接层的导电材料。

16、在实施方式中,三维存储器还包括存储阵列芯片,其中,存储阵列芯片可包括存储阵列层和设置在存储阵列层上的第一键合层,存储阵列层包括设置在叠层结构中的多个存储串,第一键合层用于与外围电路芯片中的第二键合层键合。

17、在实施方式中,第二键合层可设置在第二电路元件层上。

18、根据本发明的另一方面,提供了用于制造三维存储器的方法,该方法包括基于第一衬底形成外围电路芯片,包括:在第一衬底上依次形成第一器件层和用于第一器件层的信号传输的第一连接层;在第一连接层上形成第二衬底,并在第二衬底上依次形成第二器件层和用于第二器件层的信号传输第二连接层;以及在第二连接层上形成具有导电触点的键合层。

19、在实施方式中,第一器件层可包括多个第一晶体管,第二器件层可包括多个第二晶体管,并且至少一个第一晶体管的工作电压可大于至少一个第二晶体管的工作电压。

20、在实施方式中,至少一个第一晶体管的尺寸可大于至少一个第二晶体管的尺寸。

21、在实施方式中,形成第一连接层可包括:在第一器件层上形成第一电介质层;在第一电介质层中利用第一导电材料形成用于信号传输的导电布线和导电触点。在实施方式中,形成第二连接层可包括:在第二器件层上形成第二电介质层;在第二电介质层中利用第二导电材料形成用于信号传输的导电布线和导电触点。在实施方式中,第一导电材料的熔点大于或等于第二导电材料的熔点。

22、在实施方式中,该方法还可包括:在第二连接层上形成第三衬底,并在第三衬底上依次形成第三器件层和用于第三器件层的信号传输第三连接层,其中,上述键合层形成在第三连接层上。

23、在实施方式中,该方法还可包括形成第一互连层、第二互连层和第三互连层中的至少之一,其中,第一互连层可将第一连接层与第二连接层电连接,第二互连层可将第二连接层和第三连接层电连接,第三互连层可将第一连接层和第三连接层电连接;以及在第三连接层上形成具有导电触点的键合层。

24、在实施方式中,第一器件层可包括多个第一晶体管,第二器件层可包括多个第二晶体管,第三器件层可包括多个第三晶体管。在实施方式中,至少一个第一晶体管的工作电压可大于至少一个第二晶体管的工作电压,并且至少一个第二晶体管的工作电压可大于至少一个第三晶体管的工作电压。

25、在实施方式中,至少一个第一晶体管的尺寸可大于至少一个第二晶体管的尺寸,并且至少一个第二晶体管的尺寸可大于至少一个第三晶体管的尺寸。

26、在实施方式中,形成第一连接层可包括:在第一器件层上形成第一电介质层;在第一电介质层中利用第一导电材料形成用于信号传输的导电布线和导电触点。在实施方式中,形成第二连接层可包括:在第二器件层上形成第二电介质层;在第二电介质层中利用第二导电材料形成用于信号传输的导电布线和导电触点。在实施方式中,形成第三连接层可包括:在第三器件层上形成第三电介质层;在第三电介质层中利用第三导电材料形成用于信号传输的导电布线和导电触点。在实施方式中,第一导电层的导电材料的熔点可大于或等于第二导电层的导电材料的熔点,并且第二导电层的导电材料的熔点可大于或等于第三导电层的导电材料的熔点。

27、根据本发明的又一方面,提供了另一种三维存储器,该三维存储器包括外围电路芯片和存储阵列芯片,外围电路芯片包括:第一衬底;第一电路元件层,设置在第一衬底上,并且包括第一器件层,第一器件层包括多个高压晶体管;第二衬底,设置在第一电路元件层上,且第二衬底与第一电路元件层接触;以及第二电路元件层,设置在第二衬底上,并且包括第二器件层,第二器件层包括多个低压晶体管;存储阵列芯片设置在第二电路元件层上。

28、上述实施方案的三维存储器及制造方法,由于外围电路芯片中的器件可以设置在不同的衬底上,可以有效地减小外围电路芯片的面积,有利于三维存储器存储密度的增加。同时,由于不同工作电压的器件形成在不同的衬底上,可以简化制备工艺并提高器件的稳定性。

- 还没有人留言评论。精彩留言会获得点赞!