LDPC码的译码方法及装置、可读存储介质、终端与流程

本发明涉及计算机,尤其涉及一种ldpc码的译码方法及装置、可读存储介质、终端。

背景技术:

1、低密度奇偶校验(lowdensity parity check,ldpc)是一种通信编码方式。在5g通信领域中,ldpc码在译码算法上有着显著的优势,ldpc基于稀疏校验矩阵,该矩阵中多数单元为0,仅有少数单元为1,这使得在译码过程中可以减少大量的计算量,提高译码效率;同时,稀疏矩阵使连续突发的错误对译码影响差距不大;该算法有很好的并行性,硬件实现复杂度低。

2、在ldpc译码过程中,首先获取每单元的对数似然比(log-likelihood ratio,llr)信息,然后迭代更新以修正单元错误,迭代过程中变量节点的软判决信息的绝对值越大,表示可靠性越高。

3、然而在现有的ldpc译码过程中,采用缓存器存储中间计算数据,而每次从缓存器中读取需要的数据会固定需要1个时钟(clock,clk),由于中间计算数据较多,导致读取时长过长,译码效率较低。

4、亟需一种ldpc码的译码方法,提高译码效率。

技术实现思路

1、本发明解决的技术问题是提供一种ldpc码的译码方法及装置、可读存储介质、终端,用于提高译码效率。

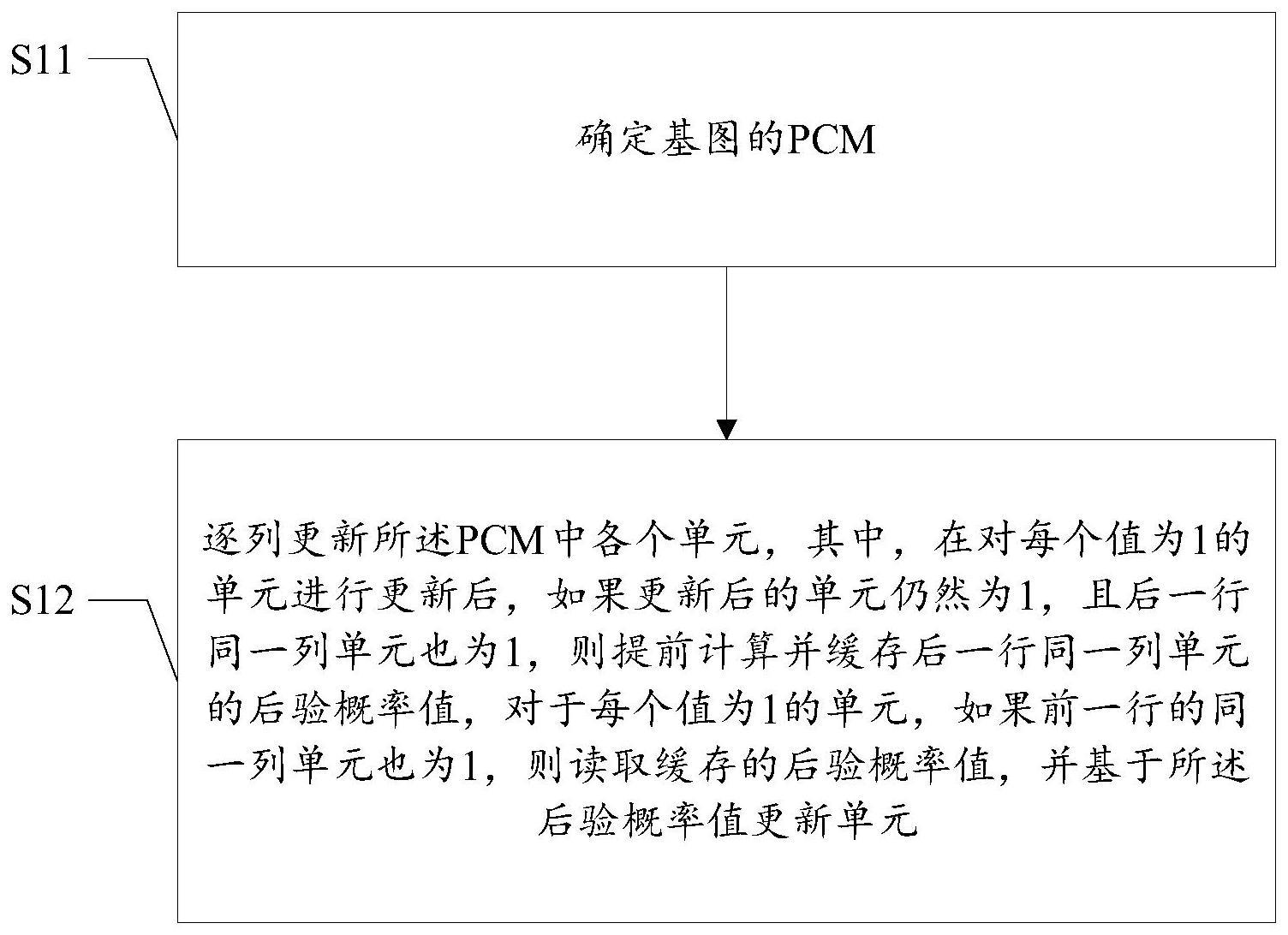

2、为解决上述技术问题,本发明实施例提供一种ldpc码的译码方法,包括:确定基图的pcm;逐列更新所述pcm中各个单元;其中,在对每个值为1的单元进行更新后,如果更新后的单元仍然为1,且后一行同一列单元也为1,则提前计算并缓存后一行同一列单元的后验概率值;对于每个值为1的单元,如果前一行的同一列单元也为1,则读取缓存的后验概率值,并基于所述后验概率值更新单元。

3、可选的,所述提前计算并缓存后一行同一列单元的后验概率值,包括:基于当前单元的校验节点r值提前计算后一行同一列单元的校验节点r值,然后在缓存中采用后一行同一列单元的校验节点r值覆盖当前单元的校验节点r值,然后提前计算并缓存后一行同一列单元的后验概率值。

4、可选的,所述基于当前单元的校验节点r值提前计算后一行同一列单元的校验节点r值,包括:根据当前单元的后验概率值与当前单元的校验节点r值确定后一行同一列单元的信息节点l值;确定后一行同一列单元的除当前信息节点之外的所有信息节点l值的绝对值的最小值与预设的偏移量的差值,并在所述差值大于0时,采用所述差值、预设的归一化因子以及后一行同一列单元的除当前信息节点之外的所有信息节点l值的符号的乘积这三者之积作为后一行同一列单元的校验节点r值。

5、可选的,采用下述公式,计算后一行同一列单元的校验节点r值:

6、

7、

8、其中,k用于表示分层译码的第k次迭代,t用于表示分层译码的第t层,c用于表示第c个校验节点,v用于表示第v个信息节点,n(c)\v用于表示在二部图中除去信息节点v之外的与校验节点c相连的信息节点集合,n用于表示信息节点集合n(c)\v中的第n个信息节点,用于表示信息节点v向校验节点c传递信息的信息节点l值,用于表示校验节点c向信息节点v传递信息的校验节点r值,用于表示信息节点v的后验概率值,min()用于表示最小值函数,max()用于表示最大值函数,α用于表示归一化因子,β用于表示偏移量。

9、可选的,所述提前计算并缓存后一行同一列单元的后验概率值,包括:采用后一行同一列单元的信息节点l值与后一行同一列单元的校验节点r值的差值作为所述后一行同一列单元的后验概率值。

10、可选的,在根据当前单元的后验概率值与当前单元的校验节点r值确定后一行同一列单元的信息节点l值之后,以及确定后一行同一列单元的除当前信息节点之外的所有信息节点l值的绝对值的最小值与预设的偏移量的差值之前,所述方法还包括:确定后一行同一列单元的除当前信息节点之外的所有信息节点l值的绝对值的最小值;在缓存中采用后一行同一列单元的信息节点l值覆盖当前单元的信息节点l值。

11、可选的,在同一个clk,能够既对在先单元的后验概率值进行计算,又对在后单元的校验节点r值进行计算;其中,在后单元的启动计算步骤不需等在先单元完成后验概率值的计算。

12、可选的,所述pcm中包含全零子矩阵;所述逐列更新所述pcm中各个单元,包括:不对所述全零子矩阵中的单元进行更新。

13、可选的,所述方法还包括:对于每个单元,采用校验节点处理的总时长、奇偶检验处理时长以及ldpc译码模块内部数据搬移及输出延迟时长的和值,作为ldpc译码的总时长;其中,所述校验节点处理的总时长用于表示每个单元各次迭代的时长之和与处理单个移位因子的llr所需要的时长的和值,所述奇偶检验处理时长用于表示移位因子数量个1比特数据相加需要的时钟数与预设时钟数的和值。

14、为解决上述技术问题,本发明实施例提供一种ldpc码的译码装置,包括:pcm确定模块,用于确定基图的pcm;单元更新模块,用于逐列更新所述pcm中各个单元;其中,在对每个值为1的单元进行更新后,如果更新后的单元仍然为1,且后一行同一列单元也为1,则提前计算并缓存后一行同一列单元的后验概率值;对于每个值为1的单元,如果前一行的同一列单元也为1,则读取缓存的后验概率值,并基于所述后验概率值更新单元。

15、为解决上述技术问题,本发明实施例提供一种可读存储介质,其上存储有计算机程序,所述计算机程序被处理器运行时执行上述ldpc码的译码方法的步骤。

16、为解决上述技术问题,本发明实施例提供一种终端,包括存储器和处理器,所述存储器上存储有能够在所述处理器上运行的计算机程序,所述处理器运行所述计算机程序时执行上述ldpc码的译码方法的步骤。

17、与现有技术相比,本发明实施例的技术方案具有以下有益效果:

18、在本发明实施例中,在逐列更新所述pcm中各个单元的过程中,通过判断是否出现更新后的单元仍然为1,且后一行同一列单元也为1的情况,并在该情况下提前计算并缓存后一行同一列单元的后验概率值,相比于现有技术中计算后一行同一列单元时还需要先耗费一个或多个时钟对之前缓存的中间数据进行读取,采用本发明实施例的方案,可以利用计算得到的中间数据直接对后一行同一列单元进行提前计算,节省读取中间数据的时间,有效提高译码效率。进一步地,通过设置前一行的同一列单元为1且当前单元也为1的情况下,才读取缓存的后验概率值,可以确保前一行的同一列单元是经过最新计算后仍然为1的,也即前一行的同一列单元的后验概率值是新计算得到的,从而避免误将历史缓存数据当作最新的计算数据的情况,对数据的可用性进行有效判断。

19、进一步,基于当前单元的校验节点r值提前计算后一行同一列单元的校验节点r值,然后在缓存中采用后一行同一列单元的校验节点r值覆盖当前单元的校验节点r值,然后提前计算并缓存后一行同一列单元的后验概率值,可以利用计算得到的中间数据直接对后一行同一列单元的r值进行提前计算,从而节省读取中间数据的时间,有效提高译码效率;还可以在提前计算并得到r值之后,覆盖当前单元的r值,从而减少缓存的数据,降低缓存成本。进一步地,在同一个clk,能够既对在先单元的后验概率值进行计算,又对在后单元的校验节点r值进行计算的场景中,还可以通过提前计算并覆盖r值,减少后一行同一列单元计算过程中的一轮r值计算,有助于降低在同一个clk同时读写多个r值的概率,考虑到在同一个clk对符号缓存的不同地址的同时读或写操作,容易产生缓存数据读取冲突,采用本发明实施例中的方案,可以通过降低在同一个clk同时读写多个r值的概率,有效改善缓存数据读取冲突的问题。

20、进一步,根据当前单元的后验概率值与当前单元的校验节点r值确定后一行同一列单元的信息节点l值;确定后一行同一列单元的除当前信息节点之外的所有信息节点l值的绝对值的最小值与预设的偏移量的差值,并在所述差值大于0时,采用所述差值、预设的归一化因子以及后一行同一列单元的除当前信息节点之外的所有信息节点l值的符号的乘积这三者之积作为后一行同一列单元的校验节点r值。采用上述改进后的r值计算方法,可以通过设置偏移量β提高r值计算结果的可调节性和灵活性,通过设置最大值函数max(),可以对除当前信息节点之外的所有信息节点l值的绝对值的最小值进行筛选,即仅最小值与预设的偏移量的差值大于0的情况下才将计算结果作为r值,进行后续操作,有效提高r值确定的准确性和有效性。

21、进一步,确定后一行同一列单元的除当前信息节点之外的所有信息节点l值的绝对值的最小值;在缓存中采用后一行同一列单元的信息节点l值覆盖当前单元的信息节点l值;可以利用计算得到的中间数据提前对后一行同一列单元的除当前信息节点之外的所有信息节点l值的绝对值的最小值进行计算,从而节省读取中间数据的时间,并在计算后一行同一列单元的r值时,通过提前存入的最小值直接进行计算,有效提高译码效率;还可以在提前确定后一行同一列单元的信息节点l值之后,覆盖当前单元的l值,从而减少缓存的数据,降低缓存成本。进一步地,在同一个clk,能够既对在先单元的后验概率值进行计算,又对在后单元的校验节点r值进行计算的场景中,还可以通过提前计算并覆盖l值,减少后一行同一列单元计算过程中的一轮l值计算,有助于降低在同一个clk同时读写多个l值的概率,考虑到在同一个clk对符号缓存的不同地址的同时读或写操作,容易产生缓存数据读取冲突,采用本发明实施例中的方案,可以通过降低在同一个clk同时读写多个l值的概率,有效改善缓存数据读取冲突的问题。

22、进一步,在同一个clk,能够既对在先单元的后验概率值进行计算,又对在后单元的校验节点r值进行计算;其中,在后单元的启动计算步骤不需等在先单元完成后验概率值的计算,可以采用滚动式跟进的计算方法,有效减少总的等待时长,有利于提高整体的译码效率。进一步地,由于本发明实施例中采用了提前计算并缓存后一行同一列单元的后验概率值的方法,使得在滚动式跟进的计算方法中,降低了在同一个clk对符号缓存的不同地址的同时读或写操作,进而产生缓存数据读取冲突的概率,有效提高上述滚动式跟进的计算方案的可实施性。更进一步地,在本发明实施例的一种具体实施方式中,还采用后一行同一列单元的校验节点r值覆盖当前单元的校验节点r值,和/或,采用后一行同一列单元的信息节点l值覆盖当前单元的信息节点l值,从而进一步显著降低了在同一个clk对符号缓存的不同地址的同时读或写操作,进而产生缓存数据读取冲突的概率,进一步增强滚动式跟进的计算方案的可实施性。

23、进一步,所述pcm中包含全零子矩阵;不对所述全零子矩阵中的单元进行更新,从而可以跳过对全零子矩阵的运算,进一步提高译码效率。

24、进一步,对于每个单元,采用校验节点处理的总时长、奇偶检验处理时长以及ldpc译码模块内部数据搬移及输出延迟时长的和值,作为ldpc译码的总时长,从而可以在本发明实施例中采用一项或多项提高译码效率的技术手段(提前计算并缓存后一行同一列单元的后验概率值,r值覆盖,l值覆盖,滚动式跟进的计算方法等)的基础上,选择适当的时长子集计算总时长,还可以根据计算得到的总时长对上述各种技术手段进行反馈,还可以对上述各种技术手段进行改进,从而提高译码效率的监控有效性。

- 还没有人留言评论。精彩留言会获得点赞!