耗尽型晶体管的驱动电路的制作方法

本申请涉及半导体驱动,尤其涉及一种耗尽型晶体管的驱动电路。

背景技术:

1、使用第三代半导体材料,即,宽禁带半导体材料氮化镓(gan)制备的半导体器件具有更高的工作电压、更高的开关频率、更低的导通电阻等优势,并可与成本极低、技术成熟度极高的硅基半导体集成电路工艺相兼容,在新一代高频率、小尺寸的电力转换与管理系统、电动机车、工业电机等领域具有巨大的发展潜力。

2、氮化镓功率器件一般分为耗尽型(常开型)和增强型(常关型)两种。其中增强型器件的驱动电压范围窄,一般需要专门的驱动ic驱动,同时沟道电流较弱,应用上受到一定限制,耗尽型器件电流能力强,可靠性高,动态导通电阻更低,但需要负压进行关断。

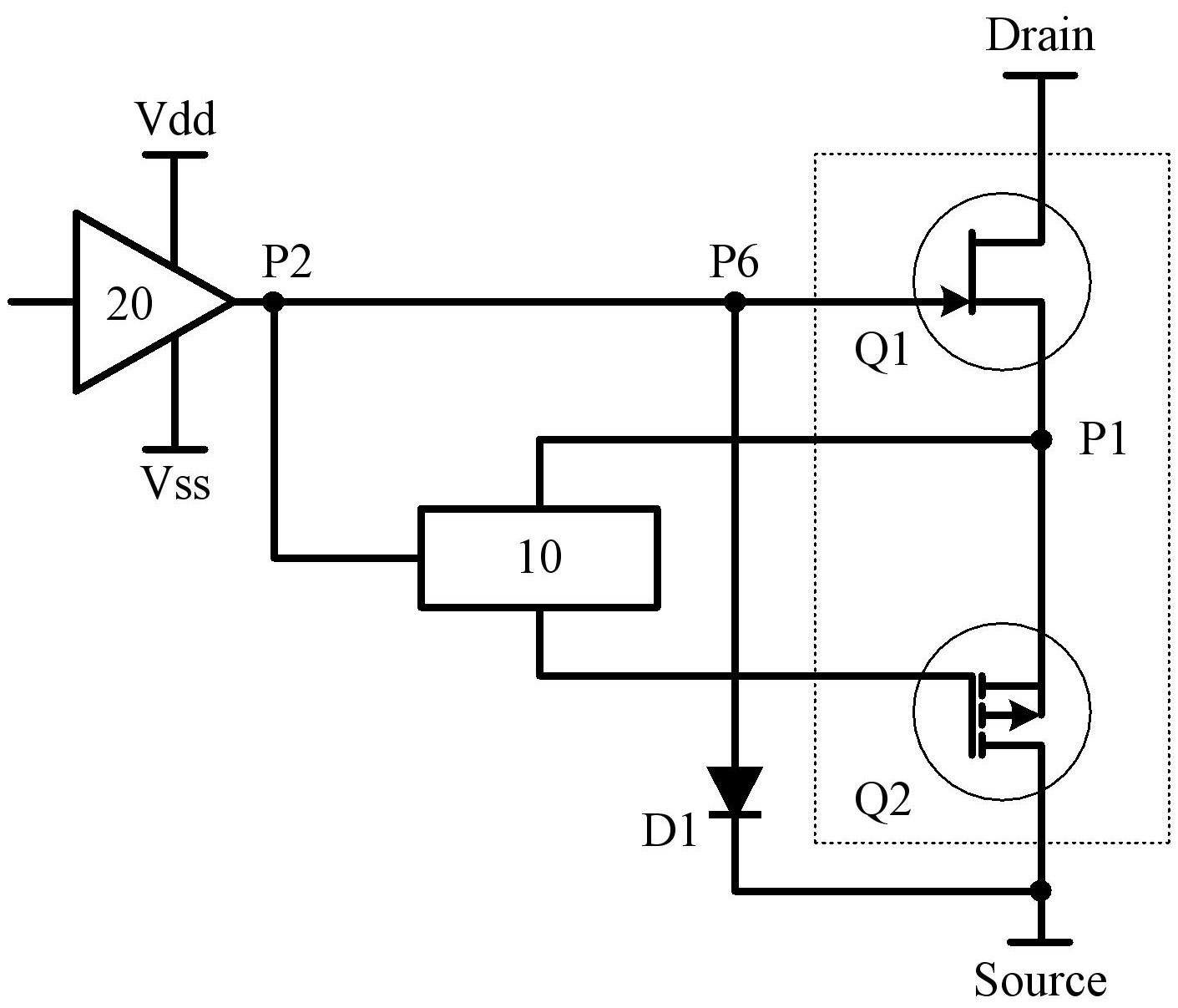

3、目前,氮化镓耗尽型器件通常与一个n沟道的低压mosfet进行级联,形成共源共栅型的常关器件,如图1所示。

4、在共源共栅级联型氮化镓器件中,耗尽型的氮化镓hemt器件k1的栅极与低压mosfet管k2的源极相连,通过驱动低压mos fet管k2的导通和关断,可以控制整个级联器件的导通和关断。但此结构存在以下几方面的问题:

5、(1)在共源共栅结构中,gan hemt的栅极直接连接至低压mosfet的源极,驱动器件的方式是通过驱动硅mos器件而不是直接驱动hemt器件,导致无法控制共源共栅器件的开关压摆率,容易引起系统emi问题。

6、(2)在驱动共源共栅级联器件关断时,由于hemt的栅源极电容与mos的漏源电容并联,必须将这两部分电容充电至hemt的阈值电压,因此器件具有更高组合的coss。同时由于给电容充电的电流来自器件本身,相比于低压的驱动电源回路对hemt的栅源极充电,功耗更大,在高频开关下会更明显。

7、(3)共源共栅结构的器件仍存在反向恢复问题。在第三象限导通时,低压mosfet的体二极管导通,克服反向恢复电荷的电流由系统中高压电源提供,增大了系统损耗。

8、(4)低压mosfet与氮化镓hemt结电容匹配难度大,匹配不当时会引起mosfet雪崩击穿,引入额外的开关损耗,特殊工况下也会引起中点电压震荡,严重时会导致器件失效。

技术实现思路

1、有鉴于此,本申请实施例至少提供一种耗尽型晶体管的驱动电路,以克服上述至少一种缺陷。

2、第一方面,本申请示例性实施例提供一种耗尽型晶体管的驱动电路,包括:mosfet,与耗尽型晶体管进行级联;开关控制模块,分别连接第一节点、第二节点和mosfet的栅极,第一节点在mosfet与耗尽型晶体管之间,第二节点为驱动电路的输出端;第一二极管,第一二极管的阳极连接到耗尽型晶体管的栅极,第一二极管的阴极连接到mosfet的漏极;其中,耗尽型晶体管的栅极连接到第二节点,被构造为在驱动电路输出的控制信号的作用下导通或者关断,开关控制模块被构造为在耗尽型晶体管的工作期间控制mosfet持续导通。

3、在一可能实施方式中,耗尽型晶体管的工作期间包括驱动电路被启动、输出控制信号的阶段。

4、在一可能实施方式中,mosfet包括p型mosfet,p型mosfet的源极与耗尽型晶体管的源极连接,第一节点为p型mosfet的源极,其中,所述开关控制模块包括:储能子电路,分别连接第三节点和第四节点,第三节点在供电电源与第一节点之间,第四节点在驱动电路的输出端与mosfet的栅极之间,被构造为在第二节点处为高电平时,储存能量并向第四节点提供高电平以控制mosfet导通,在第二节点处为低电平时,通过释放储能子电路所储存的能量,向第四节点提供高电平以维持mosfet导通。

5、在一可能实施方式中,所述开关控制模块还包括:钳位子电路,分别连接第三节点和第四节点,被构造为在第二节点处无控制信号时,对第三节点和第四节点处的电压钳位,以使得mosfet断开。

6、在一可能实施方式中,钳位子电路包括钳位电阻,储能子电路包括储能电容,被构造为在第二节点处为低电平时,储能电容通过钳位电阻进行放电,以向第四节点提供高电平,其中,放电时间小于低电平的持续时间。

7、在一可能实施方式中,所述开关控制模块还包括:辅助控制子电路,分别连接第二节点和第四节点,被构造为在第二节点处为高电平时,向第四节点处提供高电平,在第二节点处为低电平时,向第四节点处提供低电平。

8、在一可能实施方式中,辅助控制子电路包括:第一分压电阻,分别连接第二节点和第五节点;第二分压电阻,分别连接第五节点和地;三极管,三极管的基极连接到第五节点,三极管的发射极接地,三极管的集电极连接到第四节点。

9、在一可能实施方式中,辅助控制子电路还包括:限流电阻,设置在三极管的集电极与第四节点之间。

10、在一可能实施方式中,所述驱动电路还包括:第二二极管,第二二极管的阳极连接到供电电源,第二二极管的阴极连接到第三节点。

11、在一可能实施方式中,所述驱动电路还包括:开关调节子电路,设置在第二节点与耗尽型晶体管的栅极之间,以调节耗尽型晶体管的开关速度。

12、在一可能实施方式中,所述驱动电路还包括:反向通路,分别连接耗尽型晶体管的漏极和p型mosfet的漏极。

13、在一可能实施方式中,p型mosfet与耗尽型晶体管被封装为一常闭开关器件,驱动电路、储能子电路、钳位子电路、辅助控制子电路和开关调节子电路被封装为针对常闭开关器件的驱动芯片,其中,耗尽型晶体管的漏极作为常闭开关器件的漏极,耗尽型晶体管的源极与p型mosfet的源极连接,p型mosfet的漏极作为常闭开关器件的源极;或者,p型mosfet与耗尽型晶体管被封装为一常闭开关器件,驱动电路和辅助控制子电路被封装为针对常闭开关器件的驱动芯片,储能子电路、钳位子电路、开关调节子电路被引出,在封装外连接;或者,储能子电路、钳位子电路、辅助控制子电路、p型mosfet和耗尽型晶体管被封装为耗尽型功率器件,驱动电路和开关调节子电路被封装为针对耗尽型功率器件的驱动芯片;或者,所有器件被封装为一功率器件。

14、为使本申请的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

技术特征:

1.一种耗尽型晶体管的驱动电路,其特征在于,包括:

2.根据权利要求1所述的驱动电路,其特征在于,耗尽型晶体管的工作期间包括驱动电路被启动、输出控制信号的阶段。

3.根据权利要求1所述的驱动电路,其特征在于,mosfet包括p型mosfet,p型mosfet的源极与耗尽型晶体管的源极连接,第一节点为p型mosfet的源极,

4.根据权利要求3所述的驱动电路,其特征在于,所述开关控制模块还包括:

5.根据权利要求4所述的驱动电路,其特征在于,钳位子电路包括钳位电阻,储能子电路包括储能电容,被构造为在第二节点处为低电平时,储能电容通过钳位电阻进行放电,以向第四节点提供高电平,其中,放电时间小于低电平的持续时间。

6.根据权利要求4所述的驱动电路,其特征在于,所述开关控制模块还包括:

7.根据权利要求6所述的驱动电路,其特征在于,辅助控制子电路包括:

8.根据权利要求7所述的驱动电路,其特征在于,辅助控制子电路还包括:

9.根据权利要求3所述的驱动电路,其特征在于,所述驱动电路还包括:

10.根据权利要求6所述的驱动电路,其特征在于,所述驱动电路还包括:

11.根据权利要求3所述的驱动电路,其特征在于,所述驱动电路还包括:

12.根据权利要求10所述的驱动电路,其特征在于,p型mosfet与耗尽型晶体管被封装为一常闭开关器件,驱动电路、储能子电路、钳位子电路、辅助控制子电路和开关调节子电路被封装为针对常闭开关器件的驱动芯片,

技术总结

本申请提供一种耗尽型晶体管的驱动电路,包括:MOSFET,与耗尽型晶体管进行级联;开关控制模块,分别连接第一节点、第二节点和MOSFET的栅极,第一节点在MOSFET与耗尽型晶体管之间,第二节点为驱动电路的输出端;其中,耗尽型晶体管的栅极连接到第二节点,被构造为在驱动电路输出的控制信号的作用下导通或者关断,开关控制模块被构造为在耗尽型晶体管的工作期间控制MOSFET持续导通。通过本申请,能够实现对耗尽型晶体管的直接驱动,以及有效降低开关损耗,还能够避免发生因MOS雪崩击穿引入额外损耗,或者电容失配导致的震荡失效问题。

技术研发人员:钟海峰,刘志宏,黎子兰

受保护的技术使用者:广东致能科技有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!