应用于高速模数转换器的JESD204B物理层输出电压自动校准电路的制作方法

本发明涉及一种应用于高速模数转换器的jesd204b物理层输出电压自动校准电路及校准算法,属于设计集成电路设计。

背景技术:

1、随着近些年集成电路设计技术的飞速发展,模数转换器作为联通现实世界和信息世界的媒介,伴随着5g通讯技术、军事雷达等领域越来越高的芯片技术需求,对转换器转换速率的要求越来越高,随之用于高速数据传输的协议与之诞生,即jesd204b协议,相比于传统的lvds,其链路速率更高,占用io口数量更少,目前广泛用于高速、高分辨率数据转换器之中。

2、根据功能不同,应用于高速高精度模数转换器的jesd204b共分为四个部分,分别为应用层、传输层、数据链路层以及物理层。其中,物理层通过串化器将并行数据转换为串行数据,并按照通道速率发送至接收端。传统的jesd204b物理层电路,易受到工艺、环境温度等非理想因素的影响,导致输出电压发生偏移,从而使输出的数据发生错误。因此,需要数字校准技术针对物理层输出电压进行校准,稳定输出电压。由于模数转换器在通讯和雷达等应用场景中需要一直保持工作状态,因此对输出电压的校准必须采用后台校准;由于转换器使用场景的复杂多变,因此需要对物理层输出电压进行实时校准。

技术实现思路

1、本发明解决的技术问题是:针对目前现有技术中,传统jesd204b物理层输出接口性能易受制约、非理想因素影响较大的问题,提出了一种应用于高速模数转换器的jesd204b物理层输出电压自动校准电路。

2、本发明解决上述技术问题是通过如下技术方案予以实现的:

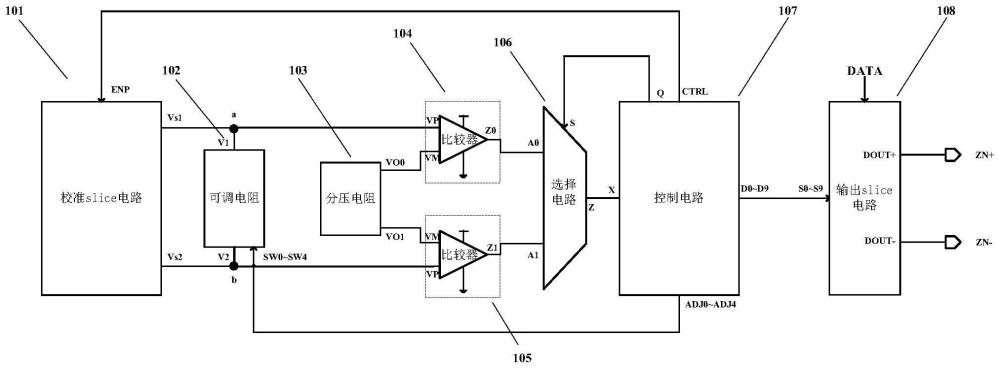

3、一种应用于高速模数转换器的jesd204b物理层输出电压自动校准电路,包括校准slice电路101、可调电阻模块102、分压电阻电路103、第一比较器104、第二比较器105、选择电路106、控制电路107以及输出slice电路108;

4、所述校准slice电路101通过enp信号开启后,输出校准前的差分电压;

5、所述可调电阻模块102通过调节接入电阻值,从而改变节点a、b处电压,即改变校准前的差分电压的数值;

6、所述分压电阻103将电源电压分压成所需的差分电压vo0、vo1;

7、所述第一比较器104将分压电阻103输出的高电压vo0与a节点电压进行比较并输出比较结果;

8、所述第二比较器105将分压电阻103输出的低电压vo1与b节点电压进行比较并输出比较结果;

9、所述选择电路106将第一比较器104或第二比较器105的比较结果输出至控制电路107;

10、所述控制电路107通过enp信号控制校准slice电路101开启;控制选择电路输出第一比较器104或第二比较器105的结果;通过改变输出adj0~adj4的值调节可调电阻102,从而改变节点a或b的输出,并将调节完成时adj0~adj4的值进行译码,通过d0~d9输出端传输至输出slice电路108;

11、所述输出slice电路108接收控制电路输出的校验码,从而决定接入的slice个数,实现物理层输出电压校准,输出经过校准后的数据。

12、进一步的,

13、所述校准slice电路101输入端通过控制信号enp与控制电路107输出端ctrl相连;校准slice电路101的第一输出端vs1和第二输出端vs2分别连接到第一比较器104的输入端vp和第二比较器105的输入端vp,可调电阻模块102的第一输入端v1和第二输入端v2分别连接到所述第一输出端vs1和第二输出端vs2;

14、可调电阻模块102输入端sw0~sw4与控制电路107的输出端adj0~adj4相连;

15、所述分压电阻模块103输出端vo0、vo1分别连接第一比较器104输入端vm和第二比较器105输入端vm;

16、所述第一比较器104输出端z与选择电路106的输入端a0相连;所述第二比较器105输出端z与选择电路106的输入端a1相连;

17、所述选择电路106输出端z与控制电路107的输入端x相连;选择电路106输入端s与控制电路输出端q相连;

18、所述控制电路107输出端dout输出校正码d0~d9给输出slice电路108的输入端s0~s9;

19、所述输出slice电路108输入端data输入需传输的数据,正输出端dout+和负输出端dout-输出差分信号。

20、进一步的,

21、所述a点具体是指:可调电阻模块102的第一输入端v1与校准slice电路101第一输出端的连接点;校准slice电路101第一输出端输出电压信号为vs1;a点电压即第一比较器104输入端vp的电压;

22、所述b点具体是指:可调电阻模块102的第二输入端v2与校准slice电路101第二输出端的连接点;校准slice电路101第二输出端输出电压信号为vs2;b点电压即第二比较器105输入端vp的电压。

23、进一步的,

24、可调电阻模块102输入端sw0~sw4与控制电路107的输出端adj0~adj4相连,接收adj0~adj4输出的值。

25、进一步的,

26、所述校准slice电路101具体包括:选择器mux1~mux8、传输门tg1~tg8、电阻rs1~rs4、反相器n1、与非门nand1、nand2、或非门nor1和nor2;

27、所述选择器mux1~mux8,输入端a0均接电源vdd,输入端a1均接地gnd,选择端s接电源vdd,选择器mux1~mux8输出端z与传输门tg1~tg8输入端一一对应连接;

28、传输门tg1,输入端与mux1输出端z相连,输出端与电阻rs1相连,控制端k1和与非门nand1的输出端相连,控制端k4和或非门nor2的输出端相连;

29、传输门tg2,输入端与mux2输出端z相连,输出端与电阻rs1相连,控制端k2和与非门nand2的输出端相连,控制端k3和或非门nor1的输出端相连;

30、传输门tg3,输入端与mux3输出端z相连,输出端与电阻rs2相连,控制端k1和与非门nand1的输出端相连,控制端k4和或非门nor2的输出端相连;

31、传输门tg4,输入端与mux4输出端z相连,输出端与电阻rs2相连,控制端k2和与非门nand2的输出端相连,控制端k3和或非门nor1的输出端相连;

32、传输门tg5,输入端与mux5输出端z相连,输出端与电阻rs3相连,控制端k2和与非门nand2的输出端相连,控制端k3和或非门nor1的输出端相连;

33、传输门tg6,输入端与mux6输出端z相连,输出端与电阻rs3相连,控制端k1和与非门nand1的输出端相连,控制端k4和或非门nor2的输出端相连;

34、传输门tg7,输入端与mux7输出端z相连,输出端与电阻rs4相连,控制端k2和与非门nand2的输出端相连,控制端k3和或非门nor1的输出端相连;

35、传输门tg8,输入端与mux8输出端z相连,输出端与电阻rs4相连,控制端k1和与非门nand1的输出端相连,控制端k4和或非门nor2的输出端相连;

36、电阻rs1,一端与tg1和tg2的输出相连,另一端与vs1以及电阻rs2相连;电阻rs2,一端与tg3和tg4的输出相连,另一端与vs1以及电阻rs1相连;电阻rs3,一端与tg5和tg6的输出相连,另一端与vs2以及电阻rs4相连;电阻rs4,一端与tg7和tg8的输出相连,另一端与vs2以及电阻rs3相连;

37、反相器n1,一端与enp相连,另一端接或非门nor1和nor2的一个输入端;所述与非门nand1,一个输入端接gnd,另一个输入端接enp,输出端接tg1、tg3、tg6、tg8的控制端k1;所述与非门nand2,一个输入端接vdd,另一个输入端接enp,输出端接tg2、tg4、tg5、tg7的控制端k2;所述或非门nor1,一个输入端接gnd,另一个输入端接enn,输出端接tg2、tg4、tg5、tg7的控制端k3;所述或非门nor2,一个输入端接vdd,另一个输入端接enn,输出端接tg1、tg3、tg6、tg8的控制端k4。

38、进一步的,

39、所述可调电阻模块102具体包括并联连接的第一支路、第二支路、第三支路、第四支路、第五支路和第六支路,六个支路的两端均分别连接在可调电阻模块102的第一输入端v1和第二输入端v2之间;

40、其中,第一支路为串联连接的电阻r0和开关st0,第二支路为串联连接的电阻r1和开关st1,第三支路为串联连接的电阻r2和开关st2,第四支路为串联连接的电阻r3和开关st3,第五支路为串联连接的电阻r4和开关st4,第六支路为电阻r5;

41、所述开关st0~st4被信号sw0~sw4一一对应控制。

42、进一步的,

43、所述控制电路107具体包括控制器、存储器以及计算单元;所述控制器在系统上电开始工作后,通过ctrl信号控制开启校准slice电路101,通过输出信号q控制选择电路106输出第一比较器104或第二比较器105的比较结果,并通过输入信号x将比较结果传递到控制器,通过输出信号adj0~adj4调节可调电阻102;所述存储器将两次校准所得两组adj0~adj4的值进行临时储存,在校准完成后将最终值输出至计算单元;所述计算单元将从存储器获得的两组adj0~adj4的值进行计算译码,并将所得译码结果d0~d9发送至输出slice电路108。

44、进一步的,

45、所述输出slice电路108具体包括:slice单元slice0~slice9;

46、所述slice单元slice0~slice9的控制信号输入端s分别与输入信号s0~s9一一对应连接,对应控制电路107的输出d0~d9,数据输入端a与输入信号data相连,输出信号d+与dout+相连,输出信号d-与dout-相连,所述slice单元slice0~slice9通过输入信号s0~s9控制其接入数量,实现对输出电压的控制。

47、进一步的,

48、本发明还提出一种应用于高速模数转换器的jesd204b物理层输出电压自动校准方法,包括如下步骤:

49、1、当电路上电完成后,首先控制电路107控制选择电路106输出端z选择a0进行输出,控制电路107通过ctrl控制校准slice电路101开启,输出待校准电压vs1和vs2;

50、同时分压电阻将电源电压分压后,输出高电压vo0到第一比较器104输入端vm,输出低电压vo1到第二比较器105输入端vm;

51、2、控制电路107通过adj0~adj4控制可调电阻模块102的接入电阻由最小依次增大,进而逐渐增大a节点即第一比较器104输入端vp的电压;

52、3、当可调电阻模块102接入电路的电阻值越来越大后,第一比较器104输入端vp的电压越来越高,直至vp=vm后,选择电路输出端z的输出由0变为1,同时选择电路106将该变换传输至控制电路107,控制电路107将当前adj0~adj4的值转译为d0~d4,并进行存储;

53、4、控制电路107控制选择电路106输出端z选择a1进行输出;

54、5、控制电路107通过adj0~adj4控制可调电阻模块102的接入电阻由最大依次减小,进而逐渐增大b节点即第二比较器105输入端vp的电压;

55、6、当可调电阻模块102接入电路的电阻值越来越小后,第二比较器105输入端vp的电压越来越高,直至vp=vm后,输出端z的输出由0变为1,同时选择电路106将该变换传输至控制电路107,控制电路107将当前adj0~adj4的值转译为d5~d9,并进行存储;

56、7、将控制电路107存储的校准值d0~d9传输至输出slice电路108控制接入的slice个数,校准输出slice电路108的dout+和dout-的输出电压;

57、8、数据data传入输出slice电路108,通过dout+和dout-进行输出;

58、9、重复步骤1~8,进行物理层输出电压实时校准,并对数据data进行输出。

59、本发明与现有技术相比的优点在于:

60、(1)本发明提供的一种应用于高速模数转换器的jesd204b物理层输出电压自动校准电路,在传统物理层输出结构的基础上,增加了电压自动校准电路,通过校准电路的生成校验码,进一步调整驱动的slice个数,以达到校准功能;

61、(2)本发明采用后台数字校准技术,不会打断物理层正常的输出,其特点是利用校准slice电路101的输出结合可调电阻模块102,调节a、b节点电压与分压电阻103输出进行实时比较,并将调节码进行转译,生成校验码,选择接入物理层输出接口中slice的个数,从而对物理层输出电压进行校准;

62、(3)本发明采用实时校准技术,会在电路工作中一直保持对物理层输出电压的校准,从而提高在复杂多变的环境中输出数据的准确度。

- 还没有人留言评论。精彩留言会获得点赞!