一种Hadamard_LDPC译码方法及译码器装置与流程

本发明涉及无线通信,更为具体的,涉及一种hadamard_ldpc译码方法及译码器装置。

背景技术:

1、在深空通信、卫星通信等应用场景中,由于发射功率及外界环境等因素限制,接收机接收到的有用信号功率远小于噪声功率,表现为极低信噪比环境。根据香农定理,信道容量与信号带宽与信噪比呈正相关。为提高低信噪比环境下功率利用率,传统常采用扩频和信道编码的两级纠错技术思路,通过扩频的方式展宽信号频谱使单位带宽内信号功率降低,同时利用信道编码增加冗余比特,提高传输可靠性。扩频+编码结构简单,便于工程实现,但是由于扩频和编码独立,解调译码时不能充分利用原始信道信息,导致性能损失。如何在低信噪比环境下构造一种可逼近香农限的低码率信道编译码成为亟待解决的问题。

2、在中高码率下,低密度奇偶校验(low density parity check codes,ldpc)码是一种可逼近香农理论极限的码字。ldpc码具有较长的编码块长度,在5g nr中主要用于数据的传输,但是其采用弱相关的奇偶校验约束,在低码率情况下译码性能较差。为了提高ldpc码的译码性能,可以将奇偶校验约束替换为hadamard约束关系,构造hadamard_ldpc码,借鉴传统ldpc分层置信传播译码方法,对hadamard_ldpc码进行基于符号最大概率的分层译码,具备最佳译码性能,可实现快速迭代收敛。然而,由于hadamard约束关系更复杂,译码过程中需要计算内积函数,存在大量指数、对数非线性运算,运算复杂度高、时延长、消耗资源大,不利于工程应用实现。

技术实现思路

1、本发明的目的在于克服现有技术的不足,提供一种hadamard_ldpc译码方法及译码器装置,译码器具备在低信噪比环境下可逼近香农限的性能,并且复杂度低、硬件开销小何收敛速度快,适用于低信噪比环境下无线数据传输。

2、本发明的目的是通过以下方案实现的:

3、一种hadamard_ldpc译码方法,包括:

4、s1,初始化:将输入的hbit信道软信息数据lch写入信道软信息输入单元llr_ram中,所述信道软信息输入单元llr_ram包括缓存器1和缓存器2,采用乒乓机制先将数据以hbit串行写入缓存器1,并从缓存器1以h×zbit并行读出,然后将其写入判决信息存储单元vn_ram中,至此完成用输入的软信息数据lch对变量信息lv进行初始化处理,即lv=lch,然后将下一帧输入数据串行写入缓存器2中,同时将校验消息存储单位cn_ram初始化为全零,即lcv=0,并设定译码控制单元中迭代层数layer=0、迭代次数iter=0和最大迭代次数max_iter=max_iter;

5、s2,变量节点消息更新:待判决信息存储单元vn_ram写满数据后,译码控制单元中利用迭代层数/次数控制单元控制迭代层数layer设为1、迭代次数iter设为1,译码控制单元中利用层处理顺序存储单元h_ram将当前迭代层数作为读地址,输出校验矩阵每行非负值所在列索引值,vn_ram将h_ram输出数据作为读地址,输出校验矩阵行重dc个变量信息,送至循环移位单元进行同等位数循环左移,并将左移结果依次传到消息更新单元1~z中,z为循环移位因子,消息更新单元将移位后的变量信息与cn_ram输出进行相减,完成变量节点消息更新,即

6、

7、其中,l、k分别为当前迭代层数和迭代次数;

8、s3,校验节点消息更新:消息更新单元中的变量消息排序单元根据最新的变量节点信息及信道输入的hadamard校验节点信息进行顺序调整,产生的数据送至消息更新单元中的校验节点消息更新单元,校验节点消息更新单元根据max_log_map准则,按下面公式进行校验节点更新:

9、

10、

11、

12、

13、其中,a为归一化因子;

14、s4,信道信息更新:利用更新后的校验节点消息与变量节点消息进行相加,完成信道信息更新:

15、

16、将更新后的信道信息数据存储至信道信息存储单元vn_ram中,译码控制单元中迭代层数/次数控制单元控制迭代层数layer加1,重复上述步骤,利用更新后的信道信息对下一层校验节点进行更新,直到所有层的消息都更新完毕,则完成一次迭代,迭代次数iter加1,继续重复上述步骤,待iter=max_iter,结束译码过程;

17、s5,判决译码:从vn_ram中读出数据进行判决,即为译码输出。

18、一种hadamard_ldpc译码器装置,包括:

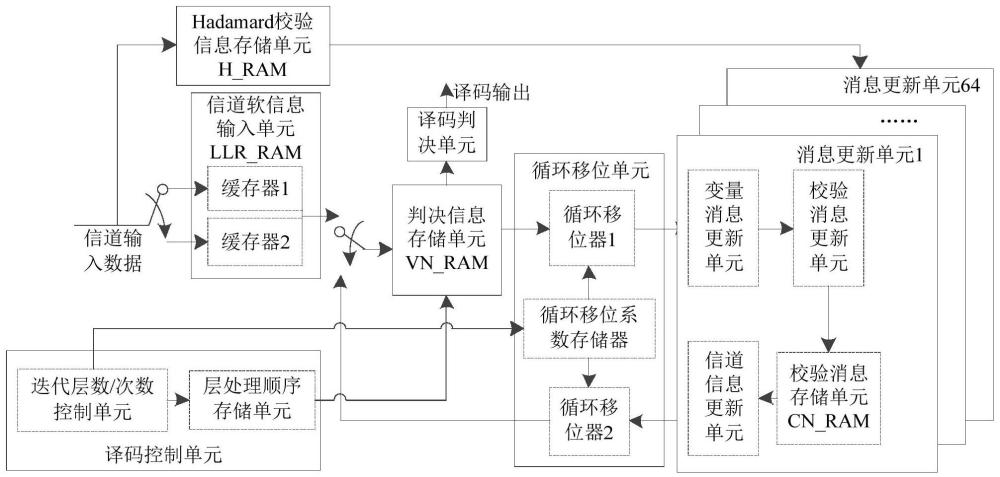

19、信道软信息输入单元llr_ram、hadamard校验信息存储单元h_ram、判决信息存储单元vn_ram、译码控制单元、循环移位单元、消息更新单元和译码判决单元;所述信道软信息输入单元llr_ram包括缓存器1和缓存器2;所述译码控制单元包括迭代层数/次数控制单元和层处理顺序存储单元;所述循环移位单元包括循环移位系数存储器、循环移位器1和循环移位器2;所述消息更新单元包括变量消息更新单元、校验消息更新单元、校验消息存储单元cn_ram和信道信息更新单元;

20、初始化时信道输入数据写入信道软信息输入单元llr_ram中的缓存器1中,然后从缓存器1读出,将其写入判决信息存储单元vn_ram中,然后将下一帧输入数据串行写入缓存器2中,同时将校验消息存储单位cn_ram初始化为全零,并设定译码控制单元中迭代层数layer=0、迭代次数iter=0和最大迭代次数max_iter=max_iter;

21、变量节点消息更新时,待判决信息存储单元vn_ram写满数据后,译码控制单元中利用迭代层数/次数控制单元控制迭代层数layer设为1、迭代次数iter设为1,译码控制单元中利用层处理顺序存储单元h_ram将当前迭代层数作为读地址,输出校验矩阵每行非负值所在列索引值,vn_ram将h_ram输出数据作为读地址,输出校验矩阵行重dc个变量信息,送至循环移位单元进行同等位数循环左移,并将左移结果依次传到消息更新单元中,消息更新单元将移位后的变量信息与cn_ram输出进行相减,完成变量节点消息更新;

22、校验节点消息更新时,消息更新单元中的变量消息排序单元根据最新的变量节点信息及信道输入的hadamard校验节点信息进行顺序调整,产生的数据送至消息更新单元中的校验节点消息更新单元,校验节点消息更新单元根据max_log_map准则进行校验节点更新;

23、信道信息更新时,利用更新后的校验节点消息与变量节点消息进行相加,完成信道信息更新;将更新后的信道信息数据存储至信道信息存储单元vn_ram中,译码控制单元中迭代层数/次数控制单元控制迭代层数layer加1,利用更新后的信道信息对下一层校验节点进行更新,直到所有层的消息都更新完毕,则完成一次迭代,迭代次数iter加1,待iter=max_iter,结束译码过程;判决译码时,从vn_ram中读出数据进行判决,即为译码输出。

24、进一步地,所述消息更新单元的数量为1~z个,z为循环移位因子,分层译码时按校验矩阵h的循环移位因子z分为多层,每层包含z行,且在同一层校验节点集中,任意两个校验节点相连的变量节点都是不同的,即h矩阵同一层中每列最多只有一个非负元素;在一层更新过程中,消息更新单元1~z并行工作,循环移位单位输出的h×zbit数据分离为z个hbit数据,分别送至消息更新单元1~z中完成变量节点消息更新和校验节点消息更新。

25、进一步地,所述变量消息更新单元,用于更新变量节点消息,变量节点更新子单元共有dc个变量消息输入,采用流水线处理结构,具体为:第一级流水线将输入的移位后的数据进行延迟,并从cn_ram输出上一次更新的dc个校验节点消息;第二级流水线将所述cn_ram输出值与延迟后的移位数据进行求差运算,得到更新的dc个变量节点消息。

26、进一步地,所述校验消息更新单元,用于更新校验节点消息,根据选择的hadamard矩阵阶数r,校验节点更新子单元共有dc个变量消息和2r-dc个hadamard校验消息输入,首先按特定顺序将2r个输入数据进行排序,然后利用r层蝶形fht和dfht处理架构,通过加减、比较处理,得到更新的dc个校验节点消息。

27、进一步地,所述循环移位系数存储单元只对校验矩阵中每行非负值进行存储,采用rom存储器实现,将校验矩阵中每行的非负值组合成一个数据,rom存储器深度设置为13;与循环移位系数存储形式一致,校验矩阵层处理顺序存储单元也仅对每行非负值所在的列索引进行存储。

28、进一步地,所述循环移位单元采用384位寄存器桶形循环移位结构。

29、进一步地,所述循环移位器1用于调整输入到消息更新单元的变量节点判决消息的顺序,所述循环移位器2用于调整消息更新单元输出信息的顺序并将其传输到判决信息存储单元中等待下一次读取,两者实现相反操作,循环移位器1移位值为shift,循环移位器2移位值为z-shift。

30、进一步地,所述校验消息更新单元,包括4层蝶形fht和4层蝶形dfht处理单元,采用流水处理结构,共有16个数据输入,6个数据输出,处理运算仅包含加减、比较运算;

31、其中,对蝶形fht处理单元进行改进优化具体包括:首先将16个将输入数据data_in1~16按奇、偶顺序分组,依次送入第一层进行加法和减法处理,第一层仅需1个加法器和1个减法器,消耗1个时钟周期,并将加法器、减法器输出进行延时,待前两组数据计算完成后,开始使能第二层,第二层使用2个加法器和2个减法器,并将加法器、减法器输出进行延时;依次类推,直至完成4层蝶形计算;

32、其中,对dfht蝶形结构进行改进优化具体包括:分为四层处理,max(a,b)与min(a,b)子模块对输入的a和b进行比较,输出两者中的最大值和最小值,max(a,-b)与min(a,-b)子模块对输入的a和-b进行比较,输出两者中的最大值和最小值;dfht第一层计算将fht输出的16个数据按(1,2)、(3,4)、(5,6)、(7,8)、(9,10)、(11,12)、(13,14)、(15,16)分组分别经过max(a,b)、min(a,b)、max(a,-b)、min(a,-b)处理,得到32个输出数据;dfht第二层计算将上层的32个数据按序均分为4组,每组按(1,5)、(2,6)、(3,7)、(4,8)、(1,6)、(2,5)、(3,8)、(4,7)的顺序经过max(a,b)、min(a,b)、max(a,b)、min(a,b)、max(a,-b)、min(a,-b)、max(a,-b)、min(a,-b)处理,得到32个输出数据;dfht第三层计算将上层的32个数据按序均分为2组,每组按(1,9)、(2,10)、(3,11)、(4,12)、(5,13)、(6,14)、(1,10)、(2,9)、(7,16)、(8,15)的顺序经过max(a,b)、min(a,b)、max(a,b)、min(a,b)、max(a,b)、min(a,b)、max(a,-b)、min(a,-b)、max(a,-b)、min(a,-b)处理,得到20个输出数据;dfht第四层计算将上层的20个数据按(1,11)、(2,12)、(3,13)、(4,14)、(5,15)、(6,16)、(7,17)、(8,18)、(1,12)、(2,11)、(9,20)、(10,19)的顺序经过max(a,b)、min(a,b)、max(a,b)、min(a,b)、max(a,b)、min(a,b)、max(a,b)、min(a,b)、max(a,-b)、min(a,-b)、max(a,-b)、min(a,-b)处理,得到12个输出数据;最后将12个数据按顺序相加得到6个输出,即为更新的校验消息。

33、进一步地,所述译码控制单元采用状态机方式,状态转移共含初试状态、第一次迭代、迭代更新、译码判决四种状态;状态机默认进入初试状态,当输入信道信息数据有效时,状态机从初试状态进入第一次迭代状态,此时判断数据长度是否达到缓存区深度,若达到,则转移至迭代更新状态,否则退回至初试状态,迭代更新状态判断迭代次数是否满足设置的最大迭代次数,若满足最大迭代次数,则结束迭代,进入译码判决状态,否则继续迭代,译码判决完成,译码输出,完成译码,重回初试状态等待下一帧数据。

34、本发明的有益效果包括:

35、本发明采用max-log-map准则作为hadamard校验节点迭代更新依据,将hadamard_ldpc码传统符号最大后验概率译码过程中的大量指数、对数运算替换为比较和加法运算,大大降低了运算量,减少硬件实现复杂度,降低硬件资源开销。

36、本发明借鉴传统ldpc分层译码思想,设计分层hadamard_ldpc译码器,依据校验矩阵按层进行迭代,在更新完每个校验节点消息之后就立刻利用该更新消息更新变量信息,并将其用于下一个校验节点消息的更新,即在一个过程内同时完成两种节点消息的传递,同时利用乒乓缓存机制、快速hadamard蝶形变化结构,整体上大大降低译码处理时延,从而提高译码器吞吐率。

37、本发明通过引入归一化因子,修正max-log-map线性运算迭代译码带来的外部信息失真,使校验节点迭代更新值尽量与传统基于符号最大后验概率准则的结果分布一致,因此在实现低译码时延、低运算复杂度的同时保证译码性能不损失。

- 还没有人留言评论。精彩留言会获得点赞!