一种低功耗电平转换电路的制作方法

本发明涉及电平转换电路,尤其是涉及一种低功耗电平转换电路。

背景技术:

1、在高集成发射机领域,发射链路的复杂度较高,电源品种较多,不同的芯片工作在不同的电压域,其中电平转换电路是发射链路的一个重要组成部分,用于驱动大功率pmos管,实现功放芯片的电源调制功能。

2、传统的电平转换电路主要包括输入缓冲器、高低电平转换模块、输出缓冲器、ldo电路和基准电路,外部电压信号经过输入缓冲器后,输入缓冲器输出控制信号给高低电平转换模块,高低电平转换模块输出控制信号驱动输出输出缓冲器的输入端,基准电路输出跟基准偏置电压相等的基准信号,该基准信号作为ldo电路的输入信号,ldo电路输出具有驱动能力的基准偏置信号,此基准偏置信号作为输出缓冲器的参考电平,控制输出缓冲器输出最终的驱动电平信号来驱动大功率pmos管的栅端,从而实现电平转换。但是,上述传统的电平转换电路在高压电源和低压电源都未建立完成的时候,其内部的节点电压会处于不定态,即其在电源上电顺序不同时会造成输出电压信号的状态异常。该输出电压信号给发射机中的大功率pmos管驱动时,如果出现不定态,则被驱动的大功率pmos管的输出就为不定态,此时大功率pmos管调制输出的电压给发射机中的功放供电,如果存在不定态则对功放的安全性构成威胁。另外,传统的电平转换电路通过基准电路产生基准偏置电压,该基准偏置电压没有驱动能力,其作为ldo电路的输入,ldo电路输出具有驱动能力的基准偏置电压,作为输出缓冲器的参考电平。虽然ldo和基准电路实现了带驱动能力的基准偏置电压,但是ldo电路和基准电路整体结构比较复杂,导致传统的电平转换电路不仅功耗较高,而且面积较大。

技术实现思路

1、本发明所要解决的技术问题是提供一种在高压电源和低压电源不同步上电时输出逻辑电平确定,不存在不定态,且不需要专门的ldo电路和基准电路来实现带驱动能力的基准偏置电压,面积和功耗均较小的低功耗电平转换电路。

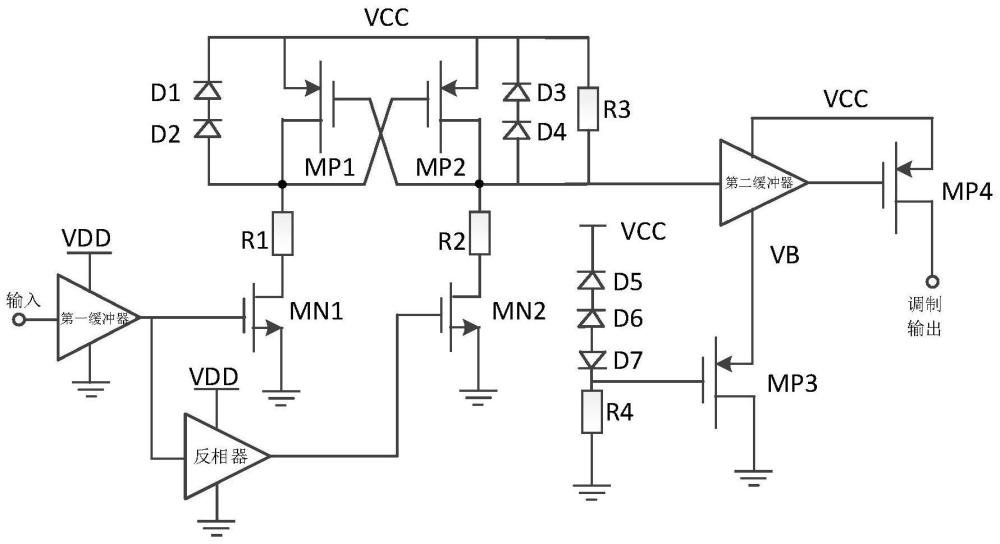

2、本发明解决上述技术问题所采用的技术方案为:一种低功耗电平转换电路,包括第一反相器、第一缓冲器、第二缓冲器、第一nmos管、第二nmos管、第一pmos管、第二pmos管、第三pmos管、第四pmos管、第一电阻、第二电阻、第三电阻、第四电阻、第一二极管、第二二极管、第三二极管、第四二极管、第五二极管、第六二极管和第七二极管,所述的第一二极管、所述的第二二极管、所述的第三二极管、所述的第四二极管、所述的第五二极管和所述的第六二极管均为齐纳二极管,所述的第七二极管为普通二极管,所述的第四pmos管为大功率pmos管,所述的第三电阻的阻值为mω级,所述的第一nmos管和所述的第二nmos管的阈值电压均不高于0.6v;所述的第一缓冲器、所述的第二缓冲器和所述的第一反相器均具有第一电源端、第二电源端、输入端和输出端,所述的第一缓冲器的第一电源端和所述的第一反相器的第一电源端均接入电源电压vdd,所述的第二缓冲器的第一电源端、所述的第一二极管的阴极、所述的第一pmos管的源极、所述的第二pmos管的源极、所述的第三二极管的阴极、所述的第三电阻的一端、所述的第五二极管的阴极和所述的第四pmos管的源极均接入电源电压vcc,电源电压vdd低于电源电压vcc,所述的第一缓冲器的第二电源端、所述的第一反相器的第二电源端、所述的第一nmos管的源极、所述的第二nmos管的源极、所述的第四电阻的一端和所述的第三pmos管的漏极均接地,所述的第一缓冲器的输入端为所述的低功耗电平转换电路的输入端,所述的第一缓冲器的输出端分别与所述的第一nmos管的栅极和所述的第一反相器的输入端相连,所述的第一反相器的输出端与所述的第二nmos管的栅极连接,所述的第一nmos管的漏极和所述的第一电阻的一端连接,所述的第一电阻的另一端、所述的第一pmos管的漏极、所述的第二二极管的阳极和所述的第二pmos管的栅极连接,所述的第二二极管的阴极与所述的第一二极管的阳极连接,所述的第二nmos管的漏极和所述的第二电阻的一端连接,所述的第二电阻的另一端、所述的第二pmos管的漏极、所述的第四二极管的阳极、所述的第一pmos管的栅极、所述的第三电阻的另一端和所述的第二缓冲器的输入端连接,所述的第四二极管的阴极与所述的第三二极管的阳极连接,所述的第二缓冲器的第二电源端与所述的第三pmos管的源极连接,所述的第二缓冲器的输出端与所述的第四pmos管的栅极连接,所述的第四pmos管的漏极为所述的低功耗电平转换电路的输出端,所述的第四电阻的另一端、所述的第七二极管的阴极和所述的第三pmos管的栅极连接,所述的第七二极管的阳极和所述的第六二极管的阳极相连,所述的第六二极管的阴极和所述的第五二极管的阳极相连。

3、所述的第一反相器包括第五pmos管和第三nmos管,所述的第五pmos管的源极为所述的第一反相器的第一电源端,所述的第五pmos管的栅极和所述的第三nmos管的栅极连接,且其连接端为所述的第一反相器的输入端,所述的第五pmos管的漏极和所述的第三nmos管的漏极连接,且其连接端为所述的第一反相器的输出端,所述的第三nmos管的源极为所述的第一反相器的第二电源端。

4、所述的第一缓冲器由m个第二反相器串联形成,m为大于等于2的偶数,每个所述的第二反相器均具有第一电源端、第二电源端、输入端和输出端,m个第二反相器的第一电源端连接,且其连接端为所述的第一缓冲器的第一电源端,m个第二反相器的第二电源端连接,且其连接端为所述的第一缓冲器的第二电源端,第1个第二反相器的输入端为所述的第一缓冲器的输入端,第m个第二反相器的输出端为所述的第一缓冲器的输出端,第n个第二反相器的输出端和第n+1个第二反相器的输入端连接,n=1,2,…,m-1;所述的第二反相器的电路结构与所述的第一反相器相同。

5、所述的第二缓冲器由k个第三反相器串联形成,k为大于等于2的偶数,每个所述的第三反相器均具有第一电源端、第二电源端、输入端和输出端,k个第三反相器的第一电源端连接,且其连接端为所述的第二缓冲器的第一电源端,k个第三反相器的第二电源端连接,且其连接端为所述的第二缓冲器的第二电源端,第1个第三反相器的输入端为所述的第二缓冲器的输入端,第k个第三反相器的输出端为所述的第二缓冲器的输出端,第j个第三反相器的输出端和第j+1个第三反相器的输入端连接,j=1,2,…,k-1;所述的第三反相器的电路结构与所述的第一反相器相同。

6、与现有技术相比,本发明的优点在于通过第一反相器、第一缓冲器、第二缓冲器、第一nmos管、第二nmos管、第一pmos管、第二pmos管、第三pmos管、第四pmos管、第一电阻、第二电阻、第三电阻、第四电阻、第一二极管、第二二极管、第三二极管、第四二极管、第五二极管、第六二极管和第七二极管构成电平转换电路,整体电路结构比较简单,当电源电压vcc上电而电源电压vdd未完成上电时,第一nmos管和第二nmos管的栅极控制电压太低,第一nmos管和第二nmos管未开启,此时第一pmos管和第二pmos管的漏极电压也无法确定,此时利用第三电阻的上拉作用,将第二pmos管的漏极电压上拉至等于电源电压vcc,解决高/低压电源不同步上电时输出逻辑电平不定态的现象,由于第一nmos管和第二nmos管未开启,其所处支路无静态电流,第三电阻在电路实现中往往可以采用高方块电阻值的多晶电阻,占用面积小,同时第三电阻的阻值采用mω级别,静态功耗较低,由此,由于mω级别的第三电阻不影响电平转换电路的驱动能力,因此不受转换频率的限制,另外本发明利用齐纳二极管的反向击穿稳压特性和pmos管的栅源电压跟随特性,产生带驱动能力的参考电压信号,即电源电压vcc经过第三二极管和第四二极管的反向击穿电压再经过第七二极管的正向压降vd,将第四电阻的另一端电压上拉到vcc-2*vr-vd,第二缓冲器的第二电源端的基准偏置电压vb随第三pmos管的栅端电压上升到vcc-2*vr-vd+vth,实现方式简单,省去了专门的基准电路和ldo电路,由此本发明在高压电源和低压电源不同步上电时输出逻辑电平确定,不存在不定态,且不需要专门的ldo电路和基准电路来实现带驱动能力的基准偏置电压,面积和功耗均较小。

- 还没有人留言评论。精彩留言会获得点赞!