MEMS器件的制作方法

mems器件

技术领域

1.本实用新型涉及微机电系统(micro

‑

electro

‑

mechanical system,mems)技术领域,具体涉及一种mems器件。

背景技术:

2.在mems器件中,通常包括由电路板和位于电路板上的壳体组成的封装结构,壳体和电路板之间形成空腔,具有特定功能的mems芯片和与mems芯片对应的专用集成电路(application specific integrated circuit,asic)被设置在空腔内,并受到电路板的支撑。与此同时,mems器件的封装结构中常常还包括一些辅助元件,例如电容。

3.为了将电容封装到mems器件的封装结构中,通常需要在电路板的位于腔体内的表面上设置两个预定焊盘,分别连接电容的两个引脚。预定焊盘的设置占用了电路板的面积,对产品小型化产生不利影响,同时提高了电路板的布线难度。

技术实现要素:

4.有鉴于此,本实用新型实施例提供了一种mems器件,以解决现有技术中的mems器件中由于加入电容所导致的mems器件尺寸增大和布线难度增大的问题。

5.本实用新型提供了一种mems器件,包括:电路板,包括第一表面,第一表面上设置有第一接线端子;壳体,包括导电通路,壳体设置在第一表面上,与电路板之间形成腔体;以及位于腔体内的电容,电容包括第一引脚和第二引脚,第一引脚与第一接线端子连接,第二引脚与导电通路连接。

6.在一个实施例中,电容的第一引脚和第二引脚相对设置。

7.在一个实施例中,壳体包括与第一表面平行的顶壁,电容的第二引脚在顶壁与导电通路连接。

8.在一个实施例中,电容倚靠在第一表面和侧壁上。

9.在一个实施例中,电容包括相对设置的第一端和第二端,第一引脚位于第一端,第二引脚位于第二端。电路板包括开设于第一表面上的第一凹槽,第一端位于第一凹槽内;和/或壳体包括与第一凹槽正对的第二凹槽,第二端位于第二凹槽内。

10.在一个实施例中,还包括位于腔体内的asic芯片,asic芯片包括信号端口,信号端口和电容的第一引脚电连接;壳体的内壁导电,电容的第二引脚通过壳体的内壁接地。

11.在一个实施例中,信号端口通过金属线连接至第一接线端子。

12.在一个实施例中,第一表面上还设置有第二接线端子,信号端口通过金属线连接至第二接线端子;第一接线端子和第二接线端子通过电路板中的电路布线连接。

13.在一个实施例中,信号端口包括输入引脚、输出引脚、电源引脚中的任一个。

14.在一个实施例中,壳体通过导电材料与电路板密封连接;电路板还包括与第一表面相对的第二表面,第二表面上设置有接地端子;导电材料通过电路板上的金属化过孔连接至电路板内的电路布线,并经由电路布线连接至接地端子。

15.在一个实施例中,还包括连通腔体和大气的声孔;封装结构还包括位于腔体内的mems声学芯片,mems声学芯片与asic芯片电连接。

16.根据本实用新型提供的mems器件,电容的第二引脚与壳体上的导电通路连接,以通过壳体将第二引脚引出到mems器件的封装结构之外。此时,电路板11上仅需设置一个第一接线端子来将电容的第一引脚引出到mems器件的封装结构之外,相对于电容的两个引脚分别通过电路板上的两个焊盘引出到封装结构之外而言,减小了电路板上需要设置的第一接线端子的数量,从而减小了电路板的尺寸,进而减小了mems器件的尺寸。与此同时,由于电路板内的布线需要绕过电路板上的第一接线端子,因此当第一接线端子的数量减少时,还可以进一步降低电路板的布线难度。

附图说明

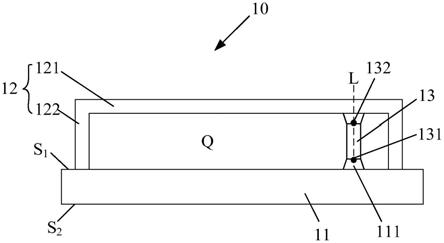

17.图1为本实用新型一实施例提供的mems器件的结构示意图。

18.图2为本实用新型另一实施例提供的mems器件的结构示意图。

19.图3为本实用新型又一实施例提供的mems器件的结构示意图。

20.图4为本实用新型一实施例提供的麦克风的封装结构的侧视结构示意图。

21.图5为图4所示麦克风的封装结构的俯视结构示意图。

22.图6为图4所示麦克风的电路结构示意图。

具体实施方式

23.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

24.图1为本实用新型一实施例提供的mems器件的结构示意图。如图1所示,该mems器件10包括电路板11、壳体12和电容13。电路板11包括第一表面s1,第一表面s1上设置有第一接线端子111。壳体12包括导电通路,壳体12设置在第一表面s1上,与电路板11之间形成腔体q。电容13位于腔体q内,电容13包括第一引脚131和第二引脚132,第一引脚131与第一接线端子111连接,第二引脚132与壳体12上的导电通路连接。

25.电路板11和壳体12共同组成了mems器件的封装结构。壳体12上的导电通路用于将电容13的第二引脚132引出到封装结构之外,例如,导电通路在壳体12的外表面形成接线端子;又例如,导电通路通过电路板11上的金属化过孔连接电路板11内部的布线,进而通过布线在电路板11的、和第一表面s1相对的第二表面s2上形成焊盘。电路板11上的第一接线端子111用于将电容13的第一引脚131引出到封装结构之外,例如,第一接线端子111经过电路板11内部的布线在电路板11的第二表面s2上形成焊盘。

26.导电通路可以是由导电材料形成的线路,也可以是壳体12本身。导电通路为壳体本身是指壳体12自身可导电,例如金属壳体,这种情况下,整个壳体12作为导电通路,第二引脚132直接与壳体12连接。

27.根据本实施例提供的mems器件,当将电容13封装到mems器件的封装结构中时,通过壳体12将电容13的一个引脚(即第二引脚132)引出到封装结构之外。此时,只需要在电路

板11上设置一个第一接线端子111(例如焊盘)来将电容13的另一个引脚(即第一引脚131)引出到封装结构之外,相对于电容13的两个引脚分别通过电路板11上的两个焊盘引出到封装结构之外而言,减小了电路板11上需要设置的第一接线端子111的数量,从而减小了电路板11的尺寸,进而减小了mems器件的尺寸。与此同时,由于电路板11内的布线需要绕过电路板11上的第一接线端子,因此当第一接线端子的数量减少时,还可以进一步降低电路板11的布线难度。

28.在一个实施例中,如图1所示,电容13的第一引脚131和第二引脚132相对设置。也就是说,对于一个封装好的电容13而言,第一引脚131和第二引脚132分别位于电容13的封装结构的相对两侧,即第一引脚131和第二引脚132在电容13的封装结构上的连线l穿过电容13的封装结构。

29.在一个优选地实施例中,第一引脚131和第二引脚132在电容13的封装结构上的连线l穿过电容13的重心。

30.对于图1所示的mems器件10而言,在将电容封装到mems器件的封装结构中时,电容13的第一引脚131连接电路板11上的第一接线端子111,第二引脚132连接壳体12。这种情况下,第一引脚131和第二引脚132即为固定电容13的受力点。根据本实施例提供的mems器件10,通过将电容13的两个受力点相对设置,即第一引脚131和第二引脚132相对设置,可以平衡受力,确保电容固定地更牢固。

31.在一个实施例中,如图1所示,壳体12包括与第一表面s1平行的顶壁121,电容13的第二引脚132在顶壁121与导电通路连接,即电容13的第二引脚132在顶壁121接入导电通路。这种情况下,相当于将电容13倒立封装在mems器件10中,从而提供了一种新的电容的封装形式。

32.图2为本实用新型另一实施例提供的mems器件的结构示意图。如图2所示的mems器件20和图1所示mems器件10的区别仅在于,在本实施例中,壳体12还包括除了顶壁121之外的侧壁122,电容23的第二引脚232在侧壁122与导电通路连接,即电容23的第二引脚232在侧壁122接入导电通路。

33.在本实施例中,电容23倚靠在电路板11的第一表面s1和壳体12的侧壁122上,即电容23分别与电路板11的第一表面s1和壳体12的侧壁122接触,从而受到第一表面s1和侧壁122的支撑。

34.应当理解,虽然图2中的电容23的第二引脚232是在壳体12的侧壁122与导电通路连接的,但其仅是示例性的。可以通过合理设置电容23的位置和第二引脚232在电容23上的位置,以使得第二引脚232在壳体12的顶壁121与导电通路连接。与此同时,由于有了第一表面s1和侧壁122的支撑,这种情况下,可以任意设置第一引脚131和第二引脚132的位置,而无需考虑第一引脚131和第二引脚132处受力平衡的问题。

35.根据本实施例提供的mems器件20,电路板11的第一表面s1和/或壳体12的侧壁122可以为电容提供支撑,避免电容23的整体重量全部集中在第一引脚131和/或第二引脚132上,从而进一步确保电容固定地更牢固。

36.图3为本实用新型又一实施例提供的mems器件的结构示意图。如图3所示的mems器件30和图1所示mems器件10的区别仅在于,电容33包括相对设置的第一端a和第二端b,第一引脚331位于第一端a,第二引脚332位于第二端b。电路板11包括开设于第一表面s1上的第

一凹槽1101,第一端a位于第一凹槽1101内。壳体12包括与第一凹槽1101正对的第二凹槽1102,第二端b位于第二凹槽1102内。

37.这种情况下,第一接线端子111设置在第一凹槽1101的槽底,以和电容33的第一引脚331电连接。壳体12上的导电通路穿过第二凹槽1102的槽底,以和电容33的第二引脚332电连接。

38.应当理解,电路板11上的第一凹槽1101和壳体12上的第二凹槽1102可以分别单独设置,例如仅在电路板11上设置第一凹槽1101,或者仅在壳体12上设置第二凹槽1102。

39.根据本实施例提供的mems器件30,通过在电路板11和/或壳体12上设置凹槽来为电容33提供固定作用,确保电容固定地更牢固。

40.麦克风是mems器件的一个重要分支。在麦克风的使用过程中,外界干扰极易耦合到麦克风的输入/输出接口,因此可以在麦克风的输入/输出接口并联电容来滤除引入的干扰杂波。下面结合附图具体描述具有上述任一实施例提供的mems器件中电容结构的麦克风的封装结构。

41.图4为本实用新型一实施例提供的麦克风的封装结构的侧视结构示意图。图5为图4所示麦克风的封装结构的俯视结构示意图。图6为图4所示麦克风的电路结构示意图。结合图4、图5和图6所示,该麦克风40在图1所示mems器件10的基础上,进一步包括位于腔体q内的asic芯片14和与asic芯片14电连接的mems声学芯片15,以及连通腔体q和大气的声孔16,如图4所示,该声孔16可以开设在电路板11上,也可以开设在壳体12上。具体而言,asic芯片14包括多个信号端口,例如输入引脚vin、偏执电压引脚bias、电源引脚vdd、接地引脚gnd和输出引脚vout。mems声学芯片15的两个电极分别与输入引脚vin和偏执电压引脚bias连接。

42.在麦克风40的使用过程中,外部声音通过声孔16进入腔体q,mems声学芯片15将声音信号转换为电信号,该电信号经过asic芯片放大后,通过电路板11第二表面s2上的接线端子引出到封装结构之外。

43.在本实施例中,asic芯片14的至少部分信号端口可能会引入外部干扰信号,例如输入引脚vin、电源引脚vdd或输出引脚vout。对于这类引脚,通过为其并联电容,可以滤除由相应引脚引入的杂波。以输出引脚vout为例,输出引脚vout和电容13的第一引脚131电连接。壳体12的内壁导电,例如壳体本身为金属材质,或者在绝缘壳体的内壁电镀一层金属,这种情况下,整个壳体12作为导电通路,并且可以起到电磁屏蔽的作用。电容13的第二引脚132通过壳体12的内壁接地。具体而言,输出引脚vout和电容13的第一引脚131电连接可以通过如下两种方式实现。例如,参阅图4和图5,电路板11的第一表面s1上还设置有第二接线端子112,输出引脚vout通过金属线连接至第二接线端子112。第一接线端子111和第二接线端子112通过电路板11中的电路布线连接。又例如,输出引脚vout通过金属线连接至第一接线端子111。这样,相当于输出引脚vout和电容13的第一引脚131共用同一接线端子,从而可以进一步节省电路板的尺寸。

44.电容13的第二引脚132通过壳体12接地可以通过如下方式实现。壳体12通过导电材料与电路板11密封连接。电路板11的第二表面s2上设置有接地端子gnd’。导电材料通过电路板11上的金属化过孔连接至电路板11被的电路布线,并经由电路布线连接至接地端子gnd’。

45.应当理解,本实施例仅以输出引脚vout并联一个电容13为例,根据实际需要,也可

以设置输出引脚vout并联多个电容,或者分别为输入引脚vin、电源引脚vdd和输出引脚vout中的至少一个引脚分别并联一个或多个电容。并且,电容13可以采用上述任一实施例提供的封装结构,例如如1、图2或图3所示的封装结构。与此同时,本实施例仅以麦克风作为示例,根据本实用新型提供的电容的封装结构还可以应用到其他mems器件中。

46.为了例示和描述的目的已经给出了以上描述。此外,此描述不意图将本申请的实施例限制到在此公开的形式。尽管以上已经讨论了多个示例方面和实施例,但是本领域技术人员将认识到其某些变型、修改、改变、添加和子组合。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1