电子封装件及其承载结构与制法的制作方法

[0001]

本发明有关一种半导体封装结构,特别是一种电子封装件及其承载结构与制法。

背景技术:

[0002]

现有半导体封装件1,如图1所示,先将一半导体芯片11以其作用面11a利用覆晶接合方式(即通过导电凸块110与底胶111)设在一封装基板10上,再将一散热件13以其顶片130经由tim层12(其包含焊锡层与助焊剂)回焊结合在该半导体芯片11的非作用面11b上,且该散热件13的支撑脚131通过粘着层14架设在该封装基板10上,以供该半导体芯片11所产生的热能经由该非作用面11b、tim层12而传导至该散热件13的顶片130以散热至该半导体封装件1的外部。

[0003]

但是,现有半导体封装件1中,因该封装基板10的材料特性,而在封装制程的热处理期间(thermal cycle),容易因热胀冷缩的现象而造成该封装基板10变形,致使该封装基板10发生翘曲(warpage)的问题,导致所述导电凸块110无法有效或精确接合在该封装基板10上。

[0004]

另外,随着科技的演进,电子产品需求趋势朝向异质整合迈进,多芯片封装结构(mcm/mcp)兴起,其将多颗半导体芯片封装成一颗半导体芯片的特性,使其具有较多的i/o数,且可以大幅增加处理器的运算能力,减少信号传递的延迟时间,以应用在高密度线路/高传输速度/高叠层数/大尺寸设计的高阶产品,然而,产品功能的多元化使封装结构更加复杂,而复杂的结构在更小的体积内实现,这就导致结构变得更加脆弱,当封装结构发生翘曲或者其它形变时,更加容易发生失效,此外,因其多芯片集成在一基板的结构特色,随着市场规格需求日新月变,其整体封装结构尺寸也随之越做越大,使得因翘曲所导致的脱层、球裂及芯片崩裂等问题日益严重。

[0005]

因此,如何克服上述现有技术的问题,实已成为目前业界亟待克服的难题。

技术实现要素:

[0006]

鉴于上述现有技术的缺陷,本发明提供一种承载结构及其制法,以有效避免或降低翘曲的问题。

[0007]

本发明的承载结构包括:绝缘板体;线路层,其设在该绝缘板体上;以及第一间隔部,其设在该绝缘板体中而未电性连接该线路层。

[0008]

本发明也提供一种承载结构的制法,其包括:提供一基材;形成凹部在该基材中;形成金属层在该基材上以遮盖该凹部,使该凹部作为间隔部;以及经由该金属层形成线路层,且该间隔部未电性连接该线路层。

[0009]

前述的承载结构及其制法中,该基材包含核心层,其具有绝缘芯部,且该间隔部贯穿该绝缘芯部。例如,该核心层还具有至少一形成在该绝缘芯部上的绝缘部。进一步,该绝缘部经由加压加温制程以形成在该间隔部中。

[0010]

前述的承载结构及其制法中,该基材定义有置晶区及围绕该置晶区周围的外围

区,以令该间隔部位在该外围区上。例如,该间隔部位在该外围区的轮廓边缘及/或轮廓角落上。或者,该外围区定义有底胶边界线,以将该外围区分为邻接该置晶区的第一区域与最外侧的第二区域。进一步,该间隔部位在该外围区的第一区域及/或第二区域上。

[0011]

前述的承载结构及其制法中,该间隔部为沟槽、孔洞或其组合。

[0012]

前述的承载结构及其制法中,该间隔部的轮廓呈直线状、曲线状、波浪状、锯齿状或其组合。

[0013]

本发明更提供一种电子封装件,其包括:前述的承载结构;电子元件,其设在该承载结构上且电性连接该线路层;以及散热件,其设在该承载结构上,其中,该散热件具有第二间隔部。

[0014]

前述的电子封装件中,该散热件包含有一结合该电子元件的散热体,且该第二间隔部位在该散热体结合该电子元件的一侧。例如,该第二间隔部位在该散热体结合该电子元件的区域以外。

[0015]

前述的电子封装件中,该第二间隔部为沟槽、孔洞或其组合。

[0016]

前述的电子封装件中,该第二间隔部的轮廓呈直线状、曲线状、波浪状、锯齿状或其组合。

[0017]

由上可知,本发明的电子封装件及其承载结构与制法,主要经由该间隔部的设计,以破坏(或断开)该绝缘板体或该基材,使该绝缘板体或该基材的结构应力不会连续集中在该绝缘板体或该基材的材料较硬处,所以相较现有技术,本发明的承载结构可避免或降低翘曲的问题。

[0018]

另外,该间隔部中填充软质胶材(即该绝缘体),不仅可吸收该绝缘板体或该基材的硬质材的应力释放,且可吸收在后续的高温制程所造成的热形变。

附图说明

[0019]

图1为现有半导体封装件的剖视示意图。

[0020]

图2a至2e为本发明的承载结构的制法的剖视示意图。

[0021]

图2a’为图2a的整体上视示意图。

[0022]

图2b’为图2b的整体上视示意图。

[0023]

图2c’及2c”为图2c的不同实施方式示意图。

[0024]

图2e’及2e”为图2e的不同实施方式示意图。

[0025]

图2f及2f’为图2e的绝缘板体的整体上视示意图。

[0026]

图3a及3a’为图2e的后续制程的不同实施例的剖视示意图。

[0027]

图3b为本发明的电子封装件的剖视示意图。

[0028]

图3b’及3b”为图3b的不同实施例的局部上视示意图。

[0029]

图4a及4b为图3b的第一实施例的不同处的局部上视图。

[0030]

图5a及5b为图3b的第二实施例的不同处的局部上视图。

[0031]

图6a及6b为图3b的第三实施例的不同处的局部上视图。

[0032]

附图标记说明

[0033]

1 半导体封装件

ꢀꢀꢀꢀꢀꢀꢀꢀ

10 封装基板

[0034]

11 半导体芯片

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

11a,31a 作用面

[0035]

11b,31b 非作用面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

110,310 导电凸块

[0036]

111,311 底胶

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

12 tim层

[0037]

13,33,43,53,63 散热件

ꢀꢀꢀꢀꢀ

130 顶片

[0038]

131,331 支撑脚

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

14 粘着层

[0039]

2,2’,2”,4,5,6 承载结构

ꢀꢀꢀꢀ

2a 基材

[0040]

2b 绝缘板体

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

20 核心层

[0041]

200 绝缘芯部

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

201 第一金属层

[0042]

202 第二金属层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

203 绝缘体

[0043]

203’,203

”ꢀ

中空部

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

203a 第一绝缘部

[0044]

203b 第二绝缘部

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

21,21

’ꢀ

第一间隔部

[0045]

21a,21b,21c,21d,21e,21f,41b,41a,46,51,56,61,66 凹部

[0046]

22 线路层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

220 导电通孔

[0047]

23 介电层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

24 绝缘保护层

[0048]

25 表面处理层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

3,3’,3

”ꢀ

电子封装件

[0049]

31 电子元件

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

32 结合层

[0050]

330 散热体

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

34 胶体

[0051]

36,36’,36a,36b,36c,36d,36e,36f,36g,36h 第二间隔部

[0052]

91 第一承载件

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

92 第二承载件

[0053]

a 置晶区

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

b 外围区

[0054]

b1 第一区域

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

b2 第二区域

[0055]

c 区域

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

l 底胶边界线。

具体实施方式

[0056]

以下经由特定的具体实施例说明本发明的实施方式,本领域技术人员可由本说明书所揭示的内容轻易地了解本发明的其他优点及功效。

[0057]

须知,本说明书附图所绘示的结构、比例、大小等,均仅用在配合说明书所揭示的内容,以供本领域技术人员的了解与阅读,并非用在限定本发明可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本发明所能产生的功效及所能达成的目的下,均应仍落在本发明所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如“上”、“第一”、“第二”及“一”等用语,也仅为便在叙述的明了,而非用在限定本发明可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当也视为本发明可实施的范畴。

[0058]

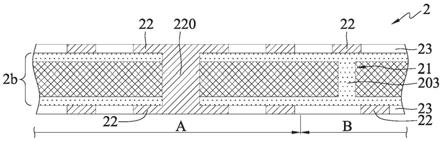

图2a至2e为本发明的承载结构2的制法的剖面示意图。

[0059]

如图2a及2a’所示,提供一基材2a,其定义有一置晶区a及一围绕该置晶区a周围的外围区b。

[0060]

在本实施例中,该基材2a设在第一承载件91上,且该基材2a包含依序叠设在该第一承载件91上的第一金属层201及核心层20,而该核心层20具有依序叠设在该第一金属层201上的第一绝缘部203a、绝缘芯部200及第二绝缘部203b。例如,该第一承载件91为如不锈钢的金属压板,该第一金属层201为铜箔,该第一与第二绝缘部203a,203b为如环氧树脂

(epoxy)的胶体,该绝缘芯部200含有玻纤及如bt(bismaleimide triazine)、fr4或fr5等的有机树脂。

[0061]

另外,当制作该基材2a时,可先在该第一承载件91上铺设该第一金属层201,再将已制作完成的粘合片作为该核心层20,以令该核心层20以其第一绝缘部203a粘贴在该第一金属层201上。

[0062]

又,该外围区b定义有一如环状的底胶(underfill)边界线l,以将该外围区b分为邻接该置晶区a的第一区域b1与最外侧的第二区域b2,其中,该第二区域b2环绕该第一区域b1。

[0063]

如图2b所示,形成凹部在该基材2a的外围区b上,以作为第一间隔部21,使该第一金属层201外露在该第一间隔部21。

[0064]

在本实施例中,该第一间隔部21贯穿该核心层20(或该绝缘芯部200)而未贯穿该第一金属层201。例如,该第一金属层201保持完整。具体地,采用雷射方式进行挖槽孔作业以形成该第一间隔部21,且所用的雷射强度符合不会破坏(或破坏极少)铜箔的波长范围,使该第一金属层201作为挖槽孔作业的止挡层。

[0065]

另外,该第一间隔部21位在该外围区b,例如位在该外围区b的轮廓边缘(如第一区域b1)及/或轮廓角落上,且可如图2b’所示的凹部21a,21b,21c,21d;应可理解地,该第一间隔部21位在该外围区b的第一区域b1及/或第二区域b2上。

[0066]

因此,可沿该置晶区a的轮廓边缘与该底胶边界线l的轮廓边缘之间的区间形成该第一间隔部21;或者,沿邻近该底胶边界线l的轮廓边缘处形成该第一间隔部21’;或者,在该基材2a的四个角落处形成凹部21a,21b,21c,21d以作为该第一间隔部21,其中,凹部21c还具有如图2b’所示的对角线态样。应可理解地,各角落所揭示的态样可依需求配搭在单一核心层20上,如四个角落都是同一种态样或至少二种态样的凹部组合。

[0067]

如图2c所示,形成一第二金属层202在该基材2a上,以令该第二金属层202遮盖该第一间隔部21。

[0068]

在本实施例中,经由第二承载件92将该第二金属层202压合在该基材2a的核心层20的第二绝缘部203b上。例如,该第二承载件92为如不锈钢的金属压板,该第二金属层202为铜箔,以形成铜箔基板,其中,该第一绝缘部203a、绝缘芯部200及第二绝缘部203b作为该铜箔基板中的绝缘板体2b。

[0069]

另外,在压合该第二金属层202的过程中,该第一绝缘部203a及/或第二绝缘部203b的部分材料可填入该第一间隔部21中,以在该第一间隔部21中形成绝缘体203。具体地,如图2c所示,该绝缘体203可填满该第一间隔部21中;或者,如图2c’所示,该绝缘体203未填满该第一间隔部21中,以在该第一间隔部21中形成中空部203’。应可理解地,该第一绝缘部203a及/或第二绝缘部203b也可未填入该第一间隔部21中,如图2c”所示,使该第一间隔部21作为中空部203”。

[0070]

又,经由该第一与第二承载件91,92作为加压板,以在加压加温制程中,使该第一绝缘部203a及/或第二绝缘部203b的胶材因高温高压的作用而呈熔融状,进而填入该第一间隔部21中。

[0071]

如图2d所示,接续图2c的制程,移除该第一承载件91与第二承载件92,以外露该第一金属层201与第二金属层202。

[0072]

如图2e所示,进行图案化制程,以将该第一金属层201与第二金属层202制成未电性连接该第一间隔部21(或绝缘体203)的线路层22,且形成至少一电性连接所述线路层22的导电通孔220,以制得所需的承载结构2。

[0073]

在本实施例中,该导电通孔220形成在置晶区a,但也可依需求形成在该外围区b。

[0074]

另外,该承载结构2可依需求配置至少一介电层23在该绝缘板体2b(或该核心层20)上,且令该线路层22外露在该介电层23上。

[0075]

又,若接续图2c’及2c”的制程,该承载结构2’在该外围区b上的第一间隔部21会具有中空部203’,如图2e’所示。

[0076]

另外,可依线路数量需求接续叠加核心层、形成间隔部、压合金属层及形成图案化线路层,以形成另一承载结构2”,如图2e”所示,其中,可在最外侧的线路层22上形成一如镍金材的表面处理层25,并在最外侧的介电层23上形成一如防焊材的绝缘保护层24,且令该最外侧的线路层22外露在该绝缘保护层24。例如,依需求重复进行配置核心层20、间隔部、如铜箔的金属层等制程及图案化制程。具体地,在多个绝缘板体2b相叠合时,每一层个绝缘板体2b的间隔部位置(或体积大小)可依据不同的叠纹(moire)状况而不同。

[0077]

本发明的承载结构2,2’,2”的制法主要经由第一间隔部21的设计以破坏(或断开)该绝缘板体2b的绝缘芯部200,使结构应力不会连续集中在材料较硬(玻纤)的绝缘芯部200,所以相较现有技术,本发明的承载结构2,2’,2”利用应力截断的原理以避免翘曲(warpage)或降低翘曲的问题,且通过各个应力截断点(多个第一间隔部21)作为该承载结构2,2’,2”的变形自由度调控点,以适当补偿翘曲方向。

[0078]

另外,该第一间隔部21中填充软质胶材(该绝缘体203),不仅可吸收硬质材(玻纤)的应力释放,且可吸收后续的高温制程所造成的热形变。

[0079]

又,该软质胶材(该绝缘体203)可作为断开该绝缘芯部200的分隔物,使该绝缘芯部200断开后的相邻两区块不会因热变形而相抵靠,因而提升应力截断的效果,即应力截断的功效能持续。

[0080]

另外,在该承载结构2,2’,2”的较佳实施例中,最佳的凹部设计为全沟槽式设计;次佳的设计是沿该置晶区a的轮廓边缘与该底胶边界线l的轮廓边缘之间的区间、及沿邻近该底胶边界线l的轮廓边缘处形成该第一间隔部21,如图2f所示,在此两处的凹部设计是在边角处采用沟槽状凹部21e,而在边缘直线段处采用孔洞状凹部21f,且其在四个角落处形成该第一间隔部21,且该凹部设计采用沟槽状;或者,如图2f’所示,也可设计为全孔洞式凹部21f设计。

[0081]

图3a及3a’为应用所述的承载结构2,2’,2”的电子封装件3,3’的不同实施例的剖面示意图。

[0082]

如图3a及3a’所示,在该承载结构2,2’上设置至少一电子元件31及一散热件33。

[0083]

所述的电子元件31设在该承载结构2,2’的置晶区a上,且该电子元件31为主动元件、被动元件、封装元件或其三者的组合。

[0084]

在本实施例中,该主动元件是例如半导体芯片,该被动元件是例如电阻、电容及电感,且该封装元件包含基板、设在该基板上的芯片及包覆该芯片的封装层。例如,该电子元件31为半导体芯片,其具有相对的作用面31a及非作用面31b,使该电子元件31借多个导电凸块310以覆晶方式结合并电性连接该承载结构2,2’的线路层22,并以底胶311包覆所述导

电凸块310。在其它实施例中,该电子元件31也可经由打线方式或其它方式电性连接该线路层22。

[0085]

另外,该底胶311的布设范围限制在该底胶边界线l内,即该底胶311不会超出该底胶边界线l。

[0086]

所述的散热件33经由一结合层32设在该电子元件31的非作用面31b上。

[0087]

在本实施例中,该散热件33具有一散热体330与多个设在该散热体330下侧的支撑脚331。例如,该散热体330为散热片并以下侧接触该结合层32,且该支撑脚331以胶体34结合在该承载结构2,2’的外围区b上,并相对位在该承载结构2,2’的上表面。

[0088]

另外,该结合层32为导热介面材(tim)或一般导热胶,并无特别限制。

[0089]

又,在该散热件33上可依需求形成第二间隔部36,如图3b所示的电子封装件3”。例如,该散热体330朝向该结合层32(或该电子元件31)的一侧形成有凹部以做为该第二间隔部36,使该支撑脚331与该第二间隔部36位在该散热体33的同一侧。

[0090]

进一步,如图3b’及3b”所示,该第二间隔部36位在该结合层32(或该电子元件31)的布设区域(如图3b’及3b”所示的虚线框)以外,即位在该散热体330结合该结合层32(或该电子元件31)的区域以外。因此,可沿该散热体330结合该电子元件31处的轮廓边缘(如该结合层32的轮廓边缘外的区域c)形成凹部,以作为该第二间隔部36;或者,在该散热体330与该支撑脚331之间的转折角处上形成该第二间隔部36’,如图3b’所示;或者,在该散热体330的四个角落处形成该第二间隔部36a,36b,36c,36d,36e,36f,36g,36h。应可理解地,各角落所揭示的态样可依需求配搭在单一散热体330上,如四个角落都是同一种态样或至少二种态样的凹部组合。

[0091]

另一方面,所述的凹部(即第一间隔部21与第二间隔部36)为沟槽(slot)或孔洞(如图6a所示的承载结构6的凹部61及图6b所示的散热件63的凹部66),且该凹部(间隔部)呈直线状(如图5a所示的承载结构5的凹部51及图5b所示的散热件53的凹部56)、曲线状(如图4a所示的承载结构4的凹部41b)、波浪状(如图4a所示的承载结构4的凹部41a及图4b所示的散热件43的凹部46)或锯齿状,并可依需求混合搭配成各种图案型态,如环形。例如,该凹部(间隔部)可为连续线段形成的沟槽,或以多个孔洞排列成所需的图案。因此,有关该凹部图案可依需求设计,并无特别限制。

[0092]

进一步,图4a及4b的基板4与散热件43的结构组合为第一最佳组合;图5a及5b的基板5与散热件53的结构组合为第二最佳组合;图6a及6b的基板6与散热件63的结构组合为第三最佳组合。

[0093]

本发明的电子封装件3,3’,3”经由该第一间隔部21与第二间隔部36的设计,以提升防翘曲的效果。具体地,第一最佳组合的防翘曲效果优于第二最佳组合的防翘曲效果,且第二最佳组合的防翘曲效果优于第三最佳组合的防翘曲效果。

[0094]

本发明还提供一种电子封装件3,3’,3”,其包括:一承载结构2,2’,2”、一设在该承载结构2,2’,2”上且电性连接该线路层22的电子元件31、及一设在该承载结构2,2’,2”上的散热件33,其中,该散热件33设有第二间隔部36,且该承载结构2,2’,2”包括一绝缘板体2b、至少一设在该绝缘板体2b上的线路层22、以及设在该绝缘板体2b中而未电性连接该线路层22的第一间隔部21。

[0095]

在一实施例中,该绝缘板体2b包含一核心层20,其具有一绝缘芯部200,且该第一

间隔部21贯穿该绝缘芯部200。进一步,该核心层20还具有至少一形成在该绝缘芯部200上的第一绝缘部203a与第二绝缘部203b。例如,该第一绝缘部203a与第二绝缘部203b还形成在该第一间隔部21中。

[0096]

在一实施例中,该绝缘板体2b定义有一置晶区a及一围绕该置晶区a周围的外围区b,以令该第一间隔部21位在该外围区b。例如,该第一间隔部21位在该外围区b的轮廓边缘及/或轮廓角落上。进一步,该外围区b定义一底胶边界线l,以将该外围区b分为邻接该置晶区a的第一区域b1与最外侧的第二区域b2,例如,该第一间隔部21位在该外围区b的第一区域b1及/或第二区域b2上。

[0097]

在一实施例中,该第一间隔部21为沟槽、孔洞或其组合。例如,该第一间隔部21的轮廓呈直线状、曲线状、波浪状、锯齿状或其组合。

[0098]

在一实施例中,该散热件33包含有一结合该电子元件31的散热体330与至少一设在该散热体330上的支撑脚331,以令该散热体330经由该支撑脚331设在该承载结构2,2’,2”上,且该第二间隔部36位在该散热体330结合该电子元件31的一侧。

[0099]

在一实施例中,该第二间隔部36位在该散热体330结合该电子元件31的区域以外。

[0100]

在一实施例中,该第二间隔部36为沟槽、孔洞或其组合。例如,该第二间隔部36的轮廓呈直线状、曲线状、波浪状、锯齿状或其组合。

[0101]

综上所述,本发明的电子封装件及其承载结构与制法,其经由该绝缘板体的间隔部的设计,以破坏(或断开)该绝缘板体内部结构,使结构应力不会连续集中在绝缘板体内,所以本发明的承载结构能有效避免或降低翘曲的问题。

[0102]

另外,该绝缘板体的间隔部中填充该绝缘体,不仅能吸收绝缘板体中的硬质材的应力释放,且能吸收后续的高温制程所造成的热形变。

[0103]

上述实施例仅用于例示性说明本发明的原理及其功效,而非用于限制本发明。任何本领域技术人员均可在不违背本发明的精神及范畴下,对上述实施例进行修改。因此本发明的权利保护范围,应如权利要求书所列。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1