包括中介层的半导体封装的制作方法

本公开总体上涉及一种半导体封装,并且更具体地,涉及一种具有中介层(interposer)的半导体封装。

背景技术:

通常,半导体封装被配置为包括基板和安装在基板上的半导体芯片。半导体芯片可以通过诸如凸块(bump)或布线的连接构件电连接至基板。

近来,根据对半导体封装的高性能和高集成度的需求,已经提出了用于在基板上堆叠多个半导体芯片的半导体封装的各种结构。作为示例,已经提出了使用引线接合(wirebonding)或硅穿孔(tsv)技术将堆叠在基板上的多个半导体芯片彼此电连接的技术。

技术实现要素:

根据一个实施方式,一种半导体封装可以包括:封装基板;下部芯片、中介层和上部芯片,该下部芯片、中介层和上部芯片堆叠在封装基板上;以及接合引线,该接合引线将下部芯片电连接到封装基板。下部芯片可以包括:第一下部芯片焊盘和第二下部芯片焊盘,该第一下部芯片焊盘和第二下部芯片焊盘在下部芯片的上表面上彼此间隔开,并且通过下部芯片的内部布线彼此电连接;引线接合焊盘,该引线接合焊盘在下部芯片上表面上接合到接合引线;以及下部芯片再分配线,该下部芯片再分配线将第二下部芯片焊盘电连接到引线接合焊盘。中介层可以包括:上部芯片连接焊盘,该上部芯片连接焊盘在中介层的上表面上电连接到上部芯片;下部芯片连接焊盘,该下部芯片连接焊盘在中介层的下表面上电连接到第一下部芯片焊盘;以及通孔电极,该通孔电极将上部芯片连接焊盘电连接到下部芯片连接焊盘。

根据另一实施方式,一种半导体封装可以包括:封装基板;下部芯片,该下部芯片设置在封装基板上并通过引线接合而电连接到封装基板;中介层,该中介层设置在下部芯片上并包括电连接到下部芯片的通孔电极;以及上部芯片,该上部芯片设置在中介层上并电连接到通孔电极。上部芯片通过中介层和下部芯片电连接到封装基板。

根据又一实施方式,一种半导体封装可以包括:封装基板;第一堆叠结构,该第一堆叠结构设置在封装基板上;第二堆叠结构,该第二堆叠结构设置在第一堆叠结构上;第一接合引线,该第一接合引线将封装基板电连接到第一堆叠结构的第一下部芯片;以及第二接合引线,该第二接合引线将封装基板电连接到第二堆叠结构的第二下部芯片。第一堆叠结构包括第一下部芯片、第一中介层和第一上部芯片,并且第二堆叠结构包括第二下部芯片、第二中介层和第二上部芯片。第一中介层包括将第一下部芯片电连接到第一上部芯片的第一通孔电极,并且第二中介层包括将第二下部芯片电连接到第二上部芯片的第二通孔电极。第一上部芯片通过第一中介层和第一下部芯片电连接到封装基板,并且第二上部芯片通过第二中介层和第二下部芯片电连接到封装基板。

附图说明

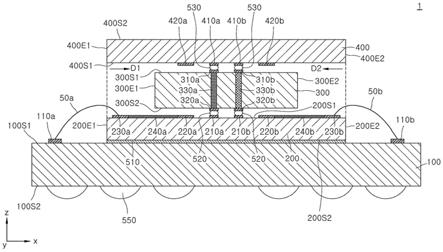

图1是示意性地示出根据本公开的一个实施方式的半导体封装的截面图。

图2和图3是示意性地示出根据本公开的实施方式的半导体芯片的平面图。

图4a和图4b是示意性地示出根据本公开的一个实施方式的半导体封装的中介层的图。

图5是示意性地示出根据本公开的一个实施方式的在半导体芯片与封装基板之间交换电信号的方法的示意图。

图6是示意性地示出根据本公开的一个实施方式的半导体封装的内部电路配置的图。

图7是示意性地示出根据本公开的另一实施方式的半导体封装的截面图。

具体实施方式

本文使用的术语可以对应于考虑了其在所呈现的实施方式中的功能而选择的词,并且这些术语的含义可以根据这些实施方式所属领域的普通技术人员而被解释为不同的含义。如果进行了具体定义,则可以根据这些定义来解释这些术语。除非另有定义,否则本文所使用的术语(包括技术术语和科学术语)具有与实施方式所属领域的普通技术人员通常所理解的含义相同的含义。在本公开的示例的描述中,诸如“第一”和“第二”、“顶部”和“底部或下部”、“左”和“右”之类的描述用于区分构件,而不用于限制构件本身或表示特定顺序。

本文所述的半导体芯片可以包括其中将集成有电子电路的半导体基板切割成管芯的形式。半导体芯片可以对应于存储器芯片、逻辑芯片(包括专用集成电路(asic)芯片)或片上系统(soc)。存储器芯片可以包括集成在半导体基板上的动态随机存取存储器(dram)电路、静态随机存取存储器(sram)电路、nand型闪存存储器电路、nor型闪存存储器电路、磁性随机存取存储器(mram)电路、电阻式随机存取存储器(reram)电路、铁电随机存取存储器(feram)电路或相变随机存取存储器(pcram)电路。逻辑芯片可以包括集成在半导体基板上的逻辑电路。半导体芯片可以根据其在关系切割工艺之后的形状而被称为半导体管芯。

在本说明书中,半导体封装可以包括其上安装有半导体芯片的封装基板。封装基板可以包括至少一层集成电路图案,并且在本说明书中可以被称为印刷电路板(pcb)。

作为一个实施方式,该半导体封装可以包括安装在封装基板上的多个半导体芯片。在半导体封装中,多个半导体芯片中的任何一个可以被配置为主芯片,并且其余的半导体芯片可以被配置为从芯片。然后,半导体封装可以使用主芯片来控制从芯片的存储器单元。主芯片可以直接与封装基板交换信号,并且从芯片可以通过主芯片与封装基板交换信号。

半导体封装可用于中诸如移动电话、与生物技术或医疗保健相关的电子系统或可穿戴电子系统的各种通信系统。

在整个说明书中,相同的附图标记指代相同的元件。即使未参照附图提及或描述某附图标记,也可参照另一附图提及或描述该附图标记。另外,即使在附图中未示出某附图标记,也可以参照另一附图提及或描述该附图标记。

图1是示意性地示出根据本公开的一个实施方式的半导体封装1的截面图。参照图1,半导体封装1可以包括堆叠在封装基板100上的下部芯片200、中介层300和上部芯片400。半导体封装1可以包括将下部芯片200电连接到封装基板100的接合引线50a和50b。

下部芯片200和上部芯片400可以是包括集成电路的半导体芯片。下部芯片200可以使用接合引线50a和50b通过引线接合方法而电连接到封装基板100。因此,下部芯片200可以直接与封装基板100交换电信号。另一方面,上部芯片400可以首先使用中介层300中的通孔电极(throughviaelectrode)330a和330b电连接到下部芯片200,并且然后可以通过下部芯片200电连接到封装基板100。也就是说,上部芯片400可以通过中介层300和下部芯片200与封装基板100交换电信号。

参照图1,可以提供封装基板100。封装基板100可以具有上表面100s1和与上表面100s1相对的下表面100s2。虽然未示出,但是封装基板100可以包括至少一层集成电路图案。

用于与下部芯片200进行引线接合的连接焊盘110a和110b可以设置在封装基板100的上表面100s1上。此外,用于与其他半导体封装或pcb电连接的连接结构550可以设置在下表面100s2上。连接结构550可以包括例如凸块和焊球等。

下部芯片200可以设置在封装基板100上。下部芯片200可以通过粘接层510而接合到封装基板100。粘接层510可以包括具有非导电性的聚合物材料。

下部芯片200可以具有上表面200s1和下表面200s2。另外,第一下部芯片焊盘210a和210b和第二下部芯片焊盘220a和220b可以在下部芯片200的上表面200s1上彼此间隔开。第一下部芯片焊盘210a和210b可以通过第一凸块520分别连接到中介层300的下部芯片连接焊盘320a和320b。

第二下部芯片焊盘220a和220b可以在横向方向(即,在平行于x方向的方向)上分别与第一下部芯片焊盘210a和210b间隔开。第二下部芯片焊盘220a和220b可以通过下部芯片200的内部布线(未示出)分别电连接至第一下部芯片焊盘210a和210b。

引线接合焊盘230a和230b可以设置在下部芯片200的上表面200s1的边缘区域中。引线接合焊盘230a和230b可以分别接触接合引线50a和50b。引线接合焊盘230a和230b可以分别通过下部芯片再分配线240a和240b而电连接到第二下部芯片焊盘220a和220b。

中介层300可以设置在下部芯片200上方。中介层300可以具有上表面300s1和下表面300s2。电连接到下部芯片200的下部芯片连接焊盘320a和320b可以设置在下表面300s2上。如上所述,下部芯片连接焊盘320a和320b可以通过第一凸块520分别连接到下部芯片200的第一下部芯片焊盘210a和210b。与此同时,电连接到上部芯片400的上部芯片连接焊盘310a和310b可以设置在上表面300s1上。如下所述,上部芯片连接焊盘310a和310b可以通过第二凸块530分别连接到第一上部芯片焊盘410a和410b。

再次参照图1,中介层300的边缘部分可以设置在从下部芯片200和上部芯片400的边缘部分沿横向方向凹入的位置处。作为示例,中介层300的侧壁表面300e1可以设置在从下部芯片200的侧壁表面200e1和上部芯片400的侧壁表面400e1沿横向方向(即,沿平行于x轴的d1方向)凹入的位置处。类似地,中介层300的另一侧壁表面300e2可以设置在从下部芯片200的另一侧壁表面200e2和上部芯片400的另一侧壁表面400e2沿横向方向(即,沿平行于x轴的d2方向))凹入的位置处。因此,中介层300中的沿着平行于x轴的方向的宽度可以小于下部芯片200和上部芯片400中的沿着平行于x轴的方向的宽度。接合引线50a和50b的至少一部分可以被容纳在凹入空间中。因此,可以稳定地执行下部芯片200的引线接合焊盘230a和230b与接合引线50a和50b之间的接合。

中介层300可以包括分别将上部芯片连接焊盘310a和310b电连接到下部芯片连接焊盘320a和320b的通孔电极330a和330b。在一个实施方式中,如下面参照图4a、图4b和图5所述,中介层300还可以包括要设置在上表面300s1和下表面300s2上的第一中介层再分配线到第四中介层再分配线341、342、351和352,以便于将上部芯片连接焊盘310a和310b以及下部芯片连接焊盘320a和320b分别连接到通孔电极330a和330b。

上部芯片400可以设置在中介层300上方。上部芯片400可以具有上表面400s1和下表面400s2。第一上部芯片焊盘410a和410b以及第二上部芯片焊盘420a和420b可以设置在上部芯片400的面向中介层300的上表面400s1上。第一上部芯片焊盘410a和410b可以通过第二凸块530分别连接到中介层300的上部芯片连接焊盘310a和310b。第二上部芯片焊盘420a和420b可以在横向方向上(即,在平行于x方向的方向上)与第一上部芯片焊盘410a和410b间隔开,并且可以不参与与包括中介层300、下部芯片200和封装基板100的外部装置的电连接。

在一个实施方式中,下部芯片200和上部芯片400可以是相同类型的芯片。然而,与上部芯片400相比,下部芯片200可以进一步在下部芯片200的上表面200s1上包括引线接合焊盘230a和230b以及下部芯片再分配线240a和240b。在这种情况下,下部芯片再分配线240a和240b可以连接到第二下部芯片焊盘220a和220b。下部芯片200和上部芯片400可以被设置为在平行于z轴的方向上彼此交叠。

在未示出的其他实施方式中,下部芯片200和上部芯片400可以具有相同的配置。也就是说,上部芯片400可以在上表面的边缘区域中包括引线接合焊盘,并且进一步包括将引线接合焊盘电连接到第二上部芯片焊盘420a和420b的上部芯片再分配线。然而,在这种情况下,上部芯片的引线接合焊盘不通过接合引线电连接到封装基板100。

在一个实施方式中,下部芯片200和上部芯片400可以是存储器芯片。在这种情况下,下部芯片200可以是主芯片,并且上部芯片400可以是从芯片。下部芯片200可以使用接合引线50a和50b直接连接且电连接到封装基板100。上部芯片400可以首先通过通孔电极330a和330b电连接到下部芯片200,并且然后可以通过下部芯片200的内部布线、输入/输出电路以及接合引线50a和50b电连接到封装基板100。

图2和图3是示意性地示出根据本公开的一个实施方式的半导体封装的半导体芯片的平面图。具体地,图2示意性地示出了图1的下部芯片200。图3示意性地示出了图1的上部芯片400。图4a和图4b是示意性地示出根据本公开的一个实施方式的半导体封装件的中介层的图。更具体地,图4a是示意性地示出图1的中介层300的平面图,并且图4b是图4a的通孔电极布置区域a的部分b的立体图。

参照图2,下部芯片200可以具有沿着平行于x轴的方向的短轴和沿着平行于y轴的方向的长轴。另外,下部芯片200可以具有沿着长轴设置的中心轴线cy-200。下部芯片200可以在短轴方向上具有预定宽度w200,并且可以在长轴方向上具有预定长度l200。中心轴线cy-200可以被配置为穿过下部芯片200的宽度w200的一半。

第一下部芯片焊盘210a和210b、第二下部芯片焊盘220a和220b以及引线接合焊盘230a和230b可以沿长轴方向(即,平行于y方向的方向)布置在下部芯片200的上表面200s1上。第一下部芯片焊盘210a和210b、第二下部芯片焊盘220a和220b以及引线接合焊盘230a和230b可以分别被设置为形成关于中心轴线cy-200对称的成对焊盘。在一个特定的实施方式中,第一下部芯片焊盘210a和210b可以被设置为比第二下部芯片焊盘220a和220b以及引线接合焊盘230a和230b更靠近中心轴线cy-200。另外,第二下部芯片焊盘220a和220b可以被设置为比引线接合焊盘230a和230b更靠近中心轴线cy-200。

基于中心轴线cy-200,第一下部芯片焊盘210a和210b可以被分类为第一下部芯片左焊盘210a和第一下部芯片右焊盘210b。基于中心轴线cy-200,第二下部芯片焊盘220a和220b可以被分类为第二下部芯片左焊盘220a和第二下部芯片右焊盘220b。基于中心轴线cy-200,引线接合焊盘230a和230b可以被分类为引线接合左焊盘230a和引线接合右焊盘230b。

如图2所示,第一下部芯片焊盘210a和210b中的每一个的表面积可以小于第二下部芯片焊盘220a和220b中的每一个的表面积。作为示例,第一下部芯片焊盘210a和210b可各自具有比第二下部芯片焊盘220a和220b小的尺寸。

与第二下部芯片焊盘220a和220b相比,第一下部芯片焊盘210a和210b可以相对密集地布置在通孔电极布置区域a中。第一下部芯片焊盘210a和210b可以沿中心轴线cy-200以预定间隔s1布置在通孔电极布置区域a中。此外,第二下部芯片焊盘220a和220b可以沿着中心轴线cy-200以相同的预定间隔s2连续地布置在通孔电极布置区域a的外部。当第一下部芯片焊盘210a和210b沿着与y轴平行的方向布置时,第一下部芯片焊盘210a和210b可以设置在第二下部芯片焊盘220a和220b之间。也就是说,第一下部芯片焊盘210a和210b以及第二下部芯片焊盘220a和220b可以在平行于y轴的方向上交替地布置。

一起参照图1和图2,电信号可以通过通孔电极330a和330b在下部芯片200的第一下部芯片焊盘210a和210b与上部芯片400的第一上部芯片焊盘410a和410b之间通信。也就是说,第一下部芯片焊盘210a和210b可以用作下部芯片200的信号输入/输出焊盘,以与上部芯片400交换电信号。

返回参照图1,下部芯片再分配线240a和240b可以设置在下部芯片200的上表面200s1上。下部芯片再分配线240a和240b可以将引线接合焊盘230a和230b电连接到第二下部芯片焊盘220a和220b。下部芯片再分配线240a和240b可以被配置为关于中心轴线cy-200对称的线。在特定示例中,基于中心轴线cy-200,下部芯片再分配线240a和240b可以被分类为下部芯片左再分配线240a和下部芯片右再分配线240b。

如上所述,从封装基板100通过接合引线50a和50b到达引线接合焊盘230a和230b的电信号可以分别通过下部芯片再分配线240a和240b传送到第二下部芯片焊盘220a和220b。随后,可以将到达第二下部芯片焊盘220a和220b的电信号传送到内部集成电路。一些电信号可以通过第一下部芯片焊盘210a和210b输出,以通过中介层300的通孔电极330a和330b而被输入到上部芯片400的第一上部芯片焊盘410a和410b。

参照图3,公开了上部芯片400。上部芯片400可以具有沿着平行于x方向的方向的短轴和沿着平行于y方向的方向的长轴。另外,上部芯片400可以具有沿着长轴设置的中心轴线cy-400。上部芯片400可以沿着短轴方向具有预定的宽度w400,并且可以沿着长轴方向具有预定的长度l400。中心轴线cy-400可以被配置为穿过上部芯片400的宽度w400的一半。在一个实施方式中,当上部芯片400被设置为与下部芯片200交叠时,上部芯片400的中心轴线cy-400可以与下部芯片200的中心轴线cy-200交叠。

第一上部芯片焊盘410a和410b以及第二上部芯片焊盘420a和420b可以沿着长轴方向(即,平行于y轴的方向)布置在上部芯片400的上表面400s1上。第一上部芯片焊盘410a和410b以及第二上部芯片焊盘420a和420b可以分别被设置为形成关于中心轴线cy-400对称的成对焊盘。在特定示例中,第一上部芯片焊盘410a和410b可以被设置为比第二上部芯片焊盘420a和420b更靠近中心轴线cy-400。基于中心轴线cy-400,第一上部芯片焊盘410a和410b可以被分类为第一上部芯片左焊盘410a和第一上部芯片右焊盘410b。基于中心轴线cy-400,第二上部芯片焊盘420a和420b可以被分类为第二上部芯片左焊盘420a和第二上部芯片右焊盘420b。

如图3所示,第一上部芯片焊盘410a和410b中的每一个的表面积可以小于第二上部芯片焊盘420a和420b中的每一个的表面积。作为示例,第一上部芯片焊盘410a和410b中的每一个可以具有比第二上部芯片焊盘420a和420b中的每一个更小的尺寸。

与第二上部芯片焊盘420a和420b相比,第一上部芯片焊盘410a和410b可以相对密集地设置在通孔电极布置区域a中。第一上部芯片焊盘410a和410b可以沿中心轴线cy-400以预定间隔s1布置在通孔电极布置区域a中。同时,第二上部芯片焊盘420a和420b可以在上表面400s1上沿着中心轴线cy-400以相同的预定间隔s2连续地设置。

一起参照图1和图3,电信号可以通过分别通孔电极330a和330b在上部芯片400的第一上部芯片焊盘410a和410b与下部芯片200的第一下部芯片焊盘210a和210b之间通信。也就是说,第一上部芯片焊盘410a和410b可以用作上部芯片的信号输入/输出焊盘,以用于与下部芯片200交换电信号。第二上部芯片焊盘420a和420b可以连接到上部芯片400内部的输入/输出电路块400a1和400a2,如稍后将描述的图6所示。然而,第二上部芯片焊盘420a和420b不直接连接到诸如中介层300、下部芯片200和封装基板100的外部装置的组件。这里,直接连接可以意味着第二上部芯片焊盘420a和420b通过诸如凸块或接合引线的外部连接结构连接至外部组件。

在一些未示出的其他实施方式中,上部芯片400可以与图2中示出的下部芯片200具有基本相同的配置。也就是说,上部芯片400可以在上表面400s1的边缘区域中具有引线接合焊盘。引线接合焊盘的位置可以与图2所示的下部芯片200的引线接合焊盘230a和230b的位置相同。另外,上部芯片400可以具有将引线接合焊盘连接到第二上部芯片焊盘420a和420b的上部芯片再分配线。

参照图4a和图4b,中介层300可以设置在下部芯片200和上部芯片400之间。中介层300可以具有沿着平行于x方向的方向的短轴和沿着平行于y方向的方向的长轴。另外,中介层300可以具有沿着长轴设置的中心轴线cy-300。中介层300可以沿着短轴方向具有预定的宽度w300,并且可以沿着长轴方向具有预定的长度l300。中心轴线cy-300可以被配置为穿过中介层300的宽度w300的一半。在一个实施方式中,当上部芯片400、中介层300和下部芯片200被设置为彼此交叠时,上部芯片400的中心轴线cy-400、中介层300的中心轴线cy-300和下部芯片200的中心轴线cy-200可以彼此交叠。

上部芯片连接焊盘310a和310b可以在中介层300的上表面300s1上沿着长轴方向(即,平行于y轴的方向)布置。在一个实施方式中,上部芯片连接焊盘310a和310b可以分别被配置为关于中心轴线cy-300对称的成对焊盘。上部芯片连接焊盘310a和310b可以被分类为关于中心轴线cy-300彼此对称的上部左焊盘310a和上部右焊盘310b。上部左焊盘310a和上部右焊盘310b可以沿着平行于y轴的方向以预定间隔s1彼此间隔开。尽管在图4a中未具体示出,但是下部芯片连接焊盘320a和320b可以沿着长轴方向布置在中介层300的下表面300s2上。在一个实施方式中,下部芯片连接焊盘320a和320b可以分别被配置为关于中心轴线cy-300对称的成对焊盘。下部芯片连接焊盘320a和320b可以被设置为与上部芯片连接焊盘310a和310b交叠。

参照图4a和图4b,从上部左焊盘310a延伸并到达第一通孔延伸焊盘341p的第一中介层再分配线341可以沿着平行于y轴的方向设置在上表面300s1上。第一通孔延伸焊盘341p可以连接到第一通孔电极330a。另外,从上部右焊盘310b延伸并到达第二通孔延伸焊盘342p的第二中介层再分配线342可以沿着平行于y轴的方向设置在上表面300s1上。第二通孔延伸焊盘342p可以连接到第二通孔电极330b。

参照图4b,设置在中介层300的下表面300s2上的下部芯片连接焊盘320a和320b可以被分类为关于中心轴线cy-300对称的下部左焊盘320a和下部右焊盘320b。在这种情况下,从下部右焊盘320b延伸并到达第三通孔延伸焊盘351p的第三中介层再分配线351可以沿着与y轴平行的方向设置在下表面300s2上。第三通孔延伸焊盘351p可以连接到第一通孔电极330a。另外,从下部左焊盘320a延伸并到达第四通孔延伸焊盘352p的第四中介层再分配线352可以沿着与y轴平行的方向设置在下表面300s2上。第四通孔延伸焊盘352p可以连接到第二通孔电极330b。

在一个实施方式中,下部左焊盘320a可以设置在上部左焊盘310a的正下方,并被设置为面对上部左焊盘310a。另外,下部右焊盘320b可以设置在上部右焊盘310b的正下方,并被设置为面对上部右焊盘310b。换句话说,下部左焊盘320a和上部左焊盘310a可以被设置为在垂直方向(即,平行于z轴的方向)上彼此交叠,并且下部右焊盘320b和上部右焊盘310b可以被设置为在垂直方向(即,平行于z轴的方向)上彼此交叠。

图5是示意性地示出根据本公开的一个实施方式的在半导体芯片与封装基板之间交换电信号的方法的示意图。在图5中,将使用上面参照图1、图2、图3、图4a和图4b描述的半导体封装1的下部芯片200、中介层300和上部芯片400的配置来示意性地描述交换电信号的方法。为了便于说明,封装基板100在图5中未示出。

参照图5和图1,封装基板100和下部芯片200之间的电信号交换可以如下进行。作为示例,封装基板100的电信号可以分别通过接合引线50a和50b而输入到引线接合左焊盘230a和引线接合右焊盘230b。输入信号可以分别通过下部芯片左再分配线240a和下部芯片右再分配线240b到达第二下部芯片左焊盘220a和第二下部芯片右焊盘220b,并且然后可以通过内部布线移动到下部芯片200内部的功能块。稍后将使用图6描述功能块。另外,与上述路径相反,半导体封装1可以具有从下部芯片200到封装基板100的电信号路径。

与此同时,封装基板100和上部芯片400之间的电信号交换可以如下进行。作为示例,电信号可以通过接合引线50a从封装基板100输入到下部芯片200的接合左焊盘230a。电信号可以通过下部芯片左再分配线240a被传送到第二下部芯片左焊盘220a。电信号可以通过内部电路布线到达第一下部芯片左焊盘210a。此后,可以通过第一凸块520将电信号从第一下部芯片左焊盘210a传送到中介层300的下部左焊盘320a。随后,电信号可以通过第四中介层再分配线352、第四通孔延伸焊盘352p、第二通孔电极330b、第二通孔延伸焊盘342p和第二中介层再分配线342而到达上部右焊盘310b。电信号可以从上部右焊盘310b通过第二凸块530到达上部芯片400的第一上部右芯片焊盘410b。这样,半导体封装件1可以具有通过下部芯片200和中介层300从封装基板100到上部芯片400的电信号路径。另外,与该路径相反,半导体封装件1可以具有通过中介层300和下部芯片200从上部芯片400到封装基板100的电信号路径。在图5中,封装基板100与上部芯片400之间的电信号路径的在下部芯片200与上部芯片400之间的电信号路径的部分被示出为“f1”。

类似地,作为另一示例,电信号可以通过接合引线50b从封装基板100输入到下部芯片200的引线接合右焊盘230b。电信号可以通过下部芯片右再分配线240b传送到第二下部芯片右焊盘220b。电信号可以通过内部电路布线到达第一下部芯片右焊盘210b。此后,电信号可以通过第一凸块520从第一下部芯片右焊盘210b传送到中介层300的下部右焊盘320b。然后,电信号可以通过第三中介层再分配线351、第三通孔延伸焊盘351p、第一通孔电极330a、第一通孔延伸焊盘341p和第一中介层再分配线341到达上部左焊盘310a。电信号可以通过第二凸块530从上部左焊盘310a到达上部芯片400的第一上部芯片左焊盘410a。这样,半导体封装件1可以具有通过下部芯片200和中介层300从封装基板100到上部芯片400的电信号路径。另外,与该路径相反,半导体封装件1可以具有通过中介层300和下部芯片200从上部芯片400到封装基板100的电信号路径。

图6是示意性地示出根据本公开的一个实施方式的半导体封装的内部电路配置的图。图6可以是示意性地示出以上参照图1描述的半导体封装1的内部电路的图。

参照图6,封装基板100可以包括设置在上表面100s1上并连接接合引线50a和50b的连接焊盘110a和110b。另外,封装基板100可以包括连接结构550,该连接结构550设置在下表面100s2上并且被提供用于与另一半导体封装或印刷电路板电连接。

下部芯片200可以包括:第一和第二输入/输出电路块200a1和200a2;第一地址和命令电路块200b1,该第一地址和命令电路块200b1连接到第一输入/输出电路块200a1;第一数据发送电路块200b2,该第一数据发送电路块200b2连接到第二输入/输出电路块200a2;以及第一存储器单元核心块200c。第一存储器单元核心块200c可以连接到第一地址和命令电路块200b1以及第一数据发送电路块200b2。

上部芯片400可以包括分别连接到一对第一上部芯片焊盘210a和210b的第二地址和命令电路块400b1和第二数据发送电路块400b2。另外,上部芯片400可以包括连接到第二地址和命令电路块400b1和第二数据发送电路块400b2的第二存储器单元核心块400c。上部芯片400可以具有分别连接到第二上部芯片焊盘420a和420b的第三和第四输入/输出电路块400a1和400a2。然而,第二上部芯片焊盘420a和420b不直接连接到诸如封装基板100、下部芯片200和中介层300的外部组件。

在一个实施方式中,封装基板100与半导体芯片200和400之间的电信号交换可以如下进行。封装基板100的电信号可以通过连接焊盘110a和110b、接合引线50a和50b、下部芯片200的引线接合焊盘230a和230b以及下部芯片再分配线240a和240b输入到第二下部芯片焊盘220a和220b。在输入的电信号中,沿着第一下部芯片内部布线200i1的一些输入信号可以通过第一输入/输出电路块200a1,并可以由第一地址和命令电路块200b1转换为第一地址和命令信号,并且然后可以被传送到第一存储器单元核心块200c。此外,在输入的电信号中,沿着第二下部芯片内部布线200i2的一些其他输入信号可以通过第二输入/输出电路块200a2,并可以由第一数据发送电路块200b2转换为数据信号,并且然后可以被传送到第一存储器单元核心块200c。

与此同时,下部芯片200的第一下部芯片内部布线200i1可以通过第一下部芯片左焊盘210a、第一凸块520、中介层300的下部左焊盘320a、中介层300的第一内部布线360a(其包括通孔电极和再分配线)、上部右焊盘310b、第二凸块530和第一上部芯片右焊盘410b连接到上部芯片400的第一上部芯片内部布线400i1。因此,在封装基板100的电信号中,从下部芯片200的第一地址和命令电路200b1输出的一些电信号可以沿着上部芯片400的第一上部芯片内部布线400i1输入到第二地址和命令电路块400b1。可以通过第二地址和命令电路块400b1将电信号转换为第二地址和命令信号,并且然后将其传送到第二存储器单元核心块400c。

因此,在本公开的一个实施方式中,上部芯片400可以使用经由下部芯片200和中介层300的电信号路径来与封装基板100交换电信号。也就是说,上部芯片400可以不经由第二上部芯片右焊盘420b应用第四输入/输出电路块400a1。

类似地,下部芯片200的第二下部芯片内部布线200i2可以通过第一下部芯片右焊盘210b、第一凸块520、中介层300的下部右焊盘320b、中介层300的第二内部布线360b(其包括通孔电极和再分配线)、上部左焊盘310a、第二凸块530和第一上部芯片左焊盘410a连接到第二上部芯片内部布线400i2。因此,在封装基板100的电信号中,从下部芯片200的第一数据发送电路块200b2输出的一些电信号可以沿着第二上部芯片内部布线400i2输入到第二数据发送电路块400b2。可以通过第二数据发送电路块400b2将电信号转换为数据信号,并且然后将其传送到第二存储器单元核心块400c。

此外,再次参照图6,从下部芯片200的第一存储器单元核心块200c输出的电信号可以沿着第一下部芯片内部布线200i1穿过第一地址和命令电路块200b1以及第一输入/输出电路块200a1,以到达第二下部芯片左焊盘220a,或者可以沿着第二下部芯片内部布线200i2穿过第一数据发送电路块200b2和第二输入/输出电路块200a2,以到达第二下部芯片右焊盘220b。此后,电信号可以通过下部芯片再分配线240a和240b发送到引线接合焊盘230a和230b,并且然后通过接合引线50a和50b传送到封装基板100。

另外,从上部芯片400的第二存储器单元核心块400c输出的电信号可以沿着第一上部芯片内部布线400i1穿过第二地址和命令电路块400b1,以到达第一上部芯片右焊盘410b,或者可以沿着第二上部芯片内部布线400i2穿过第二数据发送电路块400b2,以到达第一上部芯片左焊盘410a。之后,电信号可以通过第二凸块530到达中介层300的上部芯片连接焊盘310a和310b。随后,电信号可以穿过中介层300的第一内部布线360a和第二内部布线360b,以到达中介层300的下部芯片连接焊盘320a和320b。随后,电信号可以通过第一凸块520被输入到下部芯片200的第一下部芯片焊盘210a和210b。输入的电信号可以分别沿着第一下部芯片内部布线200i1和第二下部芯片内部布线200i2发送到第二下部芯片焊盘220a和220b。随后,电信号可以通过下部芯片再分配线240a和240b移动到引线接合焊盘230a和230b,并且然后可以分别通过接合引线50a和50b发送到封装基板100。

换句话说,第一输入/输出电路块200a1和第二输入/输出电路块200a2可以接收分别通过接合引线50a和50b、引线接合焊盘230a和230b、下部芯片再分配线240a和240b以及第二下部芯片焊盘220a发送的封装基板100的电信号。此外,第一输入/输出电路块200a1和第二输入/输出电路块200a2可以使用下部芯片200的内部布线将接收到的电信号分别发送到第一地址和命令块200b1以及第一数据发送电路块200b2。第一地址和命令块200b1和第一数据发送电路块200b2可以分别接收所发送的电信号。第一地址和命令块200b1和第一数据发送电路块200b2分别将接收到的电信号发送到下部芯片200的第一存储器单元核心块200c。

另外,中介层300可以通过第一下部芯片焊盘320a和320b接收封装基板100的一些电信号。另外,中介层300可以使用中介层300的内部布线将一些接收到的电信号发送到上部芯片400的第一上部芯片焊盘410a和410b。第二地址和命令块400b1和第二数据发送电路块400b2可以使用上部芯片400的内部布线接收分别被发送到第一上部芯片焊盘410a和410b的电信号。此外,第二地址和命令块400b1和第二数据发送电路块400b2可以分别将接收到的电信号发送到上部芯片400的第二存储器单元核心块400c。

如上所述,本公开的一个实施方式可以提供一种半导体封装,该半导体封装具有堆叠在封装基板上的下部芯片、中介层和上部芯片。在该半导体封装中,下部芯片可以使用接合引线与封装基板交换电信号。上部芯片通过中介层连接到下部芯片,并且可以经由下部芯片与封装基板交换电信号。因此,上部芯片可以省略与封装基板的直接电连接,由此,可以避免在上部芯片与封装基板之间的电连接中可能涉及的上部芯片中的输入/输出电路、上部芯片上的再分配线以及引线接合焊盘的应用。因此,可以减少在电信号的输入/输出处理期间的在上部芯片中产生的寄生电容。

因此,在本公开的一个实施方式中,可以提供一种半导体封装结构,其能够通过减小在堆叠在封装基板上的半导体芯片中产生的寄生电容来提高半导体封装的信号发送速度。

图7是示意性地示出根据本公开的另一实施方式的半导体封装件2的截面图。参照图7,半导体封装2可以具有进一步堆叠在以上参照图1描述的半导体封装1上的第二下部芯片1200、第二中介层1300和第二上部芯片1400。在这种情况下,第二下部芯片1200可以通过接合引线50c和50d电连接到封装基板100的连接焊盘110c和110d。

半导体封装件2可以包括封装基板100、设置在封装基板100上的第一堆叠结构2a以及设置在第一堆叠结构2a上的第二堆叠结构2b。第一堆叠结构2a可以包括第一下部芯片200、第一中介层300和第一上部芯片400。第二堆叠结构2b可以包括第二下部芯片1200、第二中介层1300和第二上部芯片1400。粘接层540可以设置在第一堆叠结构2a的第一上部芯片400和第二堆叠结构2b的第二下部芯片1200之间,以使得第一堆叠结构2a和第二堆叠结构2b可以彼此接合。

另外,半导体封装2可以包括:第一接合引线50a和50b,该第一接合引线50a和50b将第一堆叠结构2a的第一下部芯片200电连接到封装基板100;以及第二接合引线50c和50d,该第二接合引线50c和50d将第二堆叠结构2b的第二下部芯片1200电连接到封装基板100。

第一堆叠结构2a的第一下部芯片200、第一中介层300和第一上部芯片400的配置可以与上面参照图1描述的半导体封装1的下部芯片200、中介层300和上部芯片400的配置相同。也就是说,具有相同附图标记的组件是基本上相同的组件,因此这里将省略对这些组件的重复描述。

第二堆叠结构2b的第二下部芯片1200、第二中介层1300和第二上部芯片1400的配置可以与第一堆叠结构2a的第一下部芯片200、第一中介层300和第一上部芯片400的配置基本相同。作为示例,第二下部芯片1200的焊盘1210a、1210b、1220a和1220b可以具有与第一下部芯片200的焊盘210a、210b、220a和220b相同的配置。另外,第二下部芯片1200的引线接合焊盘1230a和1230b可以具有与第一下部芯片200的引线接合焊盘230a和230b相同的配置。另外,第二下部芯片1200的再分配线1240a和1240b可以具有与第一下部芯片200的再分配线240a和240b相同的配置。另外,第二上部芯片1400的焊盘1410a、1410b、1420a和1420b可以具有与第一上部芯片400的焊盘410a、410b、420a和420b相同的配置。另外,第二中介层1300的上部芯片连接焊盘1310a和1310b、第二通孔电极1330a和1330b以及下部芯片连接焊盘1320a和1320b可以具有与第一中介层300的上部芯片连接焊盘310a和310b、第一通孔电极330a和330b以及下部芯片连接焊盘320a和320b相同的配置。第二下部芯片1200和第二中介层1300可以通过第三凸块550彼此电连接,并且第二中介层1300和第二上部芯片1400可以通过第四凸块560彼此电连接。

第一下部芯片200可以通过接合引线50a和50b电连接到封装基板100。接合引线50a和50b可以将第一下部芯片200的引线接合焊盘230a和230b电连接到封装基板100的连接焊盘110a和110b。另一方面,在使用第一中介层300将第一上部芯片400连接至第一下部芯片200之后,可以通过第一下部芯片200将第一上部芯片400电连接至封装基板100。

第二下部芯片1200可以通过接合引线50c和50d电连接到封装基板100。接合引线50c和50d可以将第二下部芯片1200的引线接合焊盘1230a和1230b电连接到封装基板100的连接焊盘110c和110d。另一方面,在使用第二中介层1300连接到第二下部芯片1200之后,第二上部芯片1400可以经由第二下部芯片1200电连接到封装基板100。

参照图7,第一中介层300的边缘部分可以设置在从第一上部芯片400的边缘部分和第一下部芯片200的边缘部分沿横向方向(即,平行于x轴的方向)凹入的位置处。作为示例,第一中介层300的两个侧壁表面300e1和300e2二者可以分别设置在从第一上部芯片400的两个侧壁表面400e1和400e2二者以及第一下部芯片200的两个侧壁表面200e1和200e2二者沿横向方向(即,平行于x轴的方向)凹入的位置处。第二中介层1300的边缘部分可以设置在从第二上部芯片1400的边缘部分和第二下部芯片1200的边缘部分沿横向方向(即,平行于x轴的方向)凹入的位置处。作为示例,第二中介层1300的两个侧壁表面1300e1和1300e2二者可以设置在分别从第二上部芯片1400的两个侧壁表面1400e1和1400e2二者以及第二下部芯片1200的两个侧壁表面1200e1和1200e2二者沿横向方向(即,平行于x轴的方向)凹入的位置处。

在图7中,尽管公开了一种其中具有基本相同构造的两个堆叠结构2a和2b堆叠在封装基板100上的半导体封装结构,但是在一些其他实施方式中,堆叠在封装基板100上的堆叠结构的数量可以不限于此。也就是说,在其他实施方式中,可以实现其中在封装基板100上堆叠至少三个根据本公开的实施方式的堆叠结构的半导体封装。

如上所述,本公开的一个实施方式提供了一种具有依次堆叠在封装基板上的下部芯片、中介层和上部芯片的半导体封装。在半导体封装中,下部芯片可以使用引线接合连接到封装基板。上部芯片可以通过中介层的通孔电极连接到下部芯片,并且可以经由下部芯片电连接到封装基板。

在本公开的一个实施方式中,上部芯片可以通过中介层和下部芯片电连接到封装基板,而无需直接连接到封装基板。因此,为了与封装基板交换信号,上部芯片可以不应用与引线接合有关的输入/输出焊盘和输入/输出电路。结果,在半导体封装的操作期间,可以减小在上部芯片的输入/输出焊盘和输入/输出电路中产生的寄生电容。这样,本公开的一个实施方式可以提供一种能够减少在半导体芯片中产生的寄生电容的半导体封装结构,从而提高半导体封装的诸如信号发送速度的性能。如上所述,已经公开并在附图中示出了本公开的一个实施方式。根据本公开所提出的技术精神,可以进行各种其他修改。

相关申请的交叉引用

本申请要求于2019年11月29日提交的韩国专利申请第10-2019-0157705号的优先权,其全部内容通过引用合并于此。

- 还没有人留言评论。精彩留言会获得点赞!