用于光电子芯片的沟基光学组件的制作方法

1.本发明涉及光电子芯片,更具体而言,涉及包括波导芯(waveguide core)的结构以及制造包括波导芯的结构的方法。

背景技术:

2.光电子芯片用于许多应用和系统,包括但不限于数据通信系统和数据计算系统。光电子芯片将光学组件(例如波导芯和弯管)和电子组件(例如场效应晶体管)集成到统一的平台中。除其他因素外,通过将这两种类型的组件集成到统一平台中,可降低布局面积、成本和操作开销。

3.某些光电子芯片可以包括具有波导芯的光学组件,其水平布置在包含该电子组件的水平上方。这些波导芯可在形成电子组件后的工艺流程中形成。结果,用于形成这些波导芯的蚀刻工艺可能会由于遮罩(masking)不足而对该电子组件产生不利影响。

4.需要改进包括波导芯的结构以及制造包括波导芯的结构的方法。

技术实现要素:

5.在本发明的一实施例中,一种结构包括介电层和波导芯,该介电层具有包括第一侧壁和第二侧壁的沟槽,该波导芯位于该沟槽的该第一侧壁和第二侧壁之间的该沟槽内。该波导芯具有第一宽度,该沟槽具有位于该第一侧壁和第二侧壁之间的大于该波导芯的该第一宽度的第二宽度。

6.在本发明的一实施例中,一种方法包括沉积介电层于衬底上方,图案化包括第一侧壁和第二侧壁的该介电层中的沟槽,以及形成位于该沟槽的该第一侧壁和第二侧壁之间的该沟槽内的波导芯。该波导芯具有第一宽度,该沟槽具有位于该第一侧壁和第二侧壁之间的大于该波导芯的该第一宽度的第二宽度。

附图说明

7.并入本说明书并构成本说明书一部分的附图用于说明本发明的各种实施例,并且与上面给出的本发明的一般描述和下面给出的实施例的详细描述一起,用于解释本发明的实施例。在附图中,相似附图标记用于指代各视图中的相似特征。

8.图1为根据本发明的实施例所示的处于处理方法的初始制造阶段的包括结构的光电子芯片的横截面图。

9.图2为处于该处理方法的该初始制造阶段的该光电子芯片的不同部分的横截面图。

10.图3和图4分别为处于图1和图2之后的制造阶段的横截面图。

11.图5和图6分别为处于图3和图4之后的制造阶段的横截面图。

12.图7和图8分别为处于图5和图6之后的制造阶段的横截面图。

13.图7a为俯视图,其中,图7大致沿7-7线拍摄。

14.图9和图10分别为处于图7和图8之后的制造阶段的横截面图。

15.图11和图12是根据替换实施例的结构的横截面图。

具体实施方式

16.参考图1和图2,根据本发明的实施例,场效应晶体管10可位于绝缘体上硅(soi)晶片的区域中。soi晶片可包括设备层12、埋置绝缘体层14、以及通过埋置绝缘体层14与设备层12分离的衬底16。埋置绝缘体层14可由介电材料(例如二氧化硅)组成,设备层12和衬底16可以由单晶半导体材料(例如单晶硅)组成。

17.波导芯18可位于soi晶片的不同区域中。波导芯18可以通过以下方法形成:利用光刻和蚀刻工艺图案化设备层12的单晶半导体材料,其中,蚀刻掩膜形成在设备层12上方,并通过蚀刻工艺(例如反应离子蚀刻)蚀刻已遮罩的设备层12。波导芯18与埋置绝缘体层14直接接触。波导芯18在其相对侧壁之间的横向方向具有宽度w1。如图所示,波导芯18具有脊状结构。或者,波导芯18可以具有包括附加平板层(added slab layer)的肋结构。

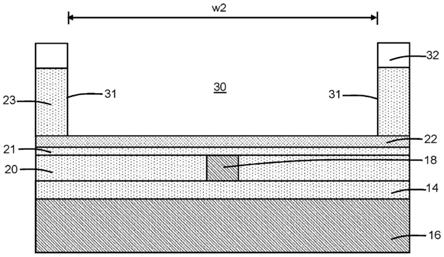

18.波导芯18可嵌入介电层20中。介电层20沉积在波导芯18和埋置绝缘体层14上方,然后利用化学机械抛光进行平坦化以提供平坦顶面。介电层20可以由诸如二氧化硅之类的介电材料组成。介电层20还可用于在场效应晶体管10的设备层12中提供浅沟槽隔离。

19.介电层21、22、23可位于波导芯18和介电层20上方的异质多层堆叠中。介电层22可以具有与介电层21、23不同的组成。在一实施例中,介电层21、23可由例如二氧化硅组成,介电层22可以由例如氮化硅组成。介电层21的总厚度可以包括来自场效应晶体管10的栅极介电层的部分的贡献,该部分也沉积在包括波导芯18和附加沉积层的区域中。比介电层21或介电层22更厚的介电层23具有足以在随后的蚀刻工艺中保护场效应晶体管10的厚度。在一实施例中,介电层23的厚度可在约50纳米至约500纳米之间。

20.在一替换实施例中,介电层22可从异质多层堆叠中省略,并且介电层21、23可组成单个介电层,随后在其上形成波导芯,如下文所述。

21.场效应晶体管10是通过前段(front-end-of-line)cmos工艺制造的,其可包括通过沉积层堆叠并使用光刻和蚀刻图案化该层堆叠而形成的栅极电极24和栅极介电质。栅极电极24可以由栅极导体组成,例如掺杂的多晶硅(即,多晶硅),栅极介电质可以由例如二氧化硅的电绝缘体组成。场效应晶体管10可包括其他元件,例如源/漏区域26、源/漏区域26上的硅化物、晕区、轻掺杂漏极延伸部分、栅极电极24上的非导电侧壁间隔件、由区域上方和场效应晶体管10之上的氮化硅组成的应力衬垫28。应力衬垫28是不同于介电层22的不同层。

22.参考图3、图4,其中相同的附图标记用于表示图1、图2中的相似特征,在后续制造阶段,沟槽30可在包括波导芯18的区域中的介电层23中被图案化。为此,在soi晶片的两个区域的介电层23上方通过光刻工艺形成蚀刻掩膜32。利用蚀刻工艺蚀刻(例如反应离子蚀刻)并移除介电层23的未遮罩部分,从而形成沟槽30。蚀刻工艺可选择在完全击穿介电层23之后停止在介电层22的材料上。沟槽30在其相对侧壁31之间具有厚度w2,该宽度w2在图案化期间被选择,并且该宽度大于波导芯18的宽度。

23.参考图5、图6,其中相同的附图标记用于表示图3、图4中的相似特征,在后续制造阶段,包括介电层33、34、35的异质层堆叠形成于soi晶片的区域上方。介电层34可以由与介

电层33、35不同的介电材料组成。在一实施例中,介电层33、35可由例如二氧化硅组成,介电层34可由例如氮化硅组成。在替代实施例中,层34可由不同种类的材料组成,例如多晶硅(即多晶硅),而不是介电材料。介电层34可比介电层33、35中的任一层显著更厚。

24.在soi晶片的两个区域的介电层35上方通过光刻工艺形成蚀刻掩膜25。蚀刻掩膜25具有被选择为确定后续蚀刻的介电层34的尺寸的宽度,如下文所述。

25.参考图7、图7a、图8,其中,相同的附图标记表示图5、图6中的相似特征,在后续制造阶段,介电层35可借由蚀刻工艺图案化,同时借由该蚀刻掩膜25遮罩以形成具有蚀刻掩膜25的给定尺寸并位于介电层34上方的的硬掩膜。在剥离蚀刻掩膜25之后,使用蚀刻工艺对介电层34进行图案化以形成具有硬掩膜的尺寸的波导芯36。通过蚀刻工艺从包括波导芯18、36的soi晶片的区域移除介电层34的未遮罩部分。介电层34、35两者通过蚀刻工艺从包括场效应晶体管10的soi晶片的区域完全移除。蚀刻工艺可以停止在沟槽30内的介电层33的材料上,并停止在沟槽30外的介电层23和33上。

26.波导芯36可直接定位在波导芯18的正上方,介电层21、22和介电层33介于它们之间。波导芯36具有侧壁37以及表示分隔相对侧壁37的距离的宽度w3。波导芯36位于沟槽30的侧壁31之间,波导芯36的相对侧壁37与沟槽30的相应最近侧壁31间隔距离d。在一实施例中,波导芯36可对称地位于沟槽30的侧壁31之间,相对侧壁37与沟槽30的最近侧壁31间隔基本相同的距离。沟槽30的侧壁31和波导芯36的侧壁37的间隔关系定义了布置在相邻一对侧壁31,37之间的未填充间隙。

27.波导芯18的中心线19可以平行于或基本平行于波导芯36的中心线39。如果对称定位,波导芯18的中心线19可以横向定位(例如,在z方向)成在垂直方向(即y方向)上位在波导芯36的中心线39的正上方。在一替换实施例中,波导芯36可不对称地位于沟槽30的侧壁31之间。

28.在一实施例中,波导芯36的宽度可以大于波导芯18的宽度。在一实施例中,沟槽30的宽度可在使用期间通过波导芯36传播并由其引导的光的波长的约1倍至约3倍的范围内。在一实施例中,沟槽30的宽度可在使用期间通过波导芯36传播并由其引导的光的波长的约1.2倍至约2.3倍的范围内。光的示例性波长可以在400纳米到1260纳米的范围内。

29.由介电层34的介电材料组成的残留轨道(residual rails)38通过蚀刻工艺形成为介电层23中的沟槽30的下角中的介电层22上方的缺陷或伪影。轨道38表示不容易通过蚀刻工艺被移除的介电层34的介电材料。选择沟槽30的宽度和波导芯36的宽度,以使轨道38从波导芯36横向位移最小距离。介电层23中的沟槽30消除了波导芯18上方的介电层23的厚度,以促进波导芯18、36之间的有效耦合,同时在形成波导芯36时提高场效应晶体管10免受蚀刻损伤的保护。可以选择轨道38与波导芯18、36之间的偏移距离,以使轨道38在使用期间对于波导芯18和波导芯36之间的光学耦合的影响可以忽略不计。

30.波导芯36提供可作为波导的部分的光学组件,以在光电子芯片上路由光信号。可替换的,波导芯36也可实施于不同类型的光学组件中,例如,谐振器或光学开关。在实施例中,波导芯36可实施为沿其长度呈锥形的波导椎管、弯曲的波导管、或直的波导段,且沟槽30的形状可以调整以反映特定的形状。

31.参考图9、图10,其中,相同的附图标记表示图7、图8中的相似特征,在后续制造阶段,介电层40形成在介电层23上方以及波导芯36上方的沟槽30内。介电层40可由通过化学

气相沉积法沉积的介电材料(例如二氧化硅)所组成。例如,介电层40可由使用臭氧和正硅酸乙酯(teos)作为反应物的化学气相沉积法沉积的二氧化硅组成。介电层40可以是层间介电层,其包含延伸到光电子芯片上的电子组件(例如场效应晶体管10)的接触件。

32.通常由附图标记42指示的后段工艺(back-end-of-line)堆叠可以形成在介电层40上方。后段工艺堆叠42可以包括由诸如掺杂的氧化硅之类的介电材料组成的一个或多个层间介电层。后段工艺堆叠42还可包括例如由铜、钨或钴组成的布线,这些布线可以布置在一层或多层层间介电层中,并可耦接至介电层40中的接触件。

33.参考图11,其中,相同的附图标记表示图9中的相似特征,根据替代实施例,波导芯18可在介电层20内重新定位,使得波导芯18不再直接位于波导芯36的正下方。波导芯18和波导芯36之间的横向偏移可以有效地防止波导芯18和波导芯36之间的光耦合。

34.参考图12,其中,相同的附图标记表示图9中的相似特征,根据替代实施例,介电层22可以从结构中消除。介电层33也可以被消除,因为当介电层23被图案化以提供波导芯36时,介电层21作为蚀刻停止层。波导芯36与介电层22直接接触。波导芯36直接位于波导芯18的正上方,其中只有介电层21介于它们之间。介电层21可以加厚以在波导芯18和波导芯36之间提供足够的隔离。

35.上述方法用于制造集成电路芯片。由此产生的集成电路芯片可由制造商以原始晶片形式(例如,作为具有多个未封装芯片的单晶片)、裸芯片或封装形式予以分布。该芯片可以与其他芯片、分立式电路元件和/或其他信号处理设备集成,以作为中间产品或最终产品的部分。最终产品可以是包括集成电路芯片的任何产品,例如具有中央处理器的计算机产品或智能手机。

36.本文中提及的近似语言修饰的术语的引用,诸如“大约”,“近似”和“基本上”,不限于所指定的精确值。近似语言可能与用于测量该值的仪器的精度相对应,除非仪器的精度另有规定,否则可表示规定值的+/-10%。

37.本文中针对诸如“垂直”、“水平”等术语的引用是通过示例而非限制的方式来建立参考框架的。本文使用的术语“水平”被定义为与半导体基本的常规平面平行的平面,而不管其实际的三维空间取向如何。术语“垂直”和“法线”是指垂直于水平方向的方向,正如先前所定义的。术语“横向”指示该水平面的方向。

38.一特征“连接”或“耦合”至另一特征可以直接连接或耦合至另一特征,或者可替代的,可以存在一个或多个中间特征。如果不存在中间特征,则一个特征可以“直接连接”或“直接耦合”至另一特征。如果存在至少一个中间特征,则一个特征可以“间接连接”或“间接耦合”至另一特征。一个特征位于另一特征“上”或“接触”另一特征可以直接位于另一特征上或直接接触另一特征,或者可替代的,可以存在一个或多个中间特征。如果不存在中间特征,则一个特征可直接位于另一特征上或直接接触另一特征。如果存在至少一个中间特征,则一个特征可以间接位于另一个特征上或间接接触另一个特征。

39.本发明的各种实施例的描述是为了说明的目的而提出的,但并不打算是详尽的或仅限于所公开的实施例。在不脱离所描述的实施例的范围和精神的情况下,对于本领域的普通技术人员来说,许多修改和变化是显而易见的。本文使用的术语被选择用于最好地解释实施例的原理、实际应用或相对于市场上发现的技术的改进,或者使本领域的其他技术人员能够理解本文公开的实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1