半导体装置的制作方法

半导体装置

1.[相关申请]

[0002]

本技术享受以日本专利申请2021-47800号(申请日:2021年3月22日)为基础申请的优先权。本技术通过参考该基础申请包括基础申请的全部内容。

技术领域

[0003]

本发明的实施方式涉及半导体装置。

背景技术:

[0004]

包含光耦合型绝缘电路的光继电器,能够使用发光元件将输入电信号变换为光信号,在由受光元件接受后输出电信号。因此,光继电器能够在输入输出间绝缘的状态下传输电信号。

[0005]

在对半导体集成电路等进行检查的半导体测试器中,多使用交流负载用的光继电器。伴随着进一步的dram(dynamic random access memory,动态随机存取存储器)等的宽频带化的要求,要求具备使频率比几ghz更高的高频信号以低损耗通过的光继电器的半导体装置。

技术实现要素:

[0006]

实施方式提供可靠性高的半导体装置。

[0007]

实施方式的半导体装置具备:安装基板,设置有第一电极焊盘及第二电极焊盘;半导体元件,设置于安装基板上,具有支承基板、设置于支承基板的朝向安装基板的面的第三电极焊盘及设置于支承基板的朝向安装基板的面的第四电极焊盘,在支承基板和第三电极焊盘上设置有第一狭缝,在支承基板和第四电极焊盘上设置有第二狭缝;第一导电性接合剂,将第一电极焊盘和第三电极焊盘连接;以及第二导电性接合剂,将第二电极焊盘和第四电极焊盘连接。

附图说明

[0008]

图1是实施方式的半导体装置的示意剖视图。

[0009]

图2是实施方式的半导体装置的示意俯视图。

[0010]

图3是实施方式的布线基板的示意立体图。

[0011]

图4是实施方式的工序示意图。

[0012]

图5是实施方式的布线基板的示意图。

[0013]

图6是实施方式的半导体装置的示意俯视图。

[0014]

图7是实施方式的布线基板的示意图。

[0015]

图8是实施方式的半导体装置的示意剖视图。

[0016]

图9是实施方式的光继电器的示意立体图。

[0017]

图10是实施方式的光继电器的结构图。

具体实施方式

[0018]

以下,参照附图对本发明的实施方式进行说明。另外,在以下的说明中,有时对相同或类似的部件标注相同的附图标记,对于已说明过一次的部件省略其说明。

[0019]

在本说明书中,为了表示零部件等的位置关系,将附图的上方向记述为“上”,将附图的下方向记述为“下”。在本说明书中,“上”、“下”的概念未必是表示与重力的方向的关系的用语。

[0020]

说明书中的物性是25℃的大气气氛下的值。

[0021]

(第一实施方式)

[0022]

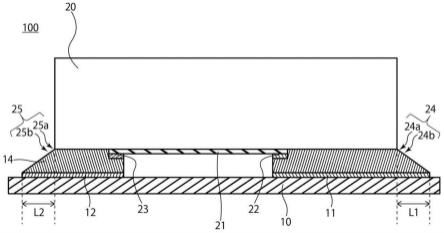

图1是实施方式的半导体装置的示意剖视图。图2是实施方式的半导体装置的示意俯视图。

[0023]

半导体装置100具备安装基板10、半导体元件20、第一导电性接合剂13和第二导电性接合剂14。

[0024]

安装基板10是与半导体元件20连接的基板。安装基板10例如是印刷基板。在安装基板10的朝向半导体元件20的面上设置有第一电极焊盘11以及第二电极焊盘12。两部分的第一电极焊盘11和两部分的第二电极焊盘12设置于安装基板10的表面上。

[0025]

半导体元件20设置于安装基板10上。半导体元件20具有支承基板21、第三电极焊盘22以及第四电极焊盘23。半导体元件20经由第一导电性接合剂13及第二导电性接合剂14载置于安装基板10。半导体元件20例如是光继电器。半导体元件20在朝向安装基板10的面上具有支承基板21。在支承基板21的朝向安装基板10的面上设置有两部分的第三电极焊盘22和两部分的第四电极焊盘23。

[0026]

安装基板10的第一电极焊盘11与半导体元件20的第三电极焊盘22对置。第一电极焊盘11和第三电极焊盘22在安装基板10的朝向半导体元件20的面的垂直方向上重叠。从通过肉眼观察来确认安装基板10与半导体元件20的接合部分的观点出发,优选的是,在与安装基板10的朝向半导体元件20的面垂直的方向上将第一电极焊盘11和半导体元件20重叠时(从半导体元件20侧向安装基板10方向透视时),第一电极焊盘11的一部分在安装基板10的面方向上比半导体元件20的外周边向外侧伸出。

[0027]

安装基板10的第二电极焊盘12与半导体元件20的第四电极焊盘23对置。第二电极焊盘12和第四电极焊盘23在安装基板10的朝向半导体元件20的面的垂直方向上重叠。从通过肉眼观察来确认安装基板10与半导体元件20的接合部分的观点出发,优选的是,在从安装基板10的朝向半导体元件20的面垂直的方向上将第二电极焊盘12和半导体元件20重叠时(从半导体元件20侧向安装基板10方向透视时),第二电极焊盘12的一部分在安装基板10的面方向上比半导体元件20的外周边向外侧伸出。

[0028]

优选在支承基板21的角部不设置第三电极焊盘22和第四电极焊盘23。

[0029]

第一导电性接合剂13设置于安装基板10与半导体元件20之间,将半导体元件20与安装基板10电连接。安装基板10的第一电极焊盘11和半导体元件20的第三电极焊盘22通过第一导电性接合剂13连接。第一导电性接合剂13例如是焊料。从提高安装基板10与半导体元件20的连接的可靠性的观点出发,第一导电性接合剂13优选还设置于第一狭缝24内。

[0030]

第二导电性接合剂14设置于安装基板10与半导体元件20之间,将半导体元件20与安装基板10电连接。安装基板10的第二电极焊盘12和半导体元件20的第四电极焊盘23通过

第二导电性接合剂14连接。第二导电性接合剂14例如是焊料。从提高安装基板10与半导体元件20的连接的可靠性的观点出发,第二导电性接合剂14优选还设置于第二狭缝25内。

[0031]

在半导体元件20的第三电极焊盘22和支承基板21上设置有第一狭缝24。第三电极焊盘22的侧面和支承基板21的侧面是半导体元件20的侧面的一部分。第三电极焊盘22的侧面与支承基板21的侧面连接。第三电极焊盘22和支承基板21层叠。第三电极焊盘22的朝向支承基板21的面与支承基板21的朝向第三电极焊盘22的面直接接触。第三电极焊盘22的朝向支承基板21的面的整个面与支承基板21的朝向第三电极焊盘22的面直接接触。

[0032]

如图3的支承基板21的示意图所示,第一狭缝24优选从半导体元件20的外周边朝向支承基板21的中央方向设置。即,第一狭缝24的开口部,位于半导体元件20的外周边侧。由于接合时的表面张力,第一导电性接合剂13容易侵入第一狭缝24,另外,在半导体元件20的外周边侧有第一狭缝24的开口部,从而第一导电性接合剂13容易从开口部侧扩展到外侧,容易确认半导体元件20与安装基板10的接合部分。若第一狭缝24在支承基板21的中央方向开口,则有时第一导电性接合剂13在中央方向扩展,从而容易发生非意图的短路,另外,会成为半导体装置100的频率特性降低的原因。此外,在本实施方式中,例如将设置于支承基板21的第一狭缝24a和设置于第三电极焊盘22的第一狭缝24b一并设为第一狭缝24。

[0033]

若考虑频率特性及加工性,则优选的是,设置于支承基板21的第一狭缝24的形状与设置于第三电极焊盘22的第一狭缝24的形状相同(大致相同)。第一狭缝24在第三电极焊盘22和支承基板21的厚度方向上贯通,经由第一狭缝24将半导体元件20内的部件与安装基板10电连接。

[0034]

从通过肉眼观察来确认安装基板10与半导体元件20的接合部分的观点出发,在与安装基板10的朝向半导体元件20的面垂直的方向上将第一导电性接合剂13和半导体元件20重叠时(从半导体元件20侧向安装基板10方向透视时),第一导电性接合剂13的一部分优选在安装基板10的面方向上比半导体元件20的外周边向外侧伸出0.05mm以上且0.2mm以下的长度(l1),更优选伸出0.1mm以上且0.15mm以下的长度(l1)。

[0035]

第一导电性接合剂13优选具有从第三电极焊盘22向第一电极焊盘11的外周边倾斜的表面。更具体而言,第一导电性接合剂13优选具有从第一狭缝24的开口部朝向第一电极焊盘11的外周边倾斜的表面。通过对倾斜的表面进行确认,能够评价半导体元件20与安装基板10的连接。第一导电性接合剂13的倾斜的表面的形状有时部分地包含曲面。

[0036]

第一狭缝24的内部优选由cu等金属镀敷。第一狭缝24的内部的镀敷形成于形成有第一狭缝24的支承基板21的内侧面、形成有第一狭缝24的第三电极焊盘22的内侧面、或者形成有第一狭缝24的支承基板21的内侧面和形成有第一狭缝24的第三电极焊盘22的内侧面这两者。

[0037]

第一狭缝24的高度优选为支承基板21的厚度与第三电极焊盘22的厚度之和。第一狭缝24的高度例如为10μm以上且100μm以下,例如优选为25μm以上且75μm以下。第一狭缝24的宽度(开口部的宽度)优选为具有第一狭缝24的开口部的第三电极焊盘22的侧面的宽度的一半以下。由于第一狭缝24具有长度,因此如果第一狭缝24的宽度过宽,则支承基板21的强度降低。另外,若第一狭缝24的宽度过窄,则无法获得设置第一狭缝24的效果。因此,具体而言,第一狭缝24的宽度例如为5μm以上且100μm以下,例如优选为50μm以上且75μm以下。

[0038]

第一狭缝24与圆筒状的通孔不同,在支承基板21的面方向上延伸。经由与具有比

通孔大的面的第一狭缝24相接触的第一导电性接合剂13将安装基板10与半导体元件20连接,因此能够提高连接的可靠性。第一狭缝24的长度比第一狭缝24的高度长,且比第一狭缝24的宽度长。第一狭缝24的长度优选为第一狭缝24的高度的4倍以上,且为第一狭缝24的宽度的4倍以上。

[0039]

在半导体元件20的第四电极焊盘23和支承基板21设置有第二狭缝25。第四电极焊盘23的侧面和支承基板21的侧面是半导体元件20的侧面的一部分。第四电极焊盘23的侧面与支承基板21的侧面连接。第四电极焊盘23和支承基板21层叠。第四电极焊盘23的朝向支承基板21的面与支承基板21的朝向第四电极焊盘23的面直接接触。第四电极焊盘23的朝向支承基板21的面的整个面与支承基板21的朝向第四电极焊盘23的面直接接触。

[0040]

如图3的支承基板21的示意图所示,第二狭缝25优选从半导体元件20的外周边朝向支承基板21的中央方向设置。即,第二狭缝25的开口部位于半导体元件20的外周边侧。由于接合时的表面张力,第二导电性接合剂14容易侵入第二狭缝25,另外,在半导体元件20的外周边侧具有第二狭缝25的开口部,从而第二导电性接合剂14容易从开口部侧扩展到外侧,容易确认半导体元件20与安装基板10的接合部分。若第二狭缝25在支承基板21的中央方向开口,则有时第二导电性接合剂14在中央方向扩展,从而容易发生非意图的短路,另外,会成为半导体装置100的频率特性降低的原因。此外,在本实施方式中,例如将设置于支承基板21的第二狭缝25a和设置于第三电极焊盘22的第二狭缝25b一并设为第二狭缝25。

[0041]

若考虑频率特性及加工性,则优选的是,设置于支承基板21的第二狭缝25的形状与设置于第四电极焊盘23的第二狭缝25的形状相同(大致相同)。第二狭缝25在第四电极焊盘23和支承基板21的厚度方向上贯通,经由第二狭缝25将半导体元件20内的部件与安装基板10电连接。

[0042]

从通过肉眼观察来确认安装基板10与半导体元件20的接合部分的观点出发,在与安装基板10的朝向半导体元件20的面垂直的方向上将第二导电性接合剂14和半导体元件20重叠时(从半导体元件20侧向安装基板10方向透视时),第二导电性接合剂14的一部分优选在安装基板10的面方向上比半导体元件20的外周边向外侧伸出0.05mm以上且0.1mm以下的长度(l2),更优选伸出0.1mm以上且0.15mm以下的长度(l2)。

[0043]

第二导电性接合剂14优选具有从第四电极焊盘23向第二电极焊盘12的外周边倾斜的表面。更具体而言,第二导电性接合剂14优选具有从第二狭缝25的开口部朝向第二电极焊盘12的外周边倾斜的表面。通过对倾斜的表面进行确认,能够评价半导体元件20与安装基板10的连接。第二导电性接合剂14的倾斜的表面的形状有时部分地包含曲面。

[0044]

第二狭缝25的内部优选由cu等金属镀敷。第二狭缝25的内部的镀敷形成于形成有第二狭缝25的支承基板21的内侧面、形成有第二狭缝25的第四电极焊盘23的内侧面、或者形成有第二狭缝25的支承基板21的内侧面和形成有第二狭缝25的第四电极焊盘23的内侧面这两者。

[0045]

第二狭缝25的高度优选为支承基板21的厚度与第四电极焊盘23的厚度之和。第二狭缝25的高度例如为10μm以上且100μm以下,例如优选为25μm以上且75μm以下。第一狭缝24的宽度(开口部的宽度)优选为具有第二狭缝25的开口部的第四电极焊盘23的侧面的宽度的一半以下。由于第二狭缝25具有长度,因此如果第二狭缝25的宽度过宽,则支承基板21的强度降低。另外,如果第二狭缝25的宽度过窄,则无法获得设置第二狭缝25的效果。因此,具

体而言,第二狭缝25的宽度例如为25μm以上且100μm以下,例如优选为50μm以上且100μm以下。

[0046]

第二狭缝25与圆筒状的通孔不同,在支承基板21的面方向上延伸。经由与具有比通孔大的面的第二狭缝25相接触的第二导电性接合剂14将安装基板10与半导体元件20连接,因此能够提高连接的可靠性。第二狭缝25的长度比第二狭缝25的高度长,且比第二狭缝25的宽度长。第二狭缝25的长度优选为第二狭缝25的高度的4倍以上,且为第二狭缝25的宽度的4倍以上。

[0047]

具备实施方式的狭缝的支承基板21例如能够通过对图4的工序示意图所示的部件进行加工而得到。准备支承基板21上设置有长的电极焊盘22(23)的部件,形成狭缝,在长的电极焊盘22(23)侧的相反侧的支承基板21的面也设置电极焊盘之后,进行切割,从而能够得到半导体元件20的支承基板21。通过使用激光,形成将支承基板21和电极焊盘22(23)贯通的狭缝。

[0048]

狭缝可以相对于1个电极焊盘而设置两个以上。另外,狭缝也可以是具有在电极焊盘中弯折的两个开口部的方式。具体而言,如图5的支承基板21的示意图所示,第一狭缝24在第三电极焊盘22中弯折成直角,在半导体元件20的侧面方向上具备第二个开口部。另外,第二狭缝25在第四电极焊盘23中弯折成直角,在半导体元件20的侧面方向上具有第二个开口部。若将具有该方式的支承基板21的半导体元件20用于半导体装置100,则如图6的俯视示意图所示,从半导体元件20的4个侧面中的任一个侧面朝向安装基板10侧连接第一导电性接合剂13、第二导电性接合剂14、或者第一导电性接合剂13和第二导电性接合剂14这两者。在狭缝弯折的情况下,到狭缝弯折的部分为止的长度为狭缝的长度。

[0049]

第一狭缝24及第二狭缝25可以分别在第三电极焊盘22和第四电极焊盘23的中心通过,也可以在上下方向上错开(偏移)。在为如图5的示意图那样的第一狭缝24及第二狭缝25的情况下,不仅是上下,左右也可以错开。

[0050]

另外,在支承基板21上,不仅能够设置第一狭缝24及第二狭缝25,还能够进一步设置通孔26。

[0051]

(第二实施方式)

[0052]

第二实施方式是第一实施方式的半导体装置100的变形例。图8中示出了第二实施方式的半导体装置200的剖视图。第二实施方式的半导体元件20是光继电器。图9表示半导体元件20的示意立体图。

[0053]

光继电器20具备:在上表面具有受光面的受光元件31、向受光面照射光的发光元件32、以及作为开关元件的mosfet33(34)。

[0054]

光继电器20具有:mosfet33(34),粘接于输出端子部41、42;受光元件31,粘接于裸片焊盘部35,在上表面具有受光面;发光元件32,对受光面照射光;粘接层36,具有透光性和绝缘性,将发光元件32粘接在受光元件31的上表面;以及第一密封树脂90。发光元件32例如能够使用led(light emitting diode:发光二极管)等。另外,受光元件31能够使用光电二极管、光电晶体管、受光ic等。

[0055]

在本图中设为,mosfet33(34)包含源极

·

公共连接的两个元件。但是,本发明并不限定于此,也可以是1个mosfet。若将各个mosfet33(34)的芯片背面作为漏极,则输出端子部41、42与各个mosfet33(34)的漏极连接。

[0056]

第一密封树脂90覆盖受光元件31、发光元件32、mosfet33(34)、聚酰亚胺基板21的第一面10a,保护内部。发光元件32也可以进一步被第二密封树脂91密封。

[0057]

支承基板21优选使用聚酰亚胺基板。聚酰亚胺基板21在矩形的第一面侧设置有mosfet33(34)、受光元件31和发光元件32等,在与第一面相反的第二面侧设置有第三电极焊盘22和第四电极焊盘23。第三电极焊盘22设置有第一狭缝24。在第四电极焊盘23设置有第二狭缝25。

[0058]

聚酰亚胺基板21优选设为10μm以上且120μm以下的厚度。这样,通过使用极薄的聚酰亚胺基板21,能够提高从15ghz到30ghz这样的高频频带中的通过特性。从使高频频带中的通过特性的观点出发,聚酰亚胺基板21的厚度更优选为10μm以上且100μm以下。从提高20ghz以上的进一步的高频频带中的通过特性的观点出发,聚酰亚胺基板21的厚度优选为10μm以上且60μm以下,更优选为10μm以上且30μm以下。通过使聚酰亚胺基板21的厚度变薄,例如设为60μm以下,从而优选的是,频率更高的高频频带的通过特性进一步提高。由于聚酰亚胺基板21薄,因此能够提高高频通过特性。

[0059]

半导体元件20作为输出端子例如具有两个输出端子部41、42。输出端子部41、42的厚度优选为5μm以上且50μm以下。输出端子部41、42是电极焊盘,与在支承基板21的第二面侧设置的第三电极焊盘22电连接。在输出端子部41、42未设置第一狭缝24。

[0060]

半导体元件20例如具有两个输入端子部43、44作为输入端子。输入端子部43、44是电极焊盘,与在支承基板21的第二面侧设置的第四电极焊盘23电连接。输入端子部43、44的厚度优选为5μm以上且50μm以下。在输入端子部43、44未设置第二狭缝25。

[0061]

输入端子部43、44、输出端子部41、42以及裸片焊盘部35能够设为,由在聚酰亚胺基板21的表面设置的cu箔以及层叠于其上的ni、au等镀敷层等构成。另外,从上方观察时,输入端子部43、44、输出端子部41、42以及裸片焊盘部35在聚酰亚胺基板21上相互分离并绝缘。

[0062]

输入端子部43经由接合线bw1与发光元件32的阴极的焊盘81f电连接。

[0063]

输入端子部44经由接合线bw2与发光元件32的阳极的焊盘81e电连接。

[0064]

受光元件31和mosfet33、34的栅极和源极经由接合线bw3、bw4、bw6、bw7电连接。受光元件的焊盘81a、81b、81c、81d经由接合线bw3、bw4、bw6、bw7与mosfet33、34的焊盘81g、81h、81k、81l电连接。

[0065]

mosfet33(源极)和mosfet34(源极)分别经由将焊盘81i和焊盘81j连接的接合线bw5电连接。

[0066]

从得到高频通过特性的半导体装置200的观点出发,优选的是,第一导电性接合剂13和受光元件31在与安装基板10的朝向半导体元件20的面垂直的方向上不重叠,第二导电性接合剂14和受光元件31在与安装基板10的朝向半导体元件20的面垂直的方向上不重叠。

[0067]

优选的是,第一狭缝24的长度比从mosfet33、34的第一狭缝24的开口部所在的半导体元件20的侧面到mosfet33、34的第一狭缝24的开口部所在的半导体元件20的侧面的相反侧的侧面为止的距离短。若第一狭缝24过长,则第一导电性接合剂13也容易位于发光元件32、受光元件31之下,有时对高频通过特性造成不良影响。

[0068]

优选的是,第一狭缝24朝向与安装基板10的朝向半导体元件20的面垂直的方向地与mosfet33、34的焊盘81g、81h、81k、81l重叠,第一狭缝24与mosfet33、34的焊盘81g、81h、

81k、81l重叠,从而mosfet33、34的焊盘81g、81h、81k、81l与安装基板10的第一电极焊盘11之间的布线距离变短。从上述观点出发,优选的是,第一狭缝24的长度为从光电继电器20的侧面到mosfet33、34的第一狭缝24的开口部侧的焊盘81i、81j的距离以上、且为从光电继电器20的侧面到mosfet33、34的第一狭缝24的开口部侧的相反侧的焊盘81g、81h、81k、81l为止的距离以下。

[0069]

优选的是,第二狭缝25朝向与安装基板10的朝向半导体元件20的面垂直的方向地、与输入端子部43、44的接合线bw1、bw2的连接面重叠,第二狭缝25与输入端子部43、44的接合线bw1、bw2的连接面重叠,从而输入端子部43、44与安装基板10的第二电极焊盘12之间的布线距离变短。

[0070]

图10是第二实施方式的光继电器的结构图。

[0071]

受光元件31还能够具有控制电路31a。控制电路31a分别与光电二极管阵列31b的第一电极和第二电极连接。若采用这样的结构,则能够将电压供给至源极

·

公共连接的mosfet33各自的栅极。另外,控制电路31a包含电阻等,在mosfet33从接通转变为截止的情况下能够使其放电而缩短下降时间。

[0072]

mosfet33、34例如能够设为n沟道增强型。在图10中,mosfet33的栅极g与光电二极管31b的阳极连接。另外,各个源极s与光电二极管31b的阴极连接,各个漏极d与输出端子部41、42连接。

[0073]

在光信号接通时,mosfet33、34都接通,经由输出端子部41、42与包含电源、负载的外部电路连接。另一方面,在光信号断开时,mosfet33、34都断开,与外部电路被切断。若设为源极

·

公共连接,则能够进行线性输出,高频信号的切换变得容易。

[0074]

两个mosfet33、34被源极

·

公共连接,在接通的情况下,高频信号被供给至负载。例如,若将两个源极电极s之间连接的接合线的数量增加到2根以上,则能够降低源极电感。另外,若使2根以上的接合线不平行,则能够进一步降低源极电感。进而,若使mosfet33、34侧的接合线的直径比发光元件32侧的接合线的直径大,则能够降低布线电感。其结果,能够降低传输损耗。

[0075]

使用了实施方式的光继电器20的半导体装置,能够降低20ghz以上的高频信号传输损失,进而可靠性高。因此,能够高精度且高速地测定包含下一代标准的超高速dram在内的半导体装置的高频特性。

[0076]

这些光继电器能够广泛地用于包含检查ic等的半导体测试器在内的产业用设备等的半导体装置。

[0077]

对本发明的几个实施方式进行了说明,但这些实施方式是作为例子而提示的,并不意图限定发明的范围。这些新的实施方式能够以其他各种方式实施,在不脱离发明的主旨的范围内,能够进行各种省略、置换、变更。这些实施方式及其变形包含在发明的范围或主旨中,并且包含在权利要求书所记载的发明及其等同的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1