击穿电压可调节的SCR型ESD保护结构的制作方法

击穿电压可调节的scr型esd保护结构

技术领域

1.本发明涉及半导体技术领域,尤其是一种击穿电压可调节的scr型esd保护结构。

背景技术:

2.现有技术中,使用最多的esd保护结构是pn结二极管、ggnmos、gdpmos、scr、npn等结构。其中ggnmos与gdpmos及其衍生的grnmos、gcnmos等是一种应用最广泛的esd保护结构,但是由于其器件面积大,鲁棒性较弱,特别是在高压应用时由于耐压不足需叠加使用,导致其面积过大使设计者很难接受;npn管做esd保护结构在芯片中也较为常见,但是由于其触发电压和npn管本身的集电结击穿电压紧密相关,其存在触发电压高,触发电压由工艺本身决定,不能灵活调整。

3.图1为常见的scr保护结构图,可看做是两个双极管,n-well(n阱区)里面的p+(p+掺杂区)作为发射极,n-well作为基区,p-well(p阱区)作为集电极,这就构成了一个pnp晶体管,另一个npn晶体管是p-well里面的n+(n+掺杂区)做发射极,p-well做基区,n-well做集电极,其原理图如图2所示,当scr作为esd保护电路时,它是作为一个两端器件被连接,阴极(cathode)和n-well连接,阳极(anode)和p-well连接。当n-well和p-well之间的pn结雪崩击穿才能触发scr,当n-well和p-well发生雪崩击穿时,击穿电流流过电阻rnwell和电阻rpwell使pnp管和npn管均导通形成放电回路scr。其触发电压定义为n-well和p-well之间的雪崩击穿电压,该电压由工艺决定,不同工艺中由于nwell、pwell浓度不同所以击穿电压也略有不同;在cmos工艺中scr的电流电压曲线如图3所示。

技术实现要素:

4.本发明目的在于提供一种击穿电压可调节的scr型esd保护结构,能够有效提升scr型esd保护结构在不同环境下的适用性。

5.实现本发明目的的技术方案:

6.一种击穿电压可调节的scr型esd保护结构,包括设置于同一p型衬底上的pnp管(t1)和npn管(t2),所述pnp管(t1)基极接所述npn管(t2)集电极,所述pnp管(t1)集电极接所述npn管(t2)基极,所述pnp管(t1)发射极接电源阳极,所述pnp管(t1)基极和所述npn管(t2)集电极经第一电阻(rnwell)接电源阳极,所述npn管(t2)发射极接电源阳极,所述npn管(t2)基极和所述pnp管(t1)集电极经第二电阻(rpwell)接电源阴极,还包括用于调节击穿电压的稳压二极管(d3),所述稳压二极管(d3)与所述pnp管(t1)和npn管(t2)设置于同一p型衬底上,所述稳压二极管(d3)阳极与所述npn管(t2)基极、所述pnp管(t1)集电极连接,所述稳压二极管(d3)阴极与所述pnp管(t1)基极和所述npn管(t2)集电极连接。

7.进一步地,p型衬底上方设有n阱区(10)和p阱区(11),n阱区(10)内的上部设有第三n+掺杂区(02),p阱区(11)内的上部设有第二p+掺杂区(03),所述n阱区(10)作为稳压二极管(d3)的阴极,所述第三n+掺杂区(02)作为所述稳压二极管(d3)的阴极欧姆接触引出端;所述p阱区(11)作为所述稳压二极管(d3)的阳极,所述第二p+掺杂区(03)作为稳压二极

管(d3)的阳极欧姆接触引出端。

8.进一步地,通过改变第三n+掺杂区(02)与n阱区(10)端部的间距(s)调节稳压二极管(d3)的击穿电压。

9.进一步地,n阱区(10)内的上部设有第一p+掺杂区(04)和第一n+掺杂区(05),n阱区(10)作为npn管(t2)的集电极与pnp管(t1)的基极,npn管(t2)的集电极与pnp管(t1)的基极相连;第一p+掺杂区(04)作为pnp管(t1)发射极的欧姆接触引出端,第一n+掺杂区(05)作为pnp管(t1)基极的欧姆接触引出端。

10.进一步地,p阱区(11)内的上部设有第二n+掺杂区(01);p阱区(11)作为pnp管(t1)的集电极与npn管(t2)的基极,pnp管(t1)的集电极与npn管(t2)的基极相连;第二n+掺杂区(01)作为npn管(t2)发射极的欧姆接触引出端。

11.进一步地,p阱区(11)内,npn管(t2)基极至第二p+掺杂区(03)之间的等效电阻为第一电阻(rnwell)。

12.进一步地,n阱区(10)内,pnp管(t1)的基极至第一n+掺杂区(05)之间的等效电阻为第二电阻(rpwell)。

13.进一步地,p阱区(11)位于n阱区(10)左侧;第二p+掺杂区(03)位于第二n+掺杂区(01)的左侧;第三n+掺杂区(02)、第一p+掺杂区(04)、第一n+掺杂区(05)由左至右依次分布。

14.进一步地,p+掺杂区和n+掺杂区相互之间设有隔离区(fox)。

15.进一步地,隔离区(fox)为场氧工艺,由绝缘材料sio2填充。

16.本发明具有的有益效果:

17.本发明设有用于调节击穿电压的稳压二极管(d3),所述稳压二极管(d3)与所述pnp管(t1)和npn管(t2)设置于同一p型衬底上,所述稳压二极管(d3)阳极与所述npn管(t2)基极、所述pnp管(t1)集电极连接,所述稳压二极管(d3)阴极与所述pnp管(t1)基极和所述npn管(t2)集电极连接。本发明通过设置稳压二极管(d3),能够起到调节scr击穿电压的作用,有效提高scr在不同工艺应用中的普适性。

18.本发明通过改变第三n+掺杂区(02)与n阱区(10)端部的间距(s)调节稳压二极管(d3)的击穿电压,可以在同一工艺中实现具有不同击穿电压的scr,有效提升scr型esd保护结构在不同环境下的适用性。

19.本发明n阱区(10)内的上部设有第一p+掺杂区(04)和第一n+掺杂区(05),n阱区(10)作为npn管(t2)的集电极与pnp管(t1)的基极,npn管(t2)的集电极与pnp管(t1)的基极相连;第一p+掺杂区(04)作为pnp管(t1)发射极的欧姆接触引出端,第一n+掺杂区(05)作为pnp管(t1)基极的欧姆接触引出端;p阱区(11)内的上部设有第二n+掺杂区(01);p阱区(11)作为pnp管(t1)的集电极与npn管(t2)的基极,pnp管(t1)的集电极与npn管(t2)的基极相连;第二n+掺杂区(01)作为npn管(t2)发射极的欧姆接触引出端;p阱区(11)内,npn管(t2)基极至第二p+掺杂区(03)之间的等效电阻为第一电阻(rnwell);n阱区(10)内,pnp管(t1)的基极至第一n+掺杂区(05)之间的等效电阻为第二电阻(rpwell);p阱区(11)位于n阱区(10)左侧;第二p+掺杂区(03)位于第二n+掺杂区(01)的左侧;第三n+掺杂区(02)、第一p+掺杂区(04)、第一n+掺杂区(05)由左至右依次分布。本发明采用上述esd保护结构的合理有效布置,进一步保证提升scr型esd保护结构在不同环境下的适用性。

附图说明

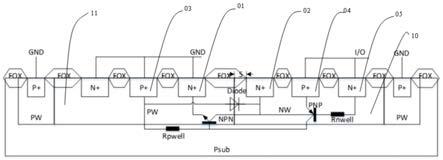

20.图1是现有scr型esd保护结构的结构示意图;

21.图2是现有scr型esd保护结构的电路原理图;

22.图3是现有scr型esd保护结构的电流-电压关系图;

23.图4是本发明scr型esd保护结构的结构示意图;

24.图5是本发明scr型esd保护结构的电路原理图;

25.图6是本发明scr型esd保护结构的两级并联结构示意图;

26.图7是本发明scr型esd保护结构的电流-电压关系图。

具体实施方式

27.下面结合附图所示的实施方式对本发明进行详细说明,但应当说明的是,这些实施方式并非对本发明的限制,本领域普通技术人员根据这些实施方式所作的功能、方法、或者结构上的等效变换或替代,均属于本发明的保护范围之内。

28.如图4、图5所示,本发明击穿电压可调节的scr型esd保护结构包括设置于同一p型衬底上的pnp管t1和npn管t2,所述pnp管t1基极接所述npn管t2集电极,所述pnp管t1集电极接所述npn管t2基极,所述pnp管t1发射极接电源阳极,所述pnp管t1基极和所述npn管t2集电极经第一电阻rnwell接电源阳极(anode),所述npn管t2发射极接电源阳极,所述npn管t2基极和所述pnp管t1集电极经第二电阻rpwell接电源阴极(cathode),还包括用于调节击穿电压的稳压二极管(diode管)d3,所述稳压二极管d3与所述pnp管t1和npn管t2设置于同一p型衬底上,所述稳压二极管d3阳极与所述npn管t2基极、所述pnp管t1集电极连接,所述稳压二极管d3阴极与所述pnp管t1基极和所述npn管t2集电极连接。

29.p型衬底psub上方设有n阱区10(nw)和p阱区11(pw),n阱区10内的上部设有第三n+掺杂区02,p阱区11内的上部设有第二p+掺杂区03,所述n阱区10作为稳压二极管d3的阴极,所述第三n+掺杂区02作为所述稳压二极管d3的阴极欧姆接触引出端;所述p阱区11作为所述稳压二极管d3的阳极,所述第二p+掺杂区03作为稳压二极管d3的阳极欧姆接触引出端。通过改变第三n+掺杂区02与n阱区10端部的间距s调节稳压二极管d3的击穿电压。

30.n阱区10内的上部设有第一p+掺杂区04和第一n+掺杂区05,n阱区10作为npn管t2的集电极与pnp管t1的基极,npn管t2的集电极与pnp管t1的基极相连;第一p+掺杂区04作为pnp管t1发射极的欧姆接触引出端,第一n+掺杂区05作为pnp管t1基极的欧姆接触引出端。

31.p阱区11内的上部设有第二n+掺杂区01;p阱区11作为pnp管t1的集电极与npn管t2的基极,pnp管t1的集电极与npn管t2的基极相连;第二n+掺杂区01作为npn管t2发射极的欧姆接触引出端。p阱区11内,npn管t2基极至第二p+掺杂区03之间的等效电阻为第一电阻rnwell。n阱区(10)内,pnp管t1的基极至第一n+掺杂区05之间的等效电阻为第二电阻rpwell。p阱区11位于n阱区10左侧;第二p+掺杂区03位于第二n+掺杂区01的左侧;第三n+掺杂区02、第一p+掺杂区04、第一n+掺杂区05由左至右依次分布。p+掺杂区和n+掺杂区相互之间设有隔离区fox。隔离区fox为场氧工艺,由绝缘材料sio2填充。

32.当esd应力发生在阴极时,稳压二极管(diode管)d3所在pw/nw_n+结发生雪崩击穿,雪崩击穿产生的大量载流子流经第一电阻rnwell、第二电阻rpwell到scr的阳极;此时第一电阻rnwell上的压降达到0.7v左右后pnp管t1发射结开始正向偏置,pnp管t1导通;电

流流经第二电阻rpwell,当电流达到触发电流itrig时,该电阻上的偏置电压达到0.7v时,使得npn管t2的发射结也正向偏置,这样npn管t2也导通。这时scr本身路径导通,开始有效的泄放esd电流,使scr结构保持启动的电压称为触发电压vtrig。

33.本发明提出了esd应力下稳压二极管先于npn管集电结击穿,为esd电流提供早期通路,待触发电流流经第一电阻rnwell、第二电阻rpwell使npn管与pnp管都导通后scr结构将作为esd电流泄放通路;而稳压二极管(diode管)d3击穿电压可以通过调节第三n+掺杂区02与n阱区10端部的间距s实现,大大提高了scr结构的适用范围。

34.本发明提出了scr结构的击穿电压breakdown的调节机制,通过改变第三n+掺杂区02与n阱区10端部的间距s来调整击穿电压,进一步改变其触发电压,vtrig=bv

diode

+itrig*rpwell,其中bv

diode

为稳压二极管(diode管)d3的击穿电压,其大小由n阱区10与第三n+掺杂区02间距s来调节。

35.本发明结构并不局限于单个使用,可以根据实际使用时对esd能力的要求两个并联使用或者多个并联使用,保留最优性能基础上可以最大程度的减小面积。如图6所示,本发明scr型esd保护结构采用两级并联结构。

36.如图7所示,bv

diode

为稳压二极管(diode管)击穿电压;触发电压vtrig=bv

diode

+itrig*(rpwell),管击穿电压bv

diode

由n阱区10与第三n+掺杂区02间距s来调节,可根据实际使用环境灵活调整s得到合适的击穿电压,提高scr结构的使用普遍性。

37.上文所列出的一系列的详细说明仅仅是针对本发明的可行性实施方式的具体说明,它们并非用以限制本发明的保护范围,凡未脱离本发明技艺精神所作的等效实施方式或变更均应包含在本发明的保护范围之内。

38.对于本领域技术人员而言,显然本发明不限于上述实施例的细节,而且在不背离本发明的精神或基本特征的情况下,能够以其他的具体形式实现本发明。因此,无论从哪一点来看,均应将实施例看作是示范性的,而且是非限制性的,本发明的范围由所附权利要求而不是上述说明限定,因此旨在将落在权利要求的等同要件的含义和范围内的所有变化囊括在本发明内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1