减少源漏极短路的方法及静态随机存储器与流程

1.本发明涉及集成电路技术领域,具体为一种减少源漏极短路的方法及使用该方法制备的静态随机存储器。

背景技术:

2.随着半导体技术不断发展,集成电路单位面积内半导体器件密度不断增大,半导体器件物理尺寸不断缩小,但随之产生的相邻半导体之间产生短路的风险增加。例如,在集成电路中制备相邻分布的晶体管,受加工工艺限制,相邻晶体管源漏极之间极易因距离较近而产生桥连,桥连易导致相邻mos管的源漏极产生短路。目前常用的减少源漏极短路的方式是缩小mos管主动区(active area)尺寸以留出充足空间或改善外延生长工艺,但随着半导体器件物理尺寸的不断缩小,主动区域尺寸缩小工艺或外延生长工艺已接近技术极限,如何通过加工工艺的进一步改善,来减少相邻mos管源漏极之间短路,成为本领域人员亟待解决的问题。

技术实现要素:

3.针对现有技术中存在的上述问题,本发明提供了一种减少源漏极短路的方法,其可降低相邻晶体管源漏极之间产生桥连而短路的风险,可提高单位面积内半导体器件密度。

4.为实现上述目的,本发明采用如下技术方案:

5.一种减少源漏极短路的方法,该方法包括以下步骤:s1、提供衬底,所述衬底上分布有间隔设置的第一沟槽隔离区,所述衬底及所述第一沟槽隔离区的顶端沉积有自下而上依次分布的体硅层、opl层、抗反射层、光刻胶层;

6.s2、采用光刻工艺对所述opl层的中部刻蚀,获得刻蚀槽;

7.s3、将所述光刻胶层去除,使所述抗反射层的顶端露出;

8.s4、在所述刻蚀槽的内表面及所述抗反射层的顶端沉积第一蚀刻层;

9.s5、在所述第一刻蚀层的顶端沉积第二蚀刻层;

10.s6、采用光刻工艺对所述第一刻蚀层、第二刻蚀层进行刻蚀,将所述opl层上方的所述第一刻蚀层、第二刻蚀层去除,同时将所述刻蚀槽内部的部分第一刻蚀层、第二刻蚀层去除,获取隔离层,所述隔离层的宽度等于相邻两个晶体管源漏极之间的最小间距;

11.s7、去除所述隔离层两侧的opl层;

12.s8、使所述隔离层两侧的所述体硅层生长出源漏极。

13.其进一步特征在于,

14.所述光刻胶层包括相邻布置的第一光刻胶层、第二光刻胶层,所述第一光刻胶层与所述第二光刻胶层之间设置有间隙,所述间隙的宽度与集成电路中相邻两个晶体管源漏极之间的最小间距相等;

15.所述刻蚀槽的宽度等于所述间隙的宽度,所述间隙的宽度与所述刻蚀槽的宽度均

为30nm~46.3nm;

16.所述第一蚀刻层的材质为sin,厚度为

17.所述第二刻蚀层的材质为sio2,厚度为

18.所述隔离层包括所述第一刻蚀层、第二刻蚀层,所述隔离层的厚度为

19.所述源漏极的材质为锗硅(sige)。

20.一种静态随机存储器,所述静态随机存储器包括至少两个相邻分布的晶体管,所述晶体管均包括源漏极,其特征在于,相邻两个所述晶体管的源漏极之间设置有所述隔离层,所述隔离层采用上述减少源漏极短路的方法制备获得。

21.其进一步特征在于,

22.相邻两个所述源漏极之间的最小宽度为30.3nm,最大宽度为46.3nm;

23.所述晶体管为平面晶体管或鳍形场效应晶体管。

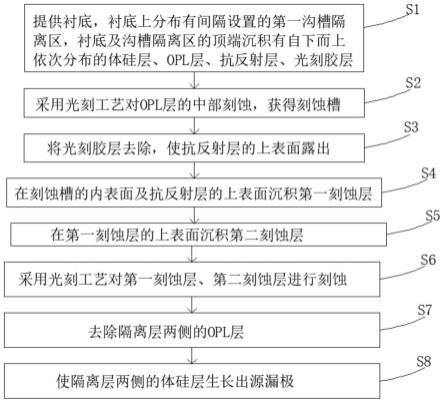

24.采用本发明上述方法可以达到如下有益效果:该减少源漏极短路的相邻晶体管源漏极制备方法中,在生长源漏极前先制备了隔离层,在隔离层的两侧生长出源漏极,由于隔离层阻隔于相邻晶体管源漏极之间,能够有效避免源漏极生长过程中产生桥连,从而降低了相邻晶体管源漏极之间的短路风险。

附图说明

25.图1为显微镜下现有的相邻两个晶体管源漏极的实物放大图;

26.图2为现有的集成电路中相邻两个晶体管的分布结构;

27.图3为本发明减少源漏极短路的方法流程图;

28.图4为本发明减少源漏极短路的方法步骤s1中第一沟槽隔离区、体硅层、opl层、抗反射层、光刻胶层分布的主视结构示意图;

29.图5为本发明减少源漏极短路的方法步骤s3中光刻胶层去除后的主视结构示意图;

30.图6为本发明减少源漏极短路的方法步骤s4中沉积第一刻蚀层后的主视结构示意图;

31.图7为本发明减少源漏极短路的方法步骤s5中沉积第二刻蚀层后的主视结构示意图;

32.图8为本发明减少源漏极短路的方法步骤s6中去除部分第一刻蚀层、第二刻蚀层后的主视结构示意图;

33.图9为本发明减少源漏极短路的方法步骤s7中去除opl层后的主视结构示意图;

34.图10为本发明减少源漏极短路的方法步骤s8中生长源漏极后的主视结构示意图。

具体实施方式

35.为了使本技术领域的人员更好地理解本发明方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分的实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人

员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本发明保护的范围。

36.需要说明的是,本发明的说明书和权利要求书及上述附图中的术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、装置、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

37.图1、图2提供了现有集成电路中相邻两个晶体管的分布结构,从图1可以看出,相邻两个晶体管源漏极之间的间距最小为30.3nm,最大为46.3nm,受加工工艺限制,生长出的相邻晶体管源漏极之间极易产生桥连而短路,相邻晶体管源漏极之间距离越近,产生短路的风险越大,使得集成电路单位面积内半导体器件密度增大受到限制。目前常用的用于减少相邻晶体管源漏极短路的方式为主动区域尺寸缩小工艺或外延生长工艺等,但这两种方式的工艺制程较为复杂,且已接近技术极限。

38.针对现有技术中存在的如何通过加工工艺进一步改善来减少集成电路中相邻晶体管源漏极短路的问题,以下提供了一种减少源漏极短路的方法的具体实施例,该方法包括以下步骤:s1、提供衬底1(pr),衬底1上分布有间隔设置的第一沟槽隔离区2(sti),衬底1及第一沟槽隔离区2的顶端沉积有自下而上依次分布的体硅层3、opl层4、抗反射层5、光刻胶层,参考图4,光刻胶层包括相邻布置的第一光刻胶层61、第二光刻胶层62,第一光刻胶层61与第二光刻胶层62之间设置有间隙7,间隙7的宽度与集成电路中相邻两个晶体管源漏极10之间的最小间距相等。

39.s2、采用光刻工艺对opl层4的中部刻蚀,获得刻蚀槽8。抗反射层5、光刻胶层61/62构成掩膜版,采用光刻工艺对opl层4进行刻蚀时,光线穿过第一光刻胶层61、第二光刻胶层62之间的间隙7对其下方的抗反射层5、opl层4进行刻蚀,获得的刻蚀槽8的宽度等于间隙7的宽度,间隙7的宽度与刻蚀槽8的宽度均为30nm~46.3nm,本实施例中优选39nm。该间距根据相邻两个晶体管源漏极10之间的最小间距灵活设定。

40.s3、将该衬底放置于去胶机中进行去胶处理,将第一光刻胶层61、第二光刻胶层62清除,使剩余抗反射层5的上表面露出,参考图5。

41.s4、采用原子层沉积方式在刻蚀槽8的内表面及抗反射层5的上表面沉积第一蚀刻层91,参考图6,第一蚀刻层91的材质为sin,厚度为

42.s5、采用原子层沉积方式在第一刻蚀层91的上表面沉积第二蚀刻层92,参考图7,第二刻蚀层的材质为sio2,厚度为

43.s6、采用光刻工艺对第一刻蚀层91、第二刻蚀层92进行刻蚀,将opl层4上方的第一刻蚀层91、第二刻蚀层92去除,同时将刻蚀槽8内部的部分第一刻蚀层91、第二刻蚀层92去除,获取隔离层11,隔离层11的宽度等于相邻两个晶体管源漏极10之间的最小间距;隔离层11包括第一刻蚀层、第二刻蚀层,本实施例中,隔离层11的厚度为b,厚度b的范围为:30.3nm~46.3nm,该厚度根据相邻两侧的晶体管源漏极的位置设定。再采用湿法清洗方式对剩余抗反射层5进行清洗刻蚀,将抗反射层5清除,参考图8。湿法清洗的清洗液为质量浓度为98%的硫酸和质量浓度为30%的双氧水,硫酸与双氧水的质量比例为5:1,采用湿法清洗进行清洗时的清洗温度为125℃,该清洗液具有强酸性,在强酸溶液腐蚀作用下将抗反射层5

去除。

44.s7、采用干法刻蚀方式将隔离层11两侧的opl层4去除,参考图9;opl层为无定形碳硬掩模层,是一种碳氢化合物,主要成分为碳,掺杂少量的氢;

45.s8、采用外延生长工艺使隔离层11两侧的体硅层3生长出源漏极10;源漏极10的材质为锗硅(sige),参考图10。

46.上述源漏极短路方法为一种集成电路中相邻晶体管源漏极的制备方法,该方法中,隔离层的设置增大了晶体管(该晶体管为pmos管但不限于pmos管)源漏极生长时的外延生长(epi)工艺窗口,因此,在上述步骤s8源漏极外延生长时,通过隔离层将源漏极分隔,相比于图1所示的源漏极结构,有效降低了源漏极桥连而短路的风险。

47.将上述方法应用于集成电路制作中,该集成电路为包含有若干晶体管的静态随机存储器,静态随机存储器包括至少两个相邻分布的晶体管,晶体管为平面晶体管(planner)或鳍形场效应晶体管(finfet),晶体管均包括源漏极11,相邻两个源漏极11之间的最小宽度为30.3nm,最大宽度为46.3nm。该静态随机存储器中相邻两个晶体管的源漏极之间设置有隔离层11,隔离层11采用上述减少源漏极短路的方法制备获得。

48.隔离层11的宽度等于相邻两个晶体管源漏极之间的最小间距,因此,在集成电路(集成电路包括静态随机存储器)中制作晶体管源漏极时,可以根据需要获得的相邻晶体管源漏极之间的最小间距来确定隔离层的宽度,本实施例中,晶体管源漏极之间的最小间距为30.3nm,在晶体管主动区域尺寸与目前常用晶体管主动区域(主动区域主要指晶体管的源漏极)尺寸相同的条件下,即使相邻两个晶体管源漏极之间的间距根据实际需求缩小,由于受隔离层阻隔,相邻两个晶体管源漏极也不会产生桥连,并且该间距的缩小使得半导体器件之间的物理尺寸缩小,从而使集成电路单位面积内半导体器件密度增大,提高了集成电路的集成度。

49.以上的仅是本技术的优选实施方式,本发明不限于以上实施例。可以理解,本领域技术人员在不脱离本发明的精神和构思的前提下直接导出或联想到的其他改进和变化,均应认为包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1