多路控制复合功能器件

1.本发明属于微电子技术领域,特别涉及一种复合功能器件,可用作电力电子系统的基本单元。

技术背景

2.随着宽禁带半导体材料的发展,传统硅基功率晶体管其性能已趋近理论极限,很难满足下一代高性能电力电子系统对高温、高压、高频、高效和高功率密度的迫切要求。而基于p型帽层gan基异质结结构的增强型高电子迁移率晶体管,即氮化镓基功率晶体管,可实现更低导通电阻、更快开关速度、更高功率密度等优异特性,有助于大大提升电力电子系统的性能和可靠性,显著减小功耗。因此,大力研发高性能、高可靠性氮化镓基功率器件,对我国实现节能减排和绿色发展发挥着举足轻重的作用。

3.传统氮化镓基功率晶体管是基于gan基异质结结构,其包括:衬底1、过渡层2、沟道层3、势垒层4、p-gan栅5、漏极6、源极7、栅金属8;势垒层4上部左侧淀积有漏极6,势垒层4上部右侧淀积有源极7,势垒层4上部中间部分淀积有p-gan栅5,p-gan栅5上部淀积有栅金属8,如图1所示。这种传统氮化镓基功率晶体管由于受到材料外延技术与器件制造工艺水平的限制,晶体管表面和体内会产生大量的缺陷,这些缺陷的存在会俘获电荷,从而导致严重的电流崩塌问题,进一步衰减器件的可靠性和功率特性,且该结构只允许漏极电位高于源极,只能实现单向阻断,参见effects of hole traps on the temperature dependence of current collapse in a normally-off gate-injection transistor,japanese journal of applied physics,55(5),2016。在当前许多功率管理系统的技术领域中,往往需要功率开关器件具有很强的反向阻断能力,由于传统gan基hemt功率开关器件的漏极为欧姆接触,因而不能施加反向电压。因此,迫切需要研发具有优异反向阻断能力的功能器件。

技术实现要素:

4.本发明的目的在于针对上述现有技术的不足,提供一种多路控制复合功能器件,以实现双向阻断特性,提升器件的可靠性,并大大缩减占用面积,提升芯片面积利用率和集成度。

5.为实现上述目的,本发明的技术方案是这样实现的:

6.一、器件结构

7.一种多路控制复合功能器件,自下而上包括:衬底1、过渡层2、沟道层3和势垒层4,其特征在于:

8.所述沟道层3和势垒层4内部设有隔离深槽5,该隔离深槽5由m个大小相同且前、后分布的深槽构成,相邻两个深槽之间的距离相等,m>1;

9.所述隔离深槽5将沟道层3和势垒层4分成m+1个条状结构,在每个条状结构上,从左至右依次设置有左电极10、左p型块6、左凹槽13、节点12,右p型块7、右凹槽14、右电极11;

10.所述左p型块6与右p型块7均位于势垒层4上部,其上侧分别设有左介质块8与右介质块9;

11.所述左凹槽13与右凹槽14均由n个矩形槽构成,这n个矩形槽为等间距平行排列,其下侧均位于沟道层3中;

12.所述左凹槽13中设有第一电极15,右凹槽14中设有第二电极16,该第一电极与第二电极均由n个大小相同的t型金属块构成,这些t型金属块的垂直部分下侧均位于沟道层3内部,水平部分的下侧位于势垒层4上表面,n>1;

13.所述左介质块8与右介质块9上部分别设有左栅极17与右栅极18。

14.进一步,所述势垒层4的al组分为0.1~0.4,其厚度a为1nm~40nm。

15.进一步,所述左p型块6与右p型块7采用p-gan或cuo或nio材料,其厚度为5nm~500nm,掺杂浓度均为5

×

10

15

cm-3

~1

×

10

22

cm-3

。

16.进一步,所述左介质块8与右介质块9采用al2o3或hfo2或si3n4,其厚度为5nm~100nm。

17.进一步,所述每个条状结构上的左凹槽13与右凹槽14中的n个矩形槽的深度均为h,h》a,其中a为势垒层4的厚度。

18.进一步,在每个条状结构上,第一电极15与第二电极16各自包含的n个t型金属块中,第一个t型金属块与第二个t型金属块之间的距离为t1,第二个t型金属块与第三个t型金属块之间的距离为t2,

…

,第(n-1)个t型金属块与第n个t型金属块之间的距离为t

n-1

,且满足t1=t2=

…

=t

n-1

,每个t型金属块的垂直部分下侧与势垒层上表面之间的距离均为h;

19.进一步,每个第一电极15中的t型金属块的水平部分左端与左p型块6右端之间的距离为x1,水平部分右端与节点12之间的距离为u1;每个第二电极16中的t型金属块的水平部分左端与右p型块7右端之间的距离为x2,水平部分右端与右电极11之间的距离为u2;且满足x1=x2=x,u1=u2=u,其中x远小于u,u》1μm。

20.进一步,所述左栅极17、右栅极18均小于其所对应的左介质块8、右介质块9的长度。

21.进一步,所述左电极10、右电极11和节点12均与势垒层4为欧姆接触;第一电极15分别与势垒层4和沟道层3之间形成肖特基接触;第二电极16分别与势垒层4和沟道层3之间形成肖特基接触。

22.二、制作方法

23.一种制作本发明多路控制复合功能器件的方法,其特征在于,包括如下步骤:

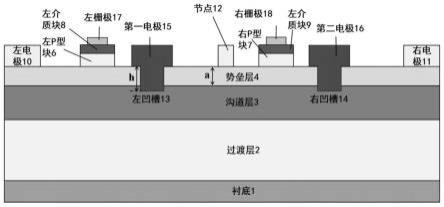

24.a)在衬底1上外延gan基宽禁带半导体材料,形成过渡层2;

25.b)在过渡层2上外延gan材料,形成沟道层3;

26.c)在沟道层3上外延gan基宽禁带半导体材料,形成厚度为a的势垒层4;

27.d)在势垒层4上外延p型半导体材料,形成厚度为5~500nm、掺杂浓度为5

×

10

15

~1

×

10

22

cm-3

的p型层;

28.e)在p型层上外延介质材料,形成厚度为5nm~100nm的介质层;

29.f)在该介质层上第一次制作掩膜,利用该掩膜对介质层、p型层、势垒层4、沟道层3依次进行刻蚀,刻蚀至沟道层3内部为止,形成m个大小相同且等间距平行排列的深槽,这m个深槽共同组成了隔离深槽5;这m个深槽将沟道层3和势垒层4分成m+1个条状结构;

30.g)刻蚀形成左p型块6、右p型块7、左介质块8与右介质块9:

31.g1)在刻蚀后的介质层、p型层、沟道层3、势垒层4与隔离深槽5上第二次制作掩膜,利用该掩膜对刻蚀后的介质层再次进行刻蚀,刻蚀至p型层的上表面为止,形成左介质块8与右介质块9;

32.g2)再次利用该掩膜,对p型层进行刻蚀,刻蚀至势垒层4的上表面为止,形成左p型块6与右p型块7;

33.h)在沟道层3、势垒层4、隔离深槽5、左介质块8与右介质块9上第三次制作掩膜,利用该掩膜在势垒层4上部的左、右两侧以及中部分别淀积多层金属,并在n2气氛中进行快速热退火,形成左电极10、右电极11与节点12;

34.i)制作第一电极15与第二电极16:

35.i1)在沟道层3、势垒层4、隔离深槽5、左介质块8、右介质块9、左电极10、右电极11与节点12上第四次制作掩膜,利用该掩膜对左p型块6右侧与右p型块7右侧的势垒层4与沟道层3依次进行刻蚀,刻蚀总深度为h,在每个左p型块6右侧与每个右p型块7右侧均形成n个大小相同的矩形槽,n个矩形槽中相邻两个矩形槽之间的距离分别为t1、t2、

…

、t

n-1

,且t1=t2=

…

=t

n-1

;每个左p型块6右侧n个矩形槽构成左凹槽13,每个右p型块7右侧n个矩形槽构成右凹槽14;

36.i2)在沟道层3、势垒层4、隔离深槽5、左介质块8、右介质块9、左电极10、右电极11、节点12、左凹槽13与右凹槽14上第五次制作掩模,利用该掩膜在每个左凹槽13内部、左凹槽13两侧的势垒层4上部淀积金属,形成第一电极15;在每个右凹槽14内部、右凹槽14两侧的势垒层4上部淀积金属,形成第二电极16;

37.j)在沟道层3、势垒层4、隔离深槽5、左介质块8、右介质块9、左电极10、右电极11、节点12、第一电极15与第二电极16上第六次制作掩膜,利用该掩膜在左介质块8与右介质块9上部淀积金属,分别形成左栅极17与右栅极18,完成整个器件的制作。

38.本发明器件与传统氮化镓基功率晶体管比较,具有以下优点:

39.第一,能提供双向阻断,器件可靠性强。

40.本发明器件中由于设置有第一电极与第二电极,组成这些电极的t型金属块连接至势垒层与沟道层之间所形成的二维电子气。在器件导通工作时,左电极电位高于节点电位,电子首先通过第一电极中每个t型金属块之间的间隙进行导电,当t型金属块电位升高后,也将参与导电;右电极与第二电极导电过程与该过程类似,这个过程与传统的导电过程相比,对电流影响不大;在器件阻断工作时,左、右栅极不施加电压,即零电位,分为两种情况:第一,在左电极电位高于节点电位情况下,此时由于器件处于关态,二维电子气不能达到导通所需要的面密度,无法进行导通,实现正向阻断;第二,在左电极电位低于节点电位情况下,第一电极中每个t型金属块与节点之间形成的肖特基二极管反偏,t型金属块附近的二维电子气被进一步耗尽,实现反向阻断;右电极与第二电极阻断过程与该过程类似;因此,器件可实现双向阻断,可靠性强。

41.第二,节省面积,提高芯片面积利用率和集成度。

42.本发明器件中有严格的平移重复关系,虽然结构略显复杂,但多个部分均可同步制作,例如:左电极、右电极与节点,左p型块与右p型块,左介质块与右介质块,第一电极与第二电极等等,因此本发明器件工艺步骤并不会增加;在本发明结构中,隔离深槽将器件分

成了(m+1)个条状结构,每个条状结构上的节点代替传统的导线互连实现左、右部分的连接;左、右电极将所有条状结构连接起来以实现多路控制。每个节点都是分立的,用于根据实际需求连接负载。因此,可以在确保器件具有良好可靠性和输出功率特性的基础上,通过器件层面的共用实现连接,避免了传统的pcb板级互联,大大提高了芯片面积利用率和集成度,显著减小了寄生参数。

附图说明

43.图1是传统氮化镓基功率晶体管的结构图;

44.图2是本发明多路控制复合功能器件结构图;

45.图3是图2的俯视图;

46.图4是图3条状结构上节点左侧一个单元的结构图;

47.图5是本发明制备图2器件的实现流程图;

48.图6是对本发明器件测试所得的阻断特性图。

具体实施方式

49.以下结合附图对本发明的实施例和效果作进一步详细描述。

50.参照图2、图3和图4,本实例给出的多路控制复合功能器件包括:衬底1、过渡层2、沟道层3、势垒层4、隔离深槽5、左p型块6、右p型块7、左介质块8、右介质块9、左电极10、右电极11、节点12、左凹槽13、右凹槽14、第一电极15、第二电极16、左栅极17、右栅极18。其中:

51.所述衬底1采用蓝宝石或碳化硅或硅或其他材料;

52.所述过渡层2位于衬底1的上部,其由gan基宽禁带半导体材料组成;

53.所述沟道层3位于过渡层2的上部,其由gan材料构成;

54.所述势垒层4位于沟道层3的上部,其由若干层相同或不同的gan基宽禁带半导体材料组成,其al组分为0.1~0.4,厚度a为1nm~40nm;

55.所述隔离深槽5位于沟道层3和势垒层4内部,其由m个大小相同且前、后分布的深槽构成,相邻两个深槽之间的距离相等,m>1,该隔离深槽5将沟道层3和势垒层4分成m+1个条状结构;

56.所述左p型块6、右p型块7位于势垒层4的上部,采用p-gan或cuo或nio或其他材料,其厚度为5nm~500nm,掺杂浓度均为5

×

10

15

cm-3

~1

×

10

22

cm-3

;

57.所述左介质块8、右介质块9分别位于左p型块6、右p型块7的上部,采用al2o3或hfo2或si3n4或其他介质材料,其厚度为5nm~100nm;

58.所述左电极10、右电极11分别位于势垒层4上部的左、右两侧,均与势垒层4为欧姆接触;

59.所述节点12位于每个条状结构上的中部位置,其采用多层金属,与势垒层4为欧姆接触;

60.所述左凹槽13位于每个条状结构上左p型块6右侧的势垒层4和沟道层3内,右凹槽14位于每个条状结构上右p型块7右侧的势垒层4和沟道层3内;每个条状结构上的左凹槽13与右凹槽14均由n个矩形槽构成,这n个矩形槽为等间距平行排列,每个矩形槽的深度均为h,h》a,其中a为势垒层4的厚度,n>1;

61.所述第一电极15位于左凹槽13内部与势垒层4上部,第二电极16位于右凹槽14内部与势垒层4上部;在每个条状结构上,第一电极15与第二电极16均由n个大小相同且等间距平行排列的t型金属块构成,这些t型金属块的垂直部分下侧均位于沟道层3内部,水平部分的下侧位于势垒层4上表面;这n个t型金属块中,第一个t型金属块与第二个t型金属块之间的距离为t1,第二个t型金属块与第三个t型金属块之间的距离为t2,

…

,第(n-1)个t型金属块与第n个t型金属块之间的距离为t

n-1

,且满足t1=t2=

…

=t

n-1

;每个第一电极15中的t型金属块的水平部分左端与左p型块6右端之间的距离为x1,与节点12之间的距离为u1;每个第二电极16中的t型金属块的水平部分左端与右p型块7右端之间的距离为x2,与右电极11之间的的距离为u2,且满足x1=x2=x,u1=u2=u,其中x远小于u,u》1μm;

62.所述左栅极17与右栅极18分别位于左介质块8与右介质块9的上部,其长度均小于对应的介质块的长度。

63.参照图5,本发明制备的多路控制复合功能器件给出如下三种实施例。

64.实施例一:在碳化硅衬底上制作m=5,势垒层4厚度a为22nm、al组分为0.3,左p型块6与右p型块7材料为p型cuo,掺杂浓度均为3

×

10

20

cm-3

、厚度均为230nm,介质块选用si3n4,厚度为45nm,第一电极15与第二电极16所对应的t型金属块数目为三个的多路控制复合功能器件。

65.步骤a.在碳化硅衬底1上外延aln材料制作过渡层2。

66.设置温度为1050℃,压强为45torr,氢气流量为4500sccm,氨气流量为4500sccm,铝源流量为7μmol/min的工艺条件,使用金属有机物化学气相淀积技术在碳化硅衬底1上外延厚度为70nm的aln材料,形成过渡层2。

67.步骤b.在过渡层2上外延gan材料,形成沟道层3。

68.设置温度为1020℃,压强为48torr,氢气流量为4800sccm,氨气流量为4800sccm,镓源流量为100μmol/min的工艺条件,使用金属有机物化学气相淀积技术在过渡层2上外延厚度为9.93μm的gan材料,形成沟道层3。

69.步骤c.在沟道层3上淀积al

0.3

ga

0.7

n制作势垒层4。

70.设置温度为980℃,压强为46torr,氢气流量为4500sccm,氨气流量为4500sccm,镓源流量为36μmol/min,铝源流量为7μmol/min的工艺条件,使用金属有机物化学气相淀积技术在沟道层3上淀积厚度为22nm,且铝组分为0.3的al

0.3

ga

0.7

n势垒层4。

71.步骤d.在势垒层4上制作p型层。

72.选用纯度为99.999%的铜作为靶材,溅射气体为高纯氩气,同样纯度的高纯氧气作为反应气体,设置溅射前反应室真空度为2.0

×

10-4

pa,溅射中保持氩气流速为20sccm,氧气流速为10sccm,沉积室的气压为0.5pa,射频功率为35w,基底温度为200℃的工艺条件,使用磁控溅射技术在势垒层4上外延厚度为230nm、掺杂浓度为3

×

10

20

cm-3

的cuo,形成p型层。

73.步骤e.在p型层上外延介质材料si3n4。

74.设置nh3流量为2.5sccm,n2流量为950sccm,sih4流量为250sccm,温度为300℃,rf功率为50w和压力为950mt的工艺条件,在p型cuo层上,使用等离子体增强化学气相淀积技术,淀积厚度为45nm的si3n4材料,形成介质层。

75.步骤f.刻蚀形成隔离深槽5。

76.设置刻蚀介质si3n4采用的工艺条件为:cf4流量为45sccm,o2流量为5sccm,压强为

15mt,功率为250w;

77.设置刻蚀其他层半导体材料采用的工艺条件为:cl2流量为18sccm,压强为14mtorr,功率为120w;

78.在该si3n4介质层上第一次制作掩膜,利用该掩膜使用反应离子刻蚀技术,对介质层、p型层、势垒层4、沟道层3依次进行刻蚀,刻蚀至沟道层3内部,刻蚀总深度为370nm,形成五个深槽,这五个深槽构成了隔离深槽5;该隔离深槽5将沟道层3和势垒层4分成了六个条状结构。

79.步骤g.刻蚀形成左p型块6、右p型块7、左介质块8与右介质块9。

80.g1)设置cf4流量为45sccm,o2流量为5sccm,压强为15mt,功率为250w的刻蚀工艺条件,在步骤f中刻蚀后的si3n4介质层、p型层、沟道层3、势垒层4与隔离深槽5上第二次制作掩膜,利用该掩膜使用反应离子刻蚀技术,对刻蚀后的介质层再次进行刻蚀,刻蚀至p型层的上表面为止,形成左介质块8与右介质块9;

81.g2)设置cl2流量为18sccm,压强为13mtorr,功率为130w的工艺条件,再次利用第二次制作的掩膜,使用反应离子刻蚀技术对p型层进行刻蚀,刻蚀至势垒层4的上表面为止,形成左p型块6与右p型块7。

82.步骤h.在势垒层4上制作左电极10、右电极11与节点12。

83.设置真空度小于1.8

×

10-3

pa,功率为400w,蒸发速率小于的工艺条件,在沟道层3、势垒层4、隔离深槽5、左介质块8与右介质块9上第三次制作掩膜,利用该掩膜使用电子束蒸发技术,在势垒层4上部的左、右两侧以及中部分别淀积多层金属,金属组合自下而上分别为ti/al/mo/au,其厚度分别为0.015μm/0.132μm/0.048μm/0.056μm,并在温度为870℃的n2气氛中进行快速热退火35s,从左至右依次形成左电极10、节点12与右电极11。

84.步骤i.制作第一电极15与第二电极16。

85.i1)设置cl2流量为18sccm,压强为15mtorr,功率为110w的工艺条件,在沟道层3、势垒层4、隔离深槽5、左介质块8、右介质块9、左电极10、右电极11与节点12上第四次制作掩膜,利用该掩膜使用反应离子刻蚀,对每个条状结构上的左p型块6右侧与右p型块7右侧的势垒层4与沟道层3均依次进行刻蚀,刻蚀总深度h为105nm,在每个左p型块6右侧与每个右p型块7右侧均形成三个大小相同且等间距排列的矩形槽;每个左p型块6右侧的三个矩形槽构成左凹槽13,每个右p型块7右侧的三个矩形槽构成右凹槽14;

86.i2)设置真空度小于1.8

×

10-3

pa,功率为520w,蒸发速率小于的工艺条件,在沟道层3、势垒层4、隔离深槽5、左介质块8、右介质块9、左电极10、右电极11、节点12、左凹槽13与右凹槽14上第五次制作掩模,利用该掩膜采用电子束蒸发技术,在每个左凹槽13内部及左凹槽13两侧的势垒层4上部、右凹槽14内部及右凹槽14两侧的势垒层4上部分别淀积金属组合ta/au,其厚度分别为0.223μm/0.137μm,分别形成三个t型金属条,依次构成第一电极15与第二电极16。

87.步骤j.在左介质块8与右介质块9上分别制作栅极17与栅极18。

88.设置溅射气压0.1pa左右,ar的流量为8sccm,基片温度固定在200℃,靶材射频功率为150w的工艺条件,在沟道层3、势垒层4、隔离深槽5、左介质块8、右介质块9、左电极10、右电极11、节点12、第一电极15与第二电极16上第六次制作掩膜,利用该掩膜在左介质块8与右介质块9上部采用溅射技术溅射厚度分别为0.025μm/0.45μm的金属组合ta/au,分别形

成左栅极17与右栅极18,完成整个器件的制作。

89.实施例二:在蓝宝石衬底上制作m=1,势垒层4厚度a为1nm、al组分为0.4,左p型块6与右p型块7材料为p型gan,掺杂浓度均为1

×

10

22

cm-3

、厚度均为5nm,介质块选用al2o3,厚度为5nm,第一电极15与第二电极16所对应的t型金属块数目为两个的多路控制复合功能器件。

90.步骤1.在蓝宝石衬底1上外延gan材料制作过渡层2。

91.使用金属有机物化学气相淀积技术在蓝宝石衬底1上外延厚度为30nm的gan材料,形成过渡层2;

92.淀积的工艺条件为:温度为500℃,压强为46torr,氢气流量为4300sccm,氨气流量为4300sccm,镓源流量为21μmol/min。

93.步骤2.在过渡层2上外延gan材料,形成沟道层3。

94.使用金属有机物化学气相淀积技术在过渡层2上外延厚度为1.94μm的gan材料,形成未掺杂的沟道层3;

95.其工艺条件为:温度为960℃,压强为48torr,氢气流量为4600sccm,氨气流量为4600sccm,镓源流量为110μmol/min。

96.步骤3.在未掺杂的沟道层3上淀积al

0.4

ga

0.6

n制作势垒层4。

97.使用金属有机物化学气相淀积技术在沟道层3上淀积厚度为1nm,且铝组分为0.4的未掺杂al

0.4

ga

0.6

n势垒层4;

98.淀积采用的工艺条件为:温度为980℃,压强为43torr,氢气流量为4200sccm,氨气流量为4200sccm,镓源流量为35μmol/min,铝源流量为7μmol/min。

99.步骤4.在势垒层4上制作p型层。

100.使用金属有机物化学气相淀积技术,在势垒层4上外延厚度为5nm、掺杂浓度为1

×

10

22

cm-3

的p型gan,形成p型gan层;

101.淀积采用的工艺条件是:温度为950℃,压强为42torr,氢气流量为4100sccm,以高纯mg源为掺杂剂,氨气流量为4100sccm,镓源流量为100μmol/min。

102.步骤5.在p型层上外延介质材料al2o3,形成介质层。

103.在p型gan层上,使用原子层淀积技术,淀积厚度为5nm的al2o3材料,形成介质层;

104.原子层淀积技术采用的工艺条件为:反应源为三甲基铝(tma)和去离子水,反应温度为300℃,反应腔气压为5托,单个反应周期包括1.5s的三甲基铝气体通入,3s的氮气吹洗,1s的去离子水蒸汽通入,3s的氮气吹洗。

105.步骤6.刻蚀形成隔离深槽5。

106.在al2o3介质层上第一次制作掩膜,利用该掩膜使用反应离子刻蚀技术,对介质层、p型层、势垒层4、沟道层3依次进行刻蚀,刻蚀至沟道层3内部,刻蚀总深度为20nm,形成一个深槽,这个深槽即为隔离深槽5;该隔离深槽5将沟道层3和势垒层4分成两个条状结构;

107.刻蚀采用的工艺条件为:cl2流量为18sccm,压强为14mtorr,功率为120w。

108.步骤7.刻蚀形成左p型块6、右p型块7、左介质块8与右介质块9。

109.7a)在刻蚀后的介质层、p型层、沟道层3、势垒层4与隔离深槽5上第二次制作掩膜,利用该掩膜使用反应离子刻蚀技术,对刻蚀后的介质层再次进行刻蚀,刻蚀至p型层的上表面为止,形成左介质块8与右介质块9;

110.刻蚀采用的工艺条件为:cl2流量为18sccm,压强为14mtorr,功率为120w;

111.7b)再次利用该掩膜,使用反应离子刻蚀技术对p型层进行刻蚀,刻蚀至势垒层4的上表面为止,形成左p型块6与右p型块7;

112.刻蚀采用的工艺条件为:cl2流量为15sccm,压强为12mtorr,功率为80w。

113.步骤8.在势垒层4上制作左电极10、右电极11与节点12。

114.在沟道层3、势垒层4、隔离深槽5、左介质块8与右介质块9上第三次制作掩膜,利用该掩膜使用电子束蒸发技术,在势垒层4上部的左、右两侧以及中部分别淀积多层金属,该金属组合自下而上分别为al、ni和au,其厚度分别为0.153μm/0.045μm/0.052μm,并在n2气氛中进行快速热退火,从左至右依次形成左电极10、节点12与右电极11;

115.电子束蒸发技术的工艺条件为:真空度小于1.8

×

10-3

pa,功率为500w,蒸发速率小于

116.快速热退火采用的工艺条件为:温度为870℃,时间为35s。

117.步骤9.制作第一电极15与第二电极16。

118.9a)在沟道层3、势垒层4、隔离深槽5、左介质块8、右介质块9、左电极10、右电极11与节点12上第四次制作掩膜,利用该掩膜使用反应离子刻蚀技术,对每个条状结构上的左p型块6右侧与右p型块7右侧的势垒层4与沟道层3均依次进行刻蚀,刻蚀总深度h为9nm,在每个左p型块6右侧与每个右p型块7右侧均形成两个大小相同的矩形槽;每个左p型块6右侧的两个矩形槽构成左凹槽13,每个右p型块7右侧的两个矩形槽构成右凹槽14;

119.反应离子刻蚀的工艺条件为:cl2流量为15sccm,压强为12mtorr,功率为95w。

120.9b)在沟道层3、势垒层4、隔离深槽5、左介质块8、右介质块9、左电极10、右电极11、节点12、左凹槽13与右凹槽14上第五次制作掩模,利用该掩膜采用电子束蒸发技术,在每个左凹槽13内部及左凹槽13两侧的势垒层4上部、右凹槽14内部及右凹槽14两侧的势垒层4上部分别淀积金属组合ni/au,其厚度分别为0.003μm/0.017μm,分别形成两个t型金属条,依次构成第一电极15与第二电极16;

121.蒸发金属采用的工艺条件为:真空度小于1.8

×

10-3

pa,功率为200w,蒸发速率小于

122.步骤10.在左介质块8与右介质块9上分别制作栅极17与栅极18。

123.在沟道层3、势垒层4、隔离深槽5、左介质块8、右介质块9、左电极10、右电极11、节点12、第一电极15与第二电极16上第六次制作掩膜,利用该掩膜在左介质块8与右介质块9上部,采用电子束蒸发技术淀积金属组合ni/au,其厚度分别为0.063μm/0.037μm,分别形成左栅极17与右栅极18,完成整个器件的制作。

124.电子束蒸发技术的工艺条件为:真空度小于1.8

×

10-3

pa,功率为500w,蒸发速率小于

125.实施例三:在硅衬底上制作m=4,势垒层4厚度a为40nm、al组分为0.1,左p型块6与右p型块7材料为p型nio,掺杂浓度均为5

×

10

15

cm-3

、厚度均为500nm,介质块选用hfo2,厚度为100nm,第一电极15与第二电极16所对应的t型金属块数目为六个的多路控制复合功能器件。

126.第一步.在硅衬底1上外延aln材料制作过渡层2。

127.使用金属有机物化学气相淀积技术在温度为820℃,压强为42torr,氢气流量为

4300sccm,氨气流量为4300sccm,铝源流量为21μmol/min的工艺条件下,在硅衬底1上外延厚度为400nm的aln材料,形成过渡层2。

128.第二步.在过渡层2上外延gan材料,形成沟道层3。

129.使用金属有机物化学气相淀积技术在温度为970℃,压强为44torr,氢气流量为4400sccm,氨气流量为4400sccm,镓源流量为110μmol/min的工艺条件下,在过渡层2上外延厚度为6.6μm的gan材料,形成沟道层3。

130.第三步.在沟道层3上淀积未掺杂的al

0.1

ga

0.9

n制作势垒层4。

131.使用金属有机物化学气相淀积技术在温度为990℃,压强为44torr,氢气流量为4500sccm,氨气流量为4500sccm,镓源流量为36μmol/min,铝源流量为8μmol/min的工艺条件下,在gan沟道层3上淀积厚度为40nm,且铝组分为0.1的未掺杂al

0.1

ga

0.9

n势垒层4。

132.第四步.在势垒层4上制作p型层。

133.使用磁控溅射技术,在溅射功率为110w,温度300℃,ar流量为20sccm,o2流量为30sccm的工艺条件下,在势垒层4上外延掺杂浓度为5

×

10

15

cm-3

、厚度为500nm的nio材料,形成p型nio层。

134.第五步.在p型层上外延介质材料hfo2,形成介质层。

135.使用射频磁控反应溅射技术,在反应室溅射气压保持在0.1pa左右,o2和ar的流量分别为1sccm和8sccm,基片温度固定在200℃,hf靶射频功率为150w的工艺条件下,在p型nio层上外延厚度为100nm的hfo2材料,形成介质层。

136.第六步.刻蚀形成隔离深槽5。

137.6.1)在该hfo2介质层上第一次制作掩膜,利用该掩膜使用反应离子刻蚀技术,在cf4流量为45sccm,o2流量为5sccm,压强为15mt,功率为250w工艺条件下,对hfo2介质层进行刻蚀,刻蚀至p型层上表面为止;

138.6.2)在cl2流量为18sccm,压强为14mtorr,功率为120w的工艺条件下,再次利用第一次制作的掩膜对p型层、势垒层4、沟道层3依次进行刻蚀,刻蚀至沟道层3内部,刻蚀总深度为600nm,形成四个深槽,这四个深槽构成了隔离深槽5;该隔离深槽5将沟道层3和势垒层4分成五个条状结构。

139.第七步.刻蚀形成左p型块6、右p型块7、左介质块8与右介质块9。

140.7.1)在第六步刻蚀后的介质层、p型层、沟道层3、势垒层4与隔离深槽5上第二次制作掩膜,利用该掩膜在cf4流量为45sccm,o2流量为5sccm,压强为15mt,功率为250w的刻蚀工艺条件下,使用反应离子刻蚀技术对介质层再次进行刻蚀,刻蚀至p型层的上表面为止,形成左介质块8与右介质块9;

141.7.2)再次利用第一次制作的掩膜,在cl2流量为18sccm,压强为14mtorr,功率为120w的工艺条件下,对p型层进行刻蚀,刻蚀至势垒层4的上表面为止,形成左p型块6与右p型块7;

142.第八步.在势垒层4上制作左电极10、右电极11与节点12。

143.在沟道层3、势垒层4、隔离深槽5、左介质块8与右介质块9上第三次制作掩膜,利用该掩膜在势垒层4上部的左、右两侧以及中部,使用电子束蒸发技术在真空度小于1.9

×

10-3

pa,功率为510w,蒸发速率小于的工艺条件下,淀积多层金属ta、pt和au,其厚度分别为0.122μm/0.317μm/0.161μm,并在温度为880℃的n2气氛中进行快速热退火30s,从左至

右依次形成左电极10、节点12与右电极11。

144.第九步.制作第一电极15与第二电极16。

145.9.1)在沟道层3、势垒层4、隔离深槽5、左介质块8、右介质块9、左电极10、右电极11与节点12上第四次制作掩膜,利用该掩膜使用反应离子刻蚀,在cl2流量为18sccm,压强为14mtorr,功率为120w工艺条件下,对左p型块6右侧与右p型块7右侧的势垒层4与沟道层3依次进行刻蚀,刻蚀总深度h为70nm,在每个左p型块6右侧与每个右p型块7右侧均形成六个大小相同且等间距排列的矩形槽;每个左p型块6右侧的六个矩形槽构成左凹槽13,每个右p型块7右侧的六个矩形槽构成右凹槽14;

146.9.2)在沟道层3、势垒层4、隔离深槽5、左介质块8、右介质块9、左电极10、右电极11、节点12、左凹槽13与右凹槽14上第五次制作掩模,利用该掩膜采用电子束蒸发技术,在真空度小于1.8

×

10-3

pa,功率为500w,蒸发速率小于工艺条件下,在每个左凹槽13内部及左凹槽13两侧的势垒层4上部、右凹槽14内部及右凹槽14两侧的势垒层4上部分别淀积厚度分别为0.063μm/0.037μm的金属组合ti/au,形成六个t型金属条,依次构成第一电极15与第二电极16。

147.第十步.在左介质块8与右介质块9上分别制作栅极17与栅极18。

148.在沟道层3、势垒层4、隔离深槽5、左介质块8、右介质块9、左电极10、右电极11、节点12、第一电极15与第二电极16上第六次制作掩膜,利用该掩膜采用电子束蒸发技术,在真空度小于1.8

×

10-3

pa,功率为530w,蒸发速率小于的工艺条件下,在左介质块8与右介质块9上部蒸发金属组合pt/au,其厚度分别为0.528μm/0.262μm,分别形成左栅极17与右栅极18;完成整个器件的制作。

149.本发明的效果可通过以下仿真进一步说明。

150.仿真内容:对本发明实施例一分别进行输出特性和阻断特性仿真,结果如图6,其中:

151.图6(a)为输出特性曲线图,图6(b)为双向阻断特性图,由图6可以看出,本发明器件的开启电压小于0.2v,且正向阻断电压为1437v,反向阻断电压为-1401v,表明本发明器件具有良好的单向导通特性和双向阻断特性。

152.以上描述仅是本发明的三个具体实施例,并不构成对本发明的限制,显然对于本领域的专业人员来说,在了解了本发明内容和原理后,能够在不背离本发明的原理和范围的情况下,根据本发明的方法进行形式和细节上的各种修正和改变,但是这些基于本发明的修正和改变仍在本发明的权利要求保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1