银烧结接合用镀覆方法、银烧结接合用镀膜、功率模块用基板、半导体元件和半导体装置与流程

本发明涉及一种用于银烧结接合的镀覆方法、用于银烧结接合的镀膜、功率模块(power module)用基板、半导体元件及半导体装置。

背景技术:

1、作为功率半导体,一直以来使用si(硅)半导体。而且,近年来与si半导体相比,可在更高温下工作的sic(碳化硅)半导体及gan(氮化镓)半导体的使用正在增加。因此,预计半导体的工作温度为高温至200℃以上,将半导体元件接合到基板的芯片键合部的耐热性也变得必要。因此,作为所关注的接合技术之一,有银烧结接合。另一方面,为了进行银烧结接合,需要对基板等接合的部件进行表面处理,通过该表面处理形成的覆膜也同样需要耐热性。

2、例如,专利文献1中公开了通过由作为基底层的镍镀膜和形成于镍镀膜上的特定合金镀膜构成的覆膜,从而提高了半导体元件与支承体的接合部即芯片贴装部中的耐热可靠性。

3、现有技术文献

4、专利文献

5、专利文献1:日本特开2018-46276号公报

技术实现思路

1、发明所要解决的问题

2、基板是在基材上设置由铜或铝形成的电路而形成的。而且,在半导体元件接合到电路时使用银烧结接合的情况下,为了确保良好的接合强度,有时在与银烧结层相接的电路的最表层使用银镀膜。虽然通过银镀膜获得良好的初始接合强度,但是银镀膜容易透氧,特别是在高温条件下,有可能导致铜、铝这样的基底金属的氧化,使接合强度降低,耐热性趋于变差。为了解决该问题,需要进一步设置基底金属的氧化阻挡层。

3、本发明人进行了深入研究,结果新判明:为了防止基底金属的氧化,可以将镍镀膜用作阻挡层,但不能充分地确保镍镀膜与银镀膜的密合性。

4、进一步,本发明人进行了深入研究,结果发现:作为镍镀膜与银镀膜之间的密合层,通过使用钯(pd)镀膜或铂(pt)镀膜等,能够确保镍镀膜与银镀膜的密合性,但由于钯和铂昂贵,因此也判明了存在成本的问题。

5、本发明的目的在于解决本发明人新发现的上述问题,提供一种能够低价地确保镍镀膜与银镀膜的密合性且具有良好的耐热性的用于银烧结接合的镀覆方法、用于银烧结接合的镀膜、具备该镀膜的功率模块用基板、具备该镀膜的半导体元件及具备该功率模块用基板的半导体装置。

6、解决问题的技术方案

7、本发明人进行了深入研究,结果发现:作为镍镀膜与银镀膜之间的密合层,通过使用银底镀(strike plating)(优选为化学银底镀)(st-ag)膜,能够低价地确保镍镀膜与银镀膜的密合性,还可以获得良好的耐热性,从而完成了本发明。

8、即,本发明涉及一种用于银烧结接合的镀覆方法,其包括以下工序:阻挡层形成工序,其在被镀覆面的上侧形成化学镍镀膜;中间层形成工序,其在化学镍镀膜的上侧形成化学银底镀膜;最表层形成工序,其在被镀覆面的最表层形成化学银镀膜。

9、上述化学银底镀膜的膜厚优选为0.010~0.200μm。

10、上述中间层形成工序优选为使用ph为5.0~9.0的置换型化学镀银浴,在化学镍镀膜的上侧形成化学银底镀膜的工序。

11、上述置换型化学镀银浴优选含有选自酰胺化合物和酰亚胺化合物中的至少一种络合剂。

12、上述置换型化学镀银浴优选含有选自酰胺化合物和酰亚胺化合物中的至少两种络合剂。

13、上述化学银镀膜的膜厚优选为0.2μm以上。

14、上述最表层形成工序优选为在被镀覆面的最表层使用还原型化学镀银浴来形成化学银镀膜的工序。

15、上述用于银烧结接合的镀覆方法中,镀膜的总膜厚优选为15μm以下。

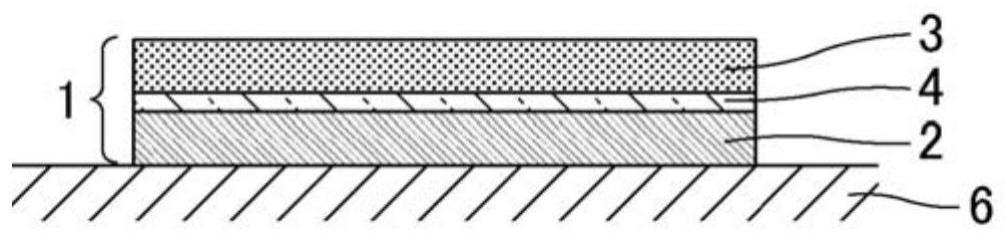

16、本发明还涉及一种用于银烧结接合的镀膜(镀膜层叠体),其具有:化学镍镀膜、在化学镍镀膜的上侧的化学银底镀膜和在最表层的化学银镀膜。

17、上述化学银底镀膜的膜厚优选为0.010~0.200μm。

18、上述化学银底镀膜优选为使用ph为5.0~9.0的置换型化学镀银浴,在化学镍镀膜的上侧形成的覆膜。

19、上述置换型化学镀银浴优选含有选自酰胺化合物和酰亚胺化合物中的至少一种络合剂。

20、上述置换型化学镀银浴优选含有选自酰胺化合物和酰亚胺化合物中的至少两种络合剂。

21、上述化学银镀膜的膜厚优选为0.2μm以上。

22、上述化学银镀膜优选为使用还原型化学镀银浴,在被镀覆面的最表层形成的覆膜。

23、上述镀膜中,镀膜的总膜厚优选为15μm以下。

24、本发明还涉及一种功率模块用基板,其具备:基材、形成于上述基材上的电路和形成于上述电路表面的上述镀膜。

25、上述电路优选为由铜和/或铝构成的电路。

26、上述镀膜的表面优选为银烧结接合面。

27、本发明还涉及一种半导体元件,其在表面具有上述镀膜。

28、本发明还涉及一种半导体装置,其具备:上述功率模块用基板和/或在表面具有上述镀膜的半导体元件。

29、上述半导体装置中,上述功率模块用基板和/或在表面具有上述镀膜的半导体元件所具有的上述镀膜的表面优选为银烧结接合面。

30、上述半导体装置还具备上述功率模块用基板、半导体元件,优选上述功率模块用基板的上述镀膜的表面与上述半导体元件通过银烧结接合。

31、该半导体装置中,上述半导体元件优选为在表面具有上述镀膜的半导体元件。

32、上述半导体装置还具备:功率模块用基板、在表面具有上述镀膜的半导体元件,

33、优选为上述半导体元件的上述镀膜的表面与上述功率模块用基板通过银烧结接合而成的半导体装置。

34、发明效果

35、根据本发明,是一种用于银烧结接合的镀覆方法,其包括以下工序:阻挡层形成工序,其在被镀覆面的上侧形成化学镍镀膜;中间层形成工序,其在化学镍镀膜的上侧形成化学银底镀膜;最表层形成工序,其在被镀覆面的最表层形成化学银镀膜,因此能够低价地确保镍镀膜与银镀膜的密合性且具有良好的耐热性。

36、另外,根据本发明,是一种用于银烧结接合的镀膜(镀膜层叠体),其具有:化学镍镀膜、在化学镍镀膜的上侧的化学银底镀膜、在最表层的化学银镀膜,由此能够低价地确保镍镀膜与银镀膜的密合性且具有良好的耐热性。

37、另外,根据本发明,是一种功率模块用基板,其具备:基材、形成于上述基材上的电路、形成于上述电路表面的特定镀膜(镀膜层叠体),因此能够低价地确保镍镀膜与银镀膜的密合性且具有良好的耐热性。

38、另外,根据本发明,是一种在表面具有特定的镀膜(镀膜层叠体)的半导体元件,因此能够低价地确保镍镀膜与银镀膜的密合性且具有良好的耐热性,是高可靠性的半导体元件。

39、另外,根据本发明,是一种半导体装置,其具备特定的功率模块用基板和/或特定的半导体元件,因此能够低价地确保镍镀膜与银镀膜的密合性且具有良好的耐热性,是高可靠性的半导体装置。

技术特征:

1.一种用于银烧结接合的镀覆方法,其包括以下工序:

2.根据权利要求1所述的镀覆方法,其中,所述化学银底镀膜的膜厚为0.010~0.200μm。

3.根据权利要求1或2所述的镀覆方法,其中,所述中间层形成工序是使用ph为5.0~9.0的置换型化学镀银浴,在化学镍镀膜的上侧形成化学银底镀膜的工序。

4.根据权利要求3所述的镀覆方法,其中,所述置换型化学镀银浴含有选自酰胺化合物和酰亚胺化合物中的至少一种络合剂。

5.根据权利要求3所述的镀覆方法,其中,所述置换型化学镀银浴含有选自酰胺化合物和酰亚胺化合物中的至少两种络合剂。

6.根据权利要求1~5中任一项所述的镀覆方法,其中,所述化学银镀膜的膜厚为0.2μm以上。

7.根据权利要求1~6中任一项所述的镀覆方法,其中,所述最表层形成工序是在被镀覆面的最表层使用还原型化学镀银浴来形成化学银镀膜的工序。

8.根据权利要求1~7中任一项所述的镀覆方法,其中,镀膜的总膜厚为15μm以下。

9.一种用于银烧结接合的镀膜,其具有:

10.根据权利要求9所述的镀膜,其中,所述化学银底镀膜的膜厚为0.010~0.200μm。

11.根据权利要求9或10所述的镀膜,其中,所述化学银底镀膜是使用ph为5.0~9.0的置换型化学镀银浴,在化学镍镀膜的上侧形成的覆膜。

12.根据权利要求11所述的镀膜,其中,所述置换型化学镀银浴含有选自酰胺化合物和酰亚胺化合物中的至少一种络合剂。

13.根据权利要求11所述的镀膜,其中,所述置换型化学镀银浴含有选自酰胺化合物和酰亚胺化合物中的至少两种络合剂。

14.根据权利要求9~13中任一项所述的镀膜,其中,所述化学银镀膜的膜厚为0.2μm以上。

15.根据权利要求9~14中任一项所述的镀膜,其中,所述化学银镀膜是使用还原型化学镀银浴,在被镀覆面的最表层形成的覆膜。

16.根据权利要求9~15中任一项所述的镀膜,其中,镀膜的总膜厚为15μm以下。

17.一种功率模块用基板,其是具备基材、形成于所述基材上的电路,和形成于所述电路表面的镀膜的功率模块用基板,其中,

18.根据权利要求17所述的功率模块用基板,其中,所述电路是由铜和/或铝构成的电路。

19.根据权利要求17或18所述的功率模块用基板,其中,所述镀膜的表面是银烧结接合面。

20.一种半导体元件,其在表面具有权利要求9~16中任一项所述的镀膜。

21.一种半导体装置,其具备:权利要求17~19中任一项所述的功率模块用基板和/或权利要求20所述的半导体元件。

22.根据权利要求21所述的半导体装置,其中,权利要求17~19中任一项所述的功率模块用基板和/或权利要求20所述的半导体元件所具有的所述镀膜的表面是银烧结接合面。

技术总结

本发明的目的在于提供一种能够低价地确保镍镀膜与银镀膜的密合性且具有良好的耐热性的用于银烧结接合的镀覆方法、用于银烧结接合的镀膜、具备该镀膜的功率模块用基板、具备该镀膜的半导体元件及具备该功率模块用基板的半导体装置。本发明提供一种用于银烧结接合的镀覆方法,其包括以下工序:阻挡层形成工序,其在被镀覆面的上侧形成化学镍镀膜;中间层形成工序,其在化学镍镀膜的上侧形成化学银底镀膜;最表层形成工序,其在被镀覆面的最表层形成化学银镀膜。

技术研发人员:大久保洋树,小田幸典,村山敬祐,佐藤雅亮

受保护的技术使用者:上村工业株式会社

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!