一种In+Ta共掺杂TiO2基巨介电陶瓷、制备方法及其应用与流程

一种in+ta共掺杂tio2基巨介电陶瓷、制备方法及其应用

技术领域

1.本发明涉及介电陶瓷制备技术领域,具体涉及一种in+ta共掺杂tio2基巨介电陶瓷、制备方法及其应用。

背景技术:

2.开发具有较好的频率和频率稳定性、巨介电常数和低介电损耗的高效高性能巨介电材料,可以实现微电子器件的小型化和高能量密度存储应用,(in+nb)共掺杂tio2具有高介电常数(≥104)和低介电损耗(≤0.05),以及良好的温度和频率稳定性。巨大的介电常数(cp)性能源自电子钉扎缺陷偶极子效应(epdd),nb掺杂产生的电子被束缚在这些复杂的缺陷偶极子中,这对共掺杂tio2的巨介电常数(cp)起着重要作用。这种材料良好的介电性能激发了对相关材料系统的大量研究。一般采用传统的烧结方法制备共掺杂tio2巨介电陶瓷。然而,一方面,常规烧结的高温(≥1400℃)和较长的保温时间(》4h)导致大量的能源消耗。另一方面,高温下较长的烧结时间会导致晶粒异常生长,从而导致烧结样品的最终电学性能变差。因此,有必要寻找一种新的烧结方法来降低烧结温度,缩短加工时间。

3.闪烧(fs)是一种新颖且具有潜力的烧结方法,可将3ysz陶瓷的烧结温度从1450℃降低到850℃,并将烧结时间大大缩短至5s左右。它在许多材料中得到了广泛的研究,包括离子导体(3ysz)、ceo2、电导体(tio2)、铁电体(batio3)、半导体和压敏陶瓷(zno)、钙钛矿(srtio3)和绝缘体(al2o3和y2o3)因为闪烧具有缩短烧结时间(从几小时到几秒)和减少炉温。尽管许多材料中都使用了闪烧,但其机理仍存在争议。为了解释闪烧现象,提出了三种主要机制,包括焦耳加热、弗伦克对成核和施加电压引起的电化学反应。

4.金红石型tio2是一种混合导体,因其在高温下具有出色的温度稳定性而成为理想的研究体系。近年来,已有一些关于金红石型tio2闪烧的研究报道,基于不同电场的不同扩散机制,在快速烧结tio2陶瓷中,离子电导率在低电场下占主导地位,在高电场下电导率占优。

5.王等人在the effect of atmosphere on the flash-sintering of nanoscale titania ceramics(scripta materialia 199(2021)113894)中提出了400v/cm的外加电场下,气氛(在空气和氩气中)对二氧化钛(tio2)纳米粉末的闪烧的影响,王等人在staged microstructural study of flash sintered titania(materialia 8(2019)100451)中提出了烧结条件(包括电场、电流密度限制和保持时间)对闪烧二氧化钛的微观结构和缺陷结构的影响,张等人在effects of phase and doping on flash sintering of tio2(journal of the ceramic society of japan 124(2016)296-300)中提出了不同掺杂(v或n)和初始粉末相(锐钛矿和金红石型初始粉末)对tio2陶瓷的快速烧结的影响,然而,通过闪烧制备的共掺杂tio2巨介电陶瓷的制备和电性能很少被研究。一方面,快速烧结可以细化晶粒并降低介电损耗。此外,它可以形成缺陷并使电子钉扎缺陷偶极子簇(epdd)更容易形成,从而提高介电性能。因此,采用闪烧制备共掺杂tio2巨介电陶瓷具有重要意义。

6.鉴于上述缺陷,本发明创作者经过长时间的研究和实践终于获得了本发明。

技术实现要素:

7.本发明的目的在于解决高温下较长的烧结时间会导致晶粒异常生长,从而导致烧结样品的最终电学性能变差的问题,提供了一种in+ta共掺杂tio2基巨介电陶瓷、制备方法及其应用。

8.为了实现上述目的,本发明公开了一种in+ta共掺杂tio2基巨介电陶瓷的制备方法,包括以下步骤:

9.s1:将氧化物粉末混合物在zro2介质的乙醇中球磨24h,然后在80℃烘箱中干燥24h得到预煅烧粉末;

10.s2:将步骤s1中得到的预煅烧粉末进行煅烧得到煅烧粉末;

11.s3:在与预煅烧粉末相同的球磨条件下将步骤s2得到的煅烧粉末进行二次球磨,然后在80℃下干燥24h;

12.s4:向步骤s3中得到的干燥粉末中加入粘合剂,在310mpa的压力下,将混合粉末单轴压制成圆盘;

13.s5:将步骤s4中得到的圆盘在650℃下烘烤2h以去除粘合剂;

14.s6:将步骤s5中得到的试样置于管式炉中,试样两端接直流电源提供电场,以10℃/min的加热速率加热;

15.s7:当样品温度达到1200℃时,保持5min后施加450v/cm~600v/cm的电场,初始预设电流为0.5a,当施加电场时,电流每5min增加0.1a直到达到限制电流0.7a,然后关闭直流电源,将样品冷却至室温。

16.所述步骤s2中煅烧温度为1000℃,煅烧时间为5h。

17.所述步骤s4中粘合剂为5wt.%聚乙烯醇。

18.所述步骤s4中圆盘厚度为2mm,直径为7mm的绿色圆盘。

19.所述步骤s5中升温速率为2℃/min。

20.本发明还公开了通过上述制备方法制得的in+ta共掺杂tio2基巨介电陶瓷以及这种in+ta共掺杂tio2基介电陶瓷在微电子器件中的应用。

21.与现有技术比较本发明的有益效果在于:本发明中这种in+ta共掺杂tio2基介电陶瓷的制备方法可将加工时间缩短15倍,烧结温度降低200℃,晶粒尺寸明显更小,组织更均匀,快速烧结具有与传统烧结相似的电性能,当电场为550v/cm时,快速烧结样品具有最好的介电性能,其中εr》104和tanδ≈0.36在103hz,同时,观察到两种介电异常,接近室温的介电异常归因于ti

3+

和ti

4+

之间的电荷转移,这有助于其巨大的介电性能。

附图说明

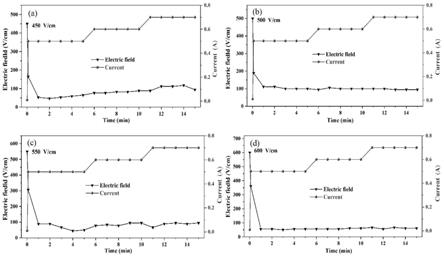

22.图1为电场作用下(in

0.5

ta

0.5

)

0.05

ti

0.95

o2样品的电场和电流随时间的变化,(a)fs450,(b)fs500,(c)fs550,(d)fs600;

23.图2为(in

0.5

ta

0.5

)

0.05

ti

0.95

o2样品在电场作用下的功率密度和估计的样品温度随时间的曲线,(a)fs450,(b)fs500,(c)fs550,(d)fs600;

24.图3为不同电场下常规固相烧结样品和闪速烧结样品的xrd谱图;

25.图4为常规烧结和闪烧结(in

0.5

ta

0.5

)

0.05

ti

0.95

o2样品在不同电场下的sem图,(a)cs1400,(b)fs450,(c)fs500,(d)fs550,(e)fs600;

26.图5为不同烧结方式下陶瓷样品室温介电性能,(a)介电常数(εr),(b)介质损耗(tanδ);

27.图6为(in

0.5

ta

0.5

)

0.05

ti

0.95

o2陶瓷样品在室温1khz下不同烧结方式和闪速烧结参数下的介电性能;

28.图7为不同频率下(in

0.5

ta

0.5

)

0.05

ti

0.95

o2陶瓷样品的介电常数和介电损耗随温度的变化,(a)cs1400,(b)fs550;

29.图8为不同频率下fs550陶瓷样品的介电损耗和介电模量随温度的变化,图中显示了该分量下的阿伦尼乌斯拟合,(a)tanδ,(b)m”;

30.图9为不同电场下常规烧结和闪烧结(in

0.5

ta

0.5

)

0.05

ti

0.95

o2样品的e-j曲线。

具体实施方式

31.以下结合附图,对本发明上述的和另外的技术特征和优点作更详细的说明。

32.一、圆盘准备

33.采用闪烧制备了组成为(in

0.5

ta

0.5

)

0.05

ti

0.95

o2的tio2基巨介电陶瓷。将氧化物粉末混合物在含zro2介质的乙醇中球磨24h,然后在80℃烘箱中干燥24h。干燥后的样品在1000℃下煅烧5h,以降低粉末的活性并去除内部的水分和杂质。在与预煅烧粉末相同的条件下对煅烧粉末进行第二次球磨以提高粉末的活性。然后再次在80℃下干燥24h。称取干燥后的粉末,慢慢倒入玛瑙研钵中,然后用胶头滴管加入粘合剂(5wt.%聚乙烯醇(pva))。在~310mpa的压力下,将混合粉末单轴压制成厚度~2mm、直径~7mm的圆盘。样品在650℃下以2℃/min的速度烘烤2h时以去除粘合剂。

34.二、烧结工艺

35.分别采用闪烧和常规烧结工艺制备了tio2基巨介电陶瓷。在常规烧结过程中,生坯在1400℃下保持4h,样品标记为cs1400。闪烧过程中,将试样置于管式炉中,试样两端接直流电源提供电场。圆柱胚在管式炉中以10℃/min的加热速率加热。当样品温度达到1200℃时,保持5min后施加450v/cm至600v/cm的电场。初始预设电流设置为0.5a,以降低功耗并避免闪烧过程中出现热节。当施加电场时,电流每5min增加0.1a(限制电流0.7a)。最后,关闭直流电源,将样品冷却至室温。通过在450v/cm到600v/cm的不同电场下闪烧制备的样品分别标记为fs450、fs500、fs550和fs600。

36.三、表征

37.采用阿基米德法测量了共掺杂tio2巨介电陶瓷的相对密度。将银浆涂覆在烧结后的圆柱形样品表面,在650℃下保持20min形成银电极。所制备的(in

0.5

ta

0.5

)

0.05

ti

0.95

o2陶瓷的物相分析采用bruck制造的x射线衍射仪(d8 advanced,德国)进行。采用fei公司制造的扫描电子显微镜(nano sem430,美国)对制备的陶瓷进行微观形貌分析。非欧姆特性(阈值场(v

t

)、漏电流(i

l

)和非线性系数(α))和介电特性采用压敏电阻直流参数计(cjp cj1001,china)和agilent hp4294a阻抗分析仪分别进行测量。

38.四、结果

39.图1为(in

0.5

ta

0.5

)

0.05

ti

0.95

o2陶瓷在不同电场(450v/cm、500v/cm、550v/cm、600v/cm)试样达到恒定炉温后保温5min的目的是使试样在烧结过程中受热均匀。注意到不同电场下闪烧第一阶段的时间几乎为0。这表明电场对闪烧第一阶段的时间有很大影响。梯度增

大电流的目的是为了保证样品烧结均匀,避免样品局部烧结的现象。施加不同的电场(450v/cm、500v/cm、550v/cm、600v/cm)后,电场急剧下降到165v/cm、189v/cm、306v/cm、361v/cm。当达到预设电流时,电场保持在约80v/cm。

40.图2显示了不同电场下闪烧样品的功率密度和估计样品温度随时间变化的曲线。值得注意的是,样品的功率密度与预测的温度趋势一致。闪速烧结有两个明显的特点:烧结时间短,升温速度快。因此,测量样品的温度非常重要。黑体辐射模型(bbr)用于预测样品的温度,忽略了热传导和对流的损失。样品在不同电场下的温度可由下式(1)计算:

[0041][0042]

式中t0为炉温,单位为k;w为样品耗散的电能,单位为w;a为试样表面积m2;ζ为stefan-boltzmann常数,值为5.67

×

10-8w

·

m-2

·

k-4

。该方程表明样品的发射率为1。大多数氧化物陶瓷的发射率大于0.9,这导致计算出的样品温度高于用真实发射率计算出的样品温度。一般来说,计算出的样品温度会高出100-200℃。

[0043]

闪烧的结果总结如表1所示。

[0044]

表1烧结结果总结

[0045][0046]

电场为450v/cm、500v/cm、550v/cm和600v/cm的陶瓷样品闪烧时,对应的峰值功率密度分别为0.19w/mm3、0.22w/mm3、0.36w/mm3和0.42w/mm3。可以看出,随着电场的增加,陶瓷样品的相应峰值功率密度也随之增加。当发生闪烧时,电场为450v/cm、500v/cm、550v/cm和600v/cm的陶瓷样品分别对应样品的预测温度1666℃、1700℃、1804℃、1848℃。预测的样品温度随着电场的增加而增加。这与峰值功率密度随电场的变化趋势一致。陶瓷样品的相对密度分别从50%增加到闪光烧结样品的91.8%、94.4%、95.2%、92.4%。很明显,随着电场的增加,相对密度先增加后减小。电场为600v/cm的样品密度低可能是由于闪烧时炉温较高,样品烧结不均匀,容易开裂。fs550样品相对于常规烧结样品具有更高的相对密度,如表1所示。

[0047]

图3显示了常规烧结样品和闪光烧结样品在不同电场下的xrd谱。所有样品都表现出典型的金红石结构(pdf#76-0320)。根据in和ta的离子半径,与ti的离子半径相近0320)。根据in和ta的离子半径,与ti的离子半径相近满足失配率原理,in和ta都可以代替ti的位置形成置换

固溶体。同时,固溶体的形成可以促进陶瓷的致密化过程,满足电子钉扎缺陷偶极子模型(epdd)。然而,除了金红石tio2衍射峰外,在fs500、fs550和fs600样品中在约38

°

处检测到额外的衍射峰,被鉴定为ta2o第二相。可能是闪烧过程不稳定造成的。

[0048]

图4显示了不同烧结方法制备的陶瓷样品的sem显微形貌。采用线性截距法测量陶瓷样品的平均晶粒尺寸。cs1400、fs450、fs500、fs550和fs600陶瓷样品的平均晶粒尺寸分别为14.99μm、3.28μm、1.31μm、1.47μm和1.32μm(见表1)。显然,常规烧结制备的共掺杂tio2陶瓷由于长时间高温烧结容易发生异常生长。电场作用下平均晶粒尺寸的减小可能是由于界面能的影响。一方面,这是由于晶界有一定程度的局部加热,降低了熵引起的能量;同时,这是因为电场和边界电荷之间的相互作用。因此,与常规烧结相比,快速烧结在细化晶粒方面可以发挥重要作用。

[0049]

图5显示了陶瓷样品在室温下不同烧结方法下的介电性能。如图5(a)所示,通过快速烧结制备的样品在很宽的频率范围内都达到了巨大的介电常数。在550v/cm的电场下,通过闪烧制备的最佳电性能,其介电常数为10319,介电损耗为0.36在频率为1khz。随着频率的增加,介电常数逐渐降低。fs600样品在104~106hz的频率范围内显示梯度下降,对应于图5(b)中的介电损耗峰值,这表明与空间电荷极化相关的弛豫过程。与常规烧结相比,fs600陶瓷样品的介电损耗峰向高频偏移,表明电场的施加会导致极化响应时间的缩短。fs450样品的介电常数较低,这可能是由于较低的密度和较低的电场所致。总的来说,闪烧制备的陶瓷样品在较低温度和较短时间下仍能保持良好的电学性能,为共掺杂tio2基巨介电陶瓷开辟了新的制备技术。

[0050]

图6为(in

0.5

ta

0.5

)

0.05

ti

0.95

o2巨介电陶瓷在1khz时的介电常数和介电损耗。由图可知,通过常规烧结和闪烧获得的陶瓷样品都达到了巨大的介电常数。常规烧结制备的陶瓷样品虽然具有较高的介电常数,但其介电损耗较高,难以应用于实际生产。与传统烧结相比,通过闪烧制备的陶瓷样品具有最佳介电损耗,在fs550下获得的值约为0.36,这可能与具有更细的晶粒尺寸有关。对于闪烧样品,陶瓷样品的介电常数随着电场的增加而逐渐增加,在fs550样品中获得了最好的介电性能,其中εr≈10319和tanδ≈0.36。

[0051]

图7为不同频率下(in

0.5

ta

0.5

)

0.05

ti

0.95

o2陶瓷样品的介电常数和介电损耗随温度的变化。从图中可以看出,介电常数增加随着温度的升高,这可能是由于在高温下界面处空间电荷的热运动增加。空间电荷含量越多,穿过晶体势垒的概率就越大,从而使得介电常数越高。此外,介电常数随着频率的增加而逐渐降低,这可能是极化衰减造成的。如图7(a)所示,常规烧结制备的样品在20-250℃温度范围内随着频率的增加,介电损耗峰向更高的温度移动,表明存在热活化行为。与常规烧结相比,fs550样品在该温度范围内没有出现明显的热活化,这可能与烧结方法有关。总体而言,采用闪烧技术制备的tio2基巨介电陶瓷还具有良好的介电温度稳定性。

[0052]

图8(a)显示了不同频率下介电损耗随温度的变化曲线。在所有频率范围内,介电损耗随温度逐渐增加。电模量通常被认为是多晶陶瓷中更有效的缺陷松弛形式。(in

0.5

ta

0.5

)

0.05

ti

0.95

o2陶瓷样品复数模量的虚部如图8(b)所示。复模数可以表示为:

[0053][0054]

其中i、ε、ε'、ε”、m'和m”分别为复介电常数、复介电常数的实部和虚部、复模量

的实部和虚部。图中可以清楚地看到介电弛豫峰。活动能可由arrhenius公式计算:

[0055][0056]

其中f、f0、kb、ea和t是弛豫峰的频率值、前因子、玻尔兹曼常数、活性能和开尔文温度。该公式计算出的活动能为0.453ev,与之前的结果相似。弛豫过程可以用maxwell-wagner弛豫来描述,这可能是由ti

4+

和ti

3+

之间的电荷转移引起的。

[0057]

图9显示了陶瓷样品在不同烧结方法下的e-j曲线。很明显,所有样品都具有压敏电阻特性,但这些样品的非线性系数很小。非线性系数是压敏电阻的一个重要性能压敏陶瓷的参数。主要说明当电位梯度和漏电流相近时,非线性系数越大,压敏电阻性能越好。不同烧结方法制备的陶瓷样品的阈值电压、漏电流和非线性系数如表2所示。

[0058]

表2不同烧结方法制备的陶瓷试样的压敏电阻性能

[0059] v

t

(v/mm)i

l

(μa)αfs45060.964512.7fs50015.634013.2fs55017.162813.4fs6007.004772.5cs140032.274992.1

[0060]

此外,闪烧制备的样品非线性系数高于常规烧结制备的样品,这可能是由于在掺杂条件下产生晶界势垒。在闪烧过程中,样品的非线性系数随着电场的增加先增大后减小。相反,漏电流随着电场的增加先减小后增大,这可能是由于fs550的样品密度较高,如表1所示。这与之前的报道一致。fs550样品表现出最好的压敏电阻性能,击穿电场为17.16v/mm,非线性系数为3.4,漏电流为281μa。虽然纯tio2不具有压敏电阻特性,但是在(in+ta)共掺杂tio2巨介电陶瓷中表现出压敏电阻特性,为闪烧法开发电容-压敏电阻器件提供了很好的研究方向。

[0061]

以上所述仅为本发明的较佳实施例,对本发明而言仅仅是说明性的,而非限制性的。本专业技术人员理解,在本发明权利要求所限定的精神和范围内可对其进行许多改变,修改,甚至等效,但都将落入本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1