时钟树电路和基于时钟树电路的信号传输方法与流程

1.本技术涉及集成电路技术领域,特别是涉及一种时钟树电路和基于时钟树电路的信号传输方法。

背景技术:

2.作为检测电路缺陷的一种方法,扫描链(scan)测试模式在大规模集成电路和汽车电子中是必选的。在带有微控制单元(microcontroller unit,mcu)和外设的系统中,功能模式一般具有丰富的时钟来源,常见的有:外灌管脚时钟、高速晶振时钟(hfxo)、利用hfxo产生的锁相环时钟(pll)、高速内置时钟(hfrc)、低速内置时钟(lfrc)和低速晶振时钟(lfxo)。不同于功能模式,扫描链测试模式下的时钟来源是一个时钟,为来自某个外灌的芯片管脚(pad)。

3.系统在扫描链测试模式下工作时,需要将在功能模式下不同的时钟来源需要切换为一个时钟来源来节省测试时间。然而,现有的时钟树电路的功能模式与扫描链测试模式对时序的要求不同。因此,为了实现时序收敛,现有的时钟树电路会在电路后端的时钟树实现上引入很多的缓冲(buffer)单元,导致芯片在功能模式下的动态功耗的增加。

技术实现要素:

4.基于此,有必要针对上述技术问题,提供一种能够降低芯片在功能模式下的动态功耗的时钟树电路和基于时钟树电路的信号传输方法。

5.第一方面,本技术提供了一种时钟树电路。所述电路包括:

6.扫描链测试模式时钟模块,所述扫描链测试模式时钟模块的输出端与时钟选择生成器的输入端电连接;

7.第一功能模式时钟模块组,所述第一功能模式时钟模块组的输出端与所述时钟选择生成器的输入端电连接;

8.时钟选择生成器,所述时钟选择生成器的输入端分别与所述扫描链测试模式时钟模块的输出端和所述第一功能模式时钟模块组的输出端电连接,所述时钟选择生成器的输出端与设备的输入端电连接;所述时钟选择生成器用于选择并生成功能模式时钟和扫描链测试模式时钟;

9.设备,所述设备的输入端与所述时钟选择生成器的输出端电连接。

10.在其中一个实施例中,所述电路还包括:

11.第二功能模式时钟模块组,所述第二功能模式时钟模块组的输出端与数据选择器的输入端电连接;

12.数据选择器,所述数据选择器的输入端分别与所述扫描链测试模式时钟模块的输出端和所述第二功能模式时钟模块组的输出端电连接,所述数据选择器的输出端与所述设备的输入端电连接。

13.在其中一个实施例中,所述电路还包括:

14.异步分频器,所述异步分频器的输入端与所述扫描链测试模式时钟模块的输出端电连接,所述异步分频器的输出端与所述数据选择器的输入端电连接。

15.在其中一个实施例中,所述异步分频器,用于响应于功能模式的开机指令,关闭所述异步分频器。

16.在其中一个实施例中,所述设备包括:高速设备和低速设备,所述第一功能模式时钟模块组包括:高速时钟模块组和低速时钟模块组;

17.所述高速时钟模块组的输出端与所述时钟选择生成器的输入端电连接;所述高速时钟模块组用于生成高速时钟,给所述高速设备提供工作时钟频率;

18.所述低速时钟模块组的输出端与所述时钟选择生成器的输入端电连接;所述低速时钟模块组用于生成低速时钟,给所述低速设备提供工作时钟频率;

19.所述时钟选择生成器的输入端分别与所述高速时钟模块组的输出端和所述低速时钟模块组的输出端电连接,所述时钟选择生成器的输出端分别与所述高速设备和所述低速设备电连接。

20.在其中一个实施例中,所述设备还包括:中速设备,所述电路还包括:

21.同步分频器,所述同步分频器的输入端与所述时钟选择生成器的输出端电连接,所述同步分频器的输出端分别与所述高速设备的输入端、所述中速设备的输入端和所述低速设备的输入端电连接,用于给所述中速设备提供工作时钟频率。

22.在其中一个实施例中,所述电路还包括:

23.模式生成器,所述模式生成器的输入端与所述扫描链测试模式时钟模块的输出端电连接,所述模式生成器的输出端与所述时钟选择生成器的输入端电连接,用于进入扫描链测试模式。

24.在其中一个实施例中,所述第一功能模式时钟模块组包括:高频时钟模块和非高频时钟模块;所述高频时钟模块为在第一功能模式时钟模块组中最高频率的时钟源;所述时钟选择生成器包括:

25.第一子时钟选择生成器,所述第一子时钟选择生成器的输入端分别与所述扫描链测试模式时钟模块的输出端和所述高频时钟模块的输出端电连接,所述第一子时钟选择生成器的输出端与第三子时钟选择生成器的输入端电连接;

26.第二子时钟选择生成器,所述第二子时钟选择生成器的输入端与所述非高频时钟模块的输出端电连接,所述第二子时钟选择生成器的输出端与第三子时钟选择生成器的输入端电连接;

27.第三子时钟选择生成器,所述第三子时钟选择生成器的输入端分别与所述第一子时钟选择生成器的输出端和所述第二子时钟选择生成器的输出端电连接,所述第三子时钟选择生成器的输出端与所述设备的输入端电连接。

28.在其中一个实施例中,所述电路还包括:

29.时钟分频器,所述时钟分频器的输入端与所述扫描链测试模式时钟模块的输出端电连接,所述时钟分频器的输出端与所述第二子时钟选择生成器的输入端电连接。

30.第二方面,本技术提供了一种基于时钟树电路的信号传输方法。所述方法应用于上述第一方面所述的时钟树电路,包括:

31.在功能模式下,响应于功能模式的开机指令,第一功能模式时钟模块组生成第一

功能模式时钟组,并将所述第一功能模式时钟组发送至时钟选择生成器;所述时钟选择生成器将所述第一功能模式时钟组发送至设备;

32.在扫描链测试模式下,响应于扫描链测试模式的开机指令,扫描链测试模式时钟模块生成扫描链测试模式时钟,并将所述扫描链测试模式时钟发送至所述时钟选择生成器;所述时钟选择生成器将所述扫描链测试模式时钟发送至设备。

33.上述扫描链测试模式下的时钟树电路和基于时钟树电路的信号传输方法,所述电路包括:扫描链测试模式时钟模块,所述扫描链测试模式时钟模块的输出端与时钟选择生成器的输入端电连接;第一功能模式时钟模块组,所述第一功能模式时钟模块组的输出端与所述时钟选择生成器的输入端电连接;时钟选择生成器,所述时钟选择生成器的输入端分别与所述扫描链测试模式时钟模块的输出端和所述第一功能模式时钟模块组的输出端电连接,所述时钟选择生成器的输出端与设备的输入端电连接;所述时钟选择生成器用于选择并生成功能模式时钟和扫描链测试模式时钟;设备,所述设备的输入端与所述时钟选择生成器的输出端电连接。这样,扫描链测试模式时钟与功能模式时钟组到达主系统时钟的路径相同,在扫描链测试模式下主时钟保持和功能模式的系统时钟路径一致,两种模式对时序的要求相同,减少对关键时序收敛造成的影响,减少在时钟树实现上引入缓冲(buffer)单元的数量,实现芯片在功能模式下的动态功耗的降低。

附图说明

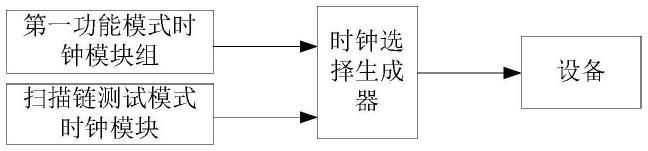

34.图1为一个实施例中时钟树电路的结构图;

35.图2为一个实施例中时钟树电路的结构图;

36.图3为一个实施例中带有ahb总线的时钟树电路结构图;

37.图4为一个实施例中基于时钟树电路的信号传输方法的流程示意图。

具体实施方式

38.为了使本技术的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处描述的具体实施例仅仅用以解释本技术,并不用于限定本技术。

39.本文中为部件所编序号本身,例如“第一”、“第二”等,仅用于区分所描述的对象,不具有任何顺序或技术含义。而本技术所说“连接”、“联接”,如无特别说明,均包括直接和间接连接(联接)。在本技术的描述中,需要理解的是,术语“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。

40.在本技术中,除非另有明确的规定和限定,第一特征在第二特征“上”或“下”可以是第一和第二特征直接接触,或第一和第二特征通过中间媒介间接接触。而且,第一特征在第二特征“之上”、“上方”和“上面”可是第一特征在第二特征正上方或斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”可以是第一特征在第二特征正下方或斜下方,或仅仅表示第一特征水平高度小于第二特征。

41.在一个实施例中,如图1所示,提供了一种时钟树电路,该电路包括:

42.扫描链测试模式时钟模块,扫描链测试模式时钟模块的输出端与时钟选择生成器的输入端电连接。

43.第一功能模式时钟模块组,第一功能模式时钟模块组的输出端与时钟选择生成器的输入端电连接。

44.时钟选择生成器,时钟选择生成器的输入端分别与扫描链测试模式时钟模块的输出端和第一功能模式时钟模块组的输出端电连接,时钟选择生成器的输出端与设备的输入端电连接。其中,时钟选择生成器用于选择并生成功能模式时钟和扫描链测试模式时钟。

45.设备,设备的输入端与时钟选择生成器的输出端电连接。

46.在本技术实施例中,该时钟树电路应用于集成电路。可以理解的是,集成电路可以为数模混合的集成电路。集成电路可以为深亚微米工艺的带有微控制单元(microcontroller unit,mcu)和外设的大规模芯片。例如,该时钟树电路应用于带有mcu和外设的汽车电子低功耗设计集成电路。扫描链测试模式时钟模块用于在扫描链测试模式下生成扫描链测试模式时钟。扫描链测试模式可以为scan(扫描)模式,扫描链测试模式时钟可以为scan模式时钟。scan扫描链测试模式用于测试数字功能器件。扫描链测试模式时钟模块可以为某个外灌的芯片管脚(pad)。第一功能模式时钟模块组为各第一功能模式时钟模块的组合。第一功能模式时钟模块组用于在功能模式下生成第一功能模式时钟组。第一功能模式时钟组可以包括:外灌管脚时钟、高速晶振时钟(hfxo)、利用高速晶振时钟产生的锁相环时钟(pll)、高速内置时钟(hfrc)、低速内置时钟(lfrc)和低速晶振时钟(lfxo)。时钟选择生成器包括至少一个数据选择器(multiplexer,mux)。设备包括:微控制单元(microcontroller unit,mcu)和外设。设备还可以包括静态随机存取存储器(static random-access memory,sram)。外设是指连在计算机主机以外的硬件设备,对数据和信息起着传输、转送和存储的作用,是计算机系统中的重要组成部分。

47.上述时钟树电路中,扫描链测试模式时钟、第一功能模式时钟组均与时钟选择生成器的输入端电连接,时钟选择生成器的输出端再与设备的输入端电连接。这样,扫描链测试模式时钟与功能模式时钟组到达主系统时钟的路径相同,在扫描链测试模式下主时钟保持和功能模式的系统时钟路径一致,两种模式对时序的要求相同,减少对关键时序收敛造成的影响,降低时序收敛难度,减少在时钟树实现上引入缓冲(buffer)单元的数量,实现芯片静态功耗的降低和在功能模式下的动态功耗的降低,也避免芯片面积的增加,减小芯片面积,降低成本。不仅如此,该时钟树电路能够在数字电路设计的rtl阶段实现,不需要依靠综合工具进行实现,结构非常合适移植和继承。此外,该时钟树电路的主时钟树结构具有层级精简的特点,扫描链测试模式所在的时钟路径短,减少了时钟源头的延迟,进一步有利于时序收敛,进一步降低芯片的功耗。

48.在一个实施例中,该时钟树电路还包括:

49.第二功能模式时钟模块组,第二功能模式时钟模块组的输出端与数据选择器的输入端电连接。

50.数据选择器,数据选择器的输入端分别与扫描链测试模式时钟模块的输出端和第二功能模式时钟模块组的输出端电连接,数据选择器的输出端与设备的输入端电连接。

51.在本技术实施例中,外设具备两个时钟体系,一个是mcu配置过来的总线读写寄存

器时钟(apb_clk或者ahb_clk),另外一个是设备自身的工作时钟,和配置总线处于异步关系。第二功能模式时钟模块组为各第二功能模式时钟模块的组合。第二功能模式时钟模块组用于在功能模式下生成第二功能模式时钟组,即在功能模式下生成设备自身的工作时钟。第二功能模式时钟组可以包括:高速外设时钟(high speed peripheral clock,hper_clk)、低速外设时钟(low speed peripheral clock,lper_clk)和中速外设时钟(medium speed peripheral clock,mper_clk)。

52.上述时钟树电路中,扫描链测试模式时钟、第二功能模式时钟组均与数据选择器的输入端电连接,数据选择器的输出端再与设备的输入端电连接。这样,扫描链测试模式时钟与功能模式时钟组到达设备的两条时钟路径均相同,即在扫描链测试模式下时钟路径和在功能模式下的时钟路径一致,两种模式对时序的要求相同,进一步降低时序收敛难度,进一步减少引入缓冲(buffer)单元,进一步降低芯片静态功耗和在功能模式下的动态功耗,也进一步减小芯片面积,进一步降低成本。

53.在一个实施例中,该时钟树电路还包括:

54.异步分频器,异步分频器的输入端与扫描链测试模式时钟模块的输出端电连接,异步分频器的输出端与数据选择器的输入端电连接。

55.在本技术实施例中,异步分频器用于对扫描链测试模式的主时钟进行异步的分频处理。

56.上述时钟树电路中,扫描链测试模式时钟通过异步分频器,实现与第二功能模式时钟组均与数据选择器的输入端电连接。这样,针对在功能模式下非主时钟通路存在系统时钟异步的时钟的情况,在扫描链测试模式下对扫描链测试模式的主时钟进行异步的分频处理,实现在功能模式下和在扫描链测试模式下均保持异步的时钟关系,能够进一步降低时序收敛的难度,保证关键时序路径可以非常集中,相较于依赖后端实现处理时高速外设和低速外设一起被盲目的集中到同一频率,能够进一步减小芯片面积,进一步降低静态功耗和动态功耗。

57.在一个实施例中,异步分频器,用于响应于功能模式的开机指令,关闭异步分频器。

58.在本技术实施例中,功能模式的开机指令用于指示开启功能模式。异步分频器包括:异步分频器门控时钟管理电路。异步分频器门控时钟管理电路用于响应于功能模式的开机指令,关闭异步分频器。

59.上述时钟树电路中,在功能模式下,异步分频器关闭。这样,异步分频器仅在扫描链测试模式下对扫描链测试模式的主时钟进行分频,对功能模式不产生影响,保证功能模式的稳定性,也避免了功耗的增加。

60.在一个实施例中,设备包括:高速设备和低速设备。第一功能模式时钟模块组包括:高速时钟模块组和低速时钟模块组。

61.高速时钟模块组的输出端与时钟选择生成器的输入端电连接。高速时钟模块组用于生成高速时钟,给高速设备提供工作时钟频率。

62.低速时钟模块组的输出端与时钟选择生成器的输入端电连接。低速时钟模块组用于生成低速时钟,给低速设备提供工作时钟频率。

63.时钟选择生成器的输入端分别与高速时钟模块组的输出端和低速时钟模块组的

输出端电连接,时钟选择生成器的输出端分别与高速设备和低速设备电连接。

64.在本技术实施例中,高速设备包括高速外设。高速外设是指脉宽发生器pwm,通用输入输出端口gpio、ram存储区等和mcu运行速度同频率的外设。低速设备包括低速外设。低速外设是指lpuart(低速串口设备)、rtc(万年历计数器)、lptimer(低功耗定时器)和wdt(看门狗)等设备。低速外设的工作时钟频率支持在最高32khz及其1至4096分频。高速时钟模块组为各高速时钟模块的组合。高速时钟模块组可以包括:高速晶振时钟(hfxo)模块,锁相环时钟(pll)模块和高速内部时钟(hfrc)模块。低速时钟模块组为各低速时钟模块的组合。低速时钟模块组可以包括:低速内部时钟(lfrc)模块和低速晶振时钟(lfxo)模块。高速时钟和低速时钟的频率倍数不小于1000倍。第一功能模式时钟模块组还包括外部时钟模块组。外部时钟模块组用于生成外部时钟组。外部时钟组包括调试mcu的协议时钟和pad外灌时钟。

65.上述时钟树电路中,在功能模式下,高速时钟模块组生成高速时钟,给高速设备提供工作时钟频率;低速时钟模块组生成低速时钟,给低速设备提供工作时钟频率。这样,在不同的设备之间的工作频率相差较大的情况下,对芯片进行测试的难度加大,上述时钟树电路与其他的时钟树电路之间的功耗差距和芯片面积差距均进一步加大。

66.在一个实施例中,设备还包括:中速设备,电路还包括:

67.同步分频器,同步分频器的输入端与时钟选择生成器的输出端电连接,同步分频器的输出端分别与高速设备的输入端、中速设备的输入端和低速设备的输入端电连接,用于给中速设备提供工作时钟频率。

68.在本技术实施例中,中速设备包括中速外设。在汽车集成电路中,中速外设指的是汽车外设can(控制器域网),spi(串行外设接口)等外设,通讯频率在1mhz到20mhz之间。同步分频器用于对高速时钟组分频。

69.上述时钟树电路中,通过同步分频器给中速设备提供工作时钟频率,保证中速设备正常工作。

70.在一个实施例中,如图2所示,时钟树电路包括:

71.扫描链测试模式时钟模块,扫描链测试模式时钟模块的输出端分别与时钟选择生成器的输入端和异步分频器的输入端电连接。

72.第一功能模式时钟模块组,第一功能模式时钟模块组的输出端与时钟选择生成器的输入端电连接。

73.时钟选择生成器,时钟选择生成器的输入端分别与扫描链测试模式时钟模块的输出端和第一功能模式时钟模块组的输出端电连接,时钟选择生成器的输出端与同步分频器的输入端电连接。

74.同步分频器,同步分频器的输入端与时钟选择生成器的输出端电连接,同步分频器的输出端分别与高速设备的输入端、中速设备的输入端和低速设备的输入端电连接。

75.异步分频器,异步分频器的输入端与扫描链测试模式时钟模块的输出端电连接,异步分频器的输出端与数据选择器的输入端电连接。

76.第二功能模式时钟模块组包括:第一分组、第二分组和第三分组。其中,第一分组,第一分组的输出端与第一选择器的输入端电连接。第二分组,第二分组的输出端与第二选择器的输入端电连接。第三分组,第三分组的输出端与第三选择器的输入端电连接。

77.数据选择器包括:第一选择器、第二选择器和第三选择器。其中,第一选择器,第一选择器的输入端分别与异步分频器的输出端和第一分组的输出端电连接,数据选择器的输出端与高速设备的输入端电连接。第二选择器,第二选择器的输入端分别与异步分频器的输出端和第二分组的输出端电连接,数据选择器的输出端与中速设备的输入端电连接。第三选择器,第三选择器的输入端分别与异步分频器的输出端和第三分组的输出端电连接,数据选择器的输出端与低速设备的输入端电连接。

78.高速设备,高速设备的输入端分别与同步分频器的输出端和第一选择器的输入端电连接。

79.中速设备,中速设备的输入端分别与同步分频器的输出端和第二选择器的输入端电连接。

80.低速设备,低速设备的输入端分别与同步分频器的输出端和第三选择器的输入端电连接。

81.在一个实施例中,该时钟树电路还包括:

82.模式生成器,模式生成器的输入端与扫描链测试模式时钟模块的输出端电连接,模式生成器的输出端与时钟选择生成器的输入端电连接,用于进入扫描链测试模式。

83.在本技术实施例中,模式生成器用于为不同的芯片提供不同的进入扫描链测试模式的方式。

84.上述时钟树电路中,扫描链测试模式时钟通过模式生成器,与时钟选择生成器的输入端电连接。这样,为不同的芯片提供不同的进入扫描链测试模式的方式,进一步提高了时钟树电路进行可移植性和可继承性。

85.在一个实施例中,第一功能模式时钟模块组包括:高频时钟模块和非高频时钟模块。高频时钟模块为在第一功能模式时钟模块组中最高频率的时钟源。

86.时钟选择生成器包括:

87.第一子时钟选择生成器,第一子时钟选择生成器的输入端分别与扫描链测试模式时钟模块的输出端和高频时钟模块的输出端电连接,第一子时钟选择生成器的输出端与第三子时钟选择生成器的输入端电连接。

88.第二子时钟选择生成器,第二子时钟选择生成器的输入端与非高频时钟模块的输出端电连接,第二子时钟选择生成器的输出端与第三子时钟选择生成器的输入端电连接。

89.第三子时钟选择生成器,第三子时钟选择生成器的输入端分别与第一子时钟选择生成器的输出端和第二子时钟选择生成器的输出端电连接,第三子时钟选择生成器的输出端与设备的输入端电连接。

90.在本技术实施例中,第一子时钟选择生成器、第二子时钟选择生成器和第三子时钟选择生成器均可以为数据选择器(mux)。第二子时钟选择生成器的数量与非高频时钟模块的数量相关。

91.上述时钟树电路中,将扫描链测试模式时钟和系统最高频率的时钟源走的路径保持一致,能够进一步减少场景应用下的时钟缓冲单元的数量,进一步减小芯片面积,进一步降低芯片的功耗。

92.在一个实施例中,该时钟树电路还包括:

93.时钟分频器,时钟分频器的输入端与扫描链测试模式时钟模块的输出端电连接,

时钟分频器的输出端与第二子时钟选择生成器的输入端电连接。

94.在本技术实施例中,时钟分频器用于在扫描链测试模式下对测试时钟进行分频。时钟分频器的数量可以和与第二子时钟选择生成器的输入端电连接的第一功能模式时钟模块的数量相同。每个时钟分频器可以配置不同的分频比。时钟分频器可以为同步分频器,也可以为异步分频器。时钟分频器为异步分频器,能够在扫描链测试模式下减少不同时钟之间互相影响,避免为了减少不同时钟之间互相影响而增加芯片面积,进一步减小芯片面积。

95.上述时钟树电路中,将扫描链测试模式时钟通过时钟分频器,实现与第二子时钟选择生成器的输入端电连接。这样,对扫描链测试模式时钟进行分频,保持与在功能模式下相同的频率对应关系,实现扫描链测试模式下和功能模式下的时钟关联性和频率的关系数量级上进一步保持一致,能够进一步减少场景应用下的时钟缓冲单元的数量,进一步减小芯片面积,进一步降低芯片的功耗。

96.在一个实施例中,如图3所示,时钟树电路包括:

97.第一功能模式时钟模块组,第一功能模式时钟模块组包括:高速晶振时钟模块301、低速晶振时钟模块302、高速内置时钟模块303、低速内置时钟模块304、外部时钟模块305和锁相环时钟模块309。其中,高速晶振时钟模块301,高速晶振时钟模块301的输出端与数据选择器308的输入端电连接。低速晶振时钟模块302,低速晶振时钟模块302的输出端与数据选择器310的输入端电连接。高速内置时钟模块303,高速内置时钟模块303的输出端与数据选择器311的输入端电连接。低速内置时钟模块304,低速内置时钟模块304的输出端与数据选择器312的输入端电连接。外部时钟模块305,外部时钟模块305的输出端与数据选择器313的输入端电连接。锁相环时钟模块309,锁相环时钟模块309的输入端与数据选择器308的输出端电连接,锁相环时钟模块309的输出端与数据选择器314的输入端电连接,锁相环时钟模块309输出的锁相环时钟(pll)的输出范围是72mhz到500mhz。

98.扫描链测试模式时钟模块306,扫描链测试模式时钟模块306的输出端与模式生成器307的输入端电连接。

99.模式生成器307,模式生成器307的输入端与扫描链测试模式时钟模块306的输出端电连接,模式生成器307的输出端分别与数据选择器308的输入端、异步分频器324的输入端、异步分频器325的输入端、数据选择器326的输入端、数据选择器327的输入端、数据选择器330的输入端、数据选择器331的输入端、时钟分频器315的输入端、时钟分频器316的输入端、时钟分频器317的输入端和时钟分频器318的输入端电连接。

100.时钟选择生成器,时钟选择生成器包括:数据选择器308、310-314。其中,数据选择器308,数据选择器308的输入端分别与高速晶振时钟模块301的输出端和扫描链测试模式时钟模块306的输出端电连接,数据选择器308的输出端与锁相环时钟模块309的输入端电连接。数据选择器310,数据选择器310的输入端分别与低速晶振时钟模块302的输出端和时钟分频器315的输出端电连接,数据选择器310的输出端与数据选择器314的输入端电连接。数据选择器311,数据选择器311的输入端分别与高速内置时钟模块303的输出端和时钟分频器316的输出端电连接,数据选择器311的输出端与数据选择器314的输入端电连接。数据选择器312,数据选择器312的输入端分别与低速内置时钟模块304的输出端和时钟分频器317的输出端电连接,数据选择器312的输出端与数据选择器314的输入端电连接。数据选择

器313,数据选择器313的输入端分别与外部时钟模块305的输出端和时钟分频器318的输出端电连接,数据选择器313的输出端与数据选择器314的输入端电连接。数据选择器314,数据选择器314的输入端分别与锁相环时钟模块309的输出端、数据选择器310的输出端、数据选择器311的输出端、数据选择器312的输出端和数据选择器313的输出端电连接,数据选择器314的输出端分别与同步分频器319的输入端、同步分频器320的输入端和系统总线转外围总线桥323的输入端电连接。

101.时钟分频器,时钟分频器包括:时钟分频器315-318。其中,时钟分频器315,时钟分频器315的输入端与模式生成器307的输出端电连接,时钟分频器315的输出端与数据选择器310的输入端电连接。时钟分频器316,时钟分频器316的输入端与模式生成器307的输出端电连接,时钟分频器316的输出端与数据选择器311的输入端电连接。时钟分频器317,时钟分频器317的输入端与模式生成器307的输出端电连接,时钟分频器317的输出端与数据选择器312的输入端电连接。时钟分频器318,时钟分频器318的输入端与模式生成器307的输出端电连接,时钟分频器318的输出端与数据选择器313的输入端电连接。

102.同步分频器,同步分频器包括:同步分频器319-320。同步分频器319,同步分频器319的输入端与数据选择器314的输出端电连接,同步分频器319的输出端与静态随机存取存储器321的输入端电连接。同步分频器320,同步分频器320的输入端与数据选择器314的输出端电连接,同步分频器320的输出端与微控制单元322的输入端电连接。

103.设备,设备包括:静态随机存取存储器321、微控制单元322、高速外设332-333、低速外设334-335和中速外设336-337。其中,静态随机存取存储器321,静态随机存取存储器321的输入端与同步分频器319的输出端电连接。微控制单元322,微控制单元322的输入端分别与同步分频器320的输出端电连接。高速外设332,高速外设332的输入端分别与系统总线转外围总线桥323的输出端和数据选择器326的输出端电连接。高速外设333,高速外设333的输入端分别与系统总线转外围总线桥323的输出端和数据选择器327的输出端电连接。低速外设334,低速外设334的输入端分别与系统总线转外围总线桥323的输出端和数据选择器328的输出端电连接。低速外设335,低速外设335的输入端分别与系统总线转外围总线桥323的输出端和数据选择器329的输出端电连接。中速外设336,中速外设336的输入端分别与系统总线转外围总线桥323的输出端和数据选择器330的输出端电连接。中速外设337,中速外设337的输入端分别与系统总线转外围总线桥323的输出端和数据选择器331的输出端电连接。

104.系统总线转外围总线桥323,系统总线转外围总线桥323的输入端与数据选择器314的输出端电连接,系统总线转外围总线桥323的输出端分别与高速外设332的输入端、高速外设333的输入端、低速外设334的输入端、低速外设335的输入端、中速外设336的输入端和中速外设337的输入端电连接。

105.异步分频器,异步分频器包括:异步分频器324-325。其中,异步分频器324,异步分频器324的输入端与模式生成器307的输出端电连接,异步分频器324的输出端与数据选择器328的输入端电连接。异步分频器325,异步分频器325的输入端与模式生成器307的输出端电连接,异步分频器325的输出端与数据选择器329的输入端电连接。

106.数据选择器326,数据选择器326的输入端分别与高速外设时钟模块338的输出端和模式生成器307的输出端电连接,数据选择器326的输出端与高速外设332的输入端电连

接。

107.数据选择器327,数据选择器327的输入端分别与高速外设时钟模块339的输出端和模式生成器307的输出端电连接,数据选择器327的输出端与高速外设333的输入端电连接。

108.数据选择器328,数据选择器328的输入端分别与低速外设时钟模块340的输出端和异步分频器324的输出端电连接,数据选择器328的输出端与低速外设334的输入端电连接。

109.数据选择器329,数据选择器329的输入端分别与低速外设时钟模块341的输出端和异步分频器325的输出端电连接,数据选择器329的输出端与低速外设335的输入端电连接。

110.数据选择器330,数据选择器330的输入端分别与中速外设时钟模块342的输出端和模式生成器307的输出端电连接,数据选择器330的输出端与中速外设336的输入端电连接。

111.数据选择器331,数据选择器331的输入端分别与中速外设时钟模块343的输出端和模式生成器307的输出端电连接,数据选择器331的输出端与中速外设337的输入端电连接。

112.第二功能模式时钟模块组,第二功能模式时钟模块组包括:高速外设时钟模块338-339、低速外设时钟模块340-341和中速外设时钟模块342-343。其中,高速外设时钟模块338,高速外设时钟模块338的输出端与数据选择器326的输入端电连接。高速外设时钟模块339,高速外设时钟模块339的输出端与数据选择器327的输入端电连接。低速外设时钟模块340,低速外设时钟模块340的输出端与数据选择器328的输入端电连接。低速外设时钟模块341,低速外设时钟模块341的输出端与数据选择器329的输入端电连接。中速外设时钟模块342,中速外设时钟模块342的输出端与数据选择器330的输入端电连接。中速外设时钟模块343,中速外设时钟模块343的输出端与数据选择器331的输入端电连接。

113.基于同样的发明构思,本技术实施例还提供了一种用于实现上述所涉及的时钟树电路的基于时钟树电路的信号传输方法。该方法所提供的解决问题的实现方案与上述方法中所记载的实现方案相似,故下面所提供的一个或多个基于时钟树电路的信号传输方法实施例中的具体限定可以参见上文中对于时钟树电路的限定,在此不再赘述。

114.在一个实施例中,如图4所示,提供了一种基于时钟树电路的信号传输方法,该方法应用于上述时钟树电路中任一个时钟树电路,该方法包括以下步骤:

115.步骤401,在功能模式下,响应于功能模式的开机指令,第一功能模式时钟模块组生成第一功能模式时钟组,并将第一功能模式时钟组发送至时钟选择生成器。时钟选择生成器将第一功能模式时钟组发送至设备。

116.在本技术实施例中,在功能模式下,响应于功能模式的开机指令,第一功能模式时钟模块组生成第一功能模式时钟组。然后,第一功能模式时钟模块组将第一功能模式时钟组发送至时钟选择生成器。然后,时钟选择生成器将第一功能模式时钟组发送至设备。

117.步骤402,在扫描链测试模式下,响应于扫描链测试模式的开机指令,扫描链测试模式时钟模块生成扫描链测试模式时钟,并将扫描链测试模式时钟发送至时钟选择生成器。时钟选择生成器将扫描链测试模式时钟发送至设备。

118.在本技术实施例中,在扫描链测试模式下,响应于扫描链测试模式的开机指令,扫描链测试模式时钟模块生成扫描链测试模式时钟。然后,扫描链测试模式时钟模块将扫描链测试模式时钟发送至时钟选择生成器。然后,时钟选择生成器将扫描链测试模式时钟发送至设备。

119.应该理解的是,虽然如上所述的各实施例所涉及的流程图中的各个步骤按照箭头的指示依次显示,但是这些步骤并不是必然按照箭头指示的顺序依次执行。除非本文中有明确的说明,这些步骤的执行并没有严格的顺序限制,这些步骤可以以其它的顺序执行。而且,如上所述的各实施例所涉及的流程图中的至少一部分步骤可以包括多个步骤或者多个阶段,这些步骤或者阶段并不必然是在同一时刻执行完成,而是可以在不同的时刻执行,这些步骤或者阶段的执行顺序也不必然是依次进行,而是可以与其它步骤或者其它步骤中的步骤或者阶段的至少一部分轮流或者交替地执行。

120.以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

121.以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对本技术专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1