全精度数字积分控制器的FPGA实现方法与流程

全精度数字积分控制器的fpga实现方法

技术领域:

1.本发明涉及电子测量技术领域,尤其涉及一种用于精密源表的全精度数字积分控制器的fpga实现方法。

背景技术:

2.随着半导体器件研发、制造行业蓬勃发展,对半导体测试仪器的需求与日俱增。其中精密源表对于半导体iv表征测试是最为重要的一类仪器,却长期被国外品牌垄断。精密源表的核心技术之一便是内部基于fpga实现的高速负反馈控制器。

3.就现有技术而言,通常使用数字pid控制器作为负反馈控制器。对于精密源表而言,pid中的比例(p)环节与微分(d)环节收到测量信号中所叠加噪声的影响,会使控制效果恶化。而如果使用常规数字的滤波的方法对测量信号先进行低通滤波,则导致控制器带宽降低,将无法满足高速脉冲输出的要求。所以在本发明中,仅采用pid控制器的积分环节,所以用于精密源表负反馈控制的是一个纯积分器。

4.另一方面,目前基于fpga实现的定点数数字积分器均采用类似零极点滤波器的递归形式,在每个数据周期都必须进行截位运算。现有存在几点不足:

①

存在截位误差,容易导致控制器不稳定;

②

定点数积分运算存在溢出风险,易使控制器输出极性反转,造成剧烈振荡;

③

数据运算周期长,不利于控制的实时性。

5.因此,发明一种基于fpga编程实现,能够高效实时计算的、不含截位误差且能避免数据溢出的积分控制器,就成为了一项关键技术。

技术实现要素:

6.为了解决上述技术问题,本发明提出一种用于精密源表的全精度数字积分控制器的fpga实现方法,仅包含定点数数加减乘除的数字算法,由fpga对高速adc采样的数字信号进行实时积分计算,并能有效避免数据溢出,全精度输出。

7.本发明提供一种用于精密源表的全精度数字积分控制器的fpga实现方法,包括如下步骤:

8.一、系统数学模型的建立

9.积分控制器是指仅使用pid控制器中的积分环节。对设定值与测量值的偏差做积分,然后乘以积分系数后作为控制器输出。

10.对连续信号做负反馈纯积分控制的数学描述如下:

[0011][0012]

式中,ki是积分系数,决定闭环系统的阶跃响应的上升速度;d(τ)为τ时刻的设定值或称参考值;x(τ)为τ时刻的测量值;u(t)是对设定值与测量值偏差的积分,并作为控制器输出从而实现对系统的负反馈控制;

[0013]

对于数字负反馈控制系统而言,控制过程在fpga中进行离散时间域的实时计算。

设定值为用户编程写入fpga的数字信号;测量值则为高速adc的采样信号。对(1-1)式离散化可得:

[0014][0015]

式中,t是数字控制器的运算周期,等于adc工作频率的倒数(精密源表使用工作频率为4mhz的高速adc,故t为250ns);d[i]是i时刻的设定值或称参考值,由用户编程规定;x[i]是i时刻adc的采样值;u[n]即是对设定值与测量值偏差的累加求和,等同于连续时间域的积分运算;u[n]作为控制器输出由fpga外部接口写入dac、实现对系统的负反馈控制。

[0016]

二、全精度数字积分器基本结构的建立

[0017]

根据式(1-2)可写出系统在n-1时刻的控制输出:

[0018][0019]

将(1-2)式及(1-3)式展开:

[0020]

u[n]=ki·

t{d[n]+d[n-1]+

…

d[0]-x[n]-x[n-1]

‑…

x[0]}

ꢀꢀ

(2-2)

[0021]

u[n-1]=ki·

t{d[n-1]+d[n-2]+

…

d[0]-x[n-1]-x[n-2]

‑…

x[0]}

ꢀꢀ

(2-3)

[0022]

用(2-4)式减去(2-5)式可得:

[0023]

u[n]=u[n-1]+ki·

t{d[n]-x[n]}

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(2-4)

[0024]

因为ki·

t是一个常数,可令ki=ki·

t,于是(2-6)式可整理为:

[0025]

u[n]=u[n-1]+ki·

{d[n]-x[n]}

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(2-5)

[0026]

由此看出,对于fpga而言,仅需一个减法器、一个加法器和一个乘法器,至少在三个系统时钟周期内可完成积分器输出。

[0027]

三、全精度数字积分器的溢出校正

[0028]

在精密源表的硬件系统中,adc采用工作频率为4mhz的24位双极性ads1675芯片;dac采用工作频率为32mhz的14位双极性ad9744芯片。于是对照(2-5)式,采样信号x[n]、参考信号d[n]是24位有符号定点数;积分系数ki也取24位有符号定点数。于是对(2-5)式的计算可按以下过程分步计算:

[0029]

(1)计算参考信号与测量信号的偏差,记为e[n],有e[n]=d[n]-x[n],e[n]为全精度定点数减法器输出,字长在x[n]与d[n]的基础上扩展一位,即25位,于是得到式(2-5)中的d[n]-x[n];

[0030]

(2)使用快速性定点数乘法器执行ki·

e[n],输出记为

△

u,乘法器为全精度输出,字长为相乘两数字长之和,即49位,于是得到式(2-5)中等式右边两个相加项的第二项;

[0031]

(3)计算u[n-1]+

△

u,全精度加法器输出的字长相对扩展一位,即50位,积分器输出恒定为50位,由于(2-5)式描述的计算过程存在递归结构,如不对输出作截位处理,会有数据溢出的可能;

[0032]

(4)判断数据是否溢出:

①

如果u[n-1]》0,

△

u》0,u[n]《0同时成立,意味着两个正数相加得到负数,则发生溢出;

②

如果u[n-1]《0,

△

u《0,u[n]》0同时成立,意味着两个负数相加得到正数,则发生溢出;

[0033]

(5)对输出信号做溢出校正:如数据溢出后符号位是1,此时将积分器输出锁定为正向最大值(对于50位有符号数,正向最大值为2

49-1);如数据溢出后符号位是0,此时将积

分器输出锁定为负向最大值,(对于50位有符号数,负向最大值为2

49

)。

[0034]

本发明的有益效果是:该用于精密源表的全精度数字积分控制器的fpga实现方法基于fpga平台,能够高效实时计算,不含截位误差且能避免数据溢出,从而实现全精度输出。

附图说明:

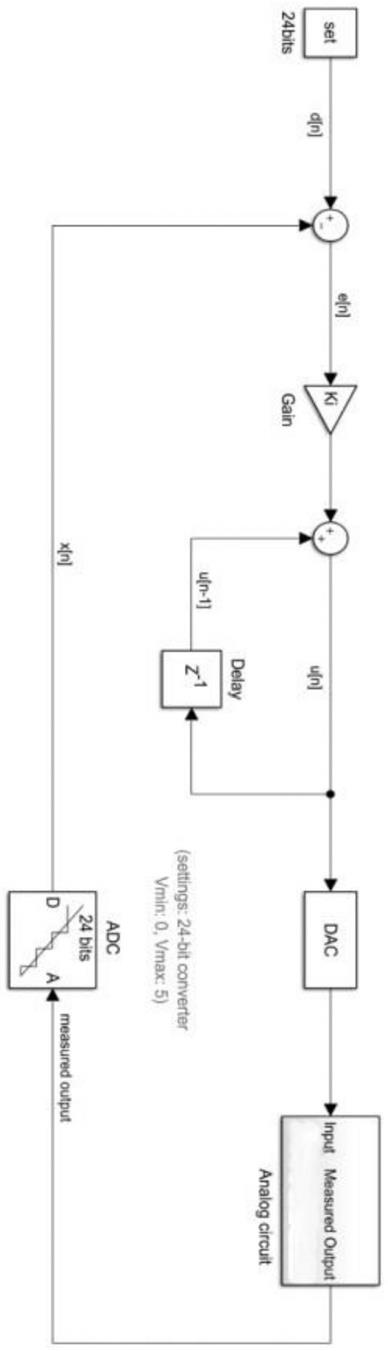

[0035]

图1是本发明的全精度数字积分器的基本结构示意图。

具体实施方式:

[0036]

下面结合附图对本发明的较佳实施例进行详细阐述,以使本发明的优点和特征能更易被本领域人员理解,从而对本发明的保护范围做出更为清楚明确的界定。

[0037]

本发明提供一种用于精密源表的全精度数字积分控制器的fpga实现方法,包括如下步骤:

[0038]

一、系统数学模型的建立

[0039]

对连续信号做负反馈纯积分控制的数学描述如下:

[0040][0041]

式中,ki是积分系数,决定闭环系统的阶跃响应的上升速度;d(τ)为τ时刻的设定值或称参考值;x(τ)为τ时刻的测量值;u(t)是对设定值与测量值偏差的积分,并作为控制器输出从而实现对系统的负反馈控制;

[0042]

对于数字负反馈控制系统而言,控制过程在fpga中进行离散时间域的实时计算。设定值为用户编程写入fpga的数字信号;测量值则为高速adc的采样信号。对(1-1)式离散化可得:

[0043][0044]

式中,t是数字控制器的运算周期,等于adc工作频率的倒数;d[i]是i时刻的设定值或称参考值,由用户编程规定;x[i]是i时刻adc的采样值;u[n]即是对设定值与测量值偏差的累加求和,等同于连续时间域的积分运算;u[n]作为控制器输出由fpga外部接口写入dac、实现对系统的负反馈控制。

[0045]

二、全精度数字积分器基本结构的建立

[0046]

根据式(1-2)可写出系统在n-1时刻的控制输出:

[0047][0048]

将(1-2)式及(1-3)式展开:

[0049]

u[n]=ki·

t{d[n]+d[n-1]+

…

d[0]-x[n]-x[n-1]

‑…

x[0]}

ꢀꢀ

(2-2)

[0050]

u[n-1]=ki·

t{d[n-1]+d[n-2]+

…

d[0]-x[n-1]-x[n-2]

‑…

x[0]}

ꢀꢀ

(2-3)

[0051]

用(2-4)式减去(2-5)式可得:

[0052]

u[n]=u[n-1]+ki·

t{d[n]-x[n]}

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(2-4)

[0053]

因为ki·

t是一个常数,可令ki=ki·

t,于是(2-6)式可整理为:

[0054]

u[n]=u[n-1]+ki·

{d[n]-x[n]}

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(2-5)

[0055]

由此看出,对于fpga而言,仅需一个减法器、一个加法器和一个乘法器,至少在三个系统时钟周期内可完成积分器输出。

[0056]

全精度数字积分器的基本结构图1所示,图1中的“analog circuit”是控制系统中模拟电路部分的抽象表征。

[0057]

三、全精度数字积分器的溢出校正

[0058]

在精密源表的硬件系统中,adc采用工作频率为4mhz的24位双极性ads1675芯片;dac采用工作频率为32mhz的14位双极性ad9744芯片。于是对照(2-5)式,采样信号x[n]、参考信号d[n]是24位有符号定点数;积分系数ki也取24位有符号定点数。于是对(2-5)式的计算可按以下过程分步计算:

[0059]

(1)计算参考信号与测量信号的偏差,记为e[n],有e[n]=d[n]-x[n],e[n]为全精度定点数减法器输出,字长在x[n]与d[n]的基础上扩展一位,即25位;

[0060]

(2)使用快速性定点数乘法器执行ki·

e[n],输出记为

△

u,乘法器为全精度输出,字长为相乘两数字长之和,即49位;

[0061]

(3)计算u[n-1]+

△

u,全精度加法器输出的字长相对扩展一位,即50位,积分器输出恒定为50位,由于(2-5)式描述的计算过程存在递归结构,如不对输出作截位处理,会有数据溢出的可能;

[0062]

(4)判断数据是否溢出:

①

如果u[n-1]》0,

△

u》0,u[n]《0同时成立,意味着两个正数相加得到负数,则发生溢出;

②

如果u[n-1]《0,

△

u《0,u[n]》0同时成立,意味着两个负数相加得到正数,则发生溢出;

[0063]

(5)对输出信号做溢出校正:如数据溢出后符号位是1,此时将积分器输出锁定为正向最大值(对于50位有符号数,正向最大值为2

49-1);如数据溢出后符号位是0,此时将积分器输出锁定为负向最大值,(对于50位有符号数,负向最大值为249)。

[0064]

以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1