数据传输电路、方法及存储装置与流程

1.本技术涉及集成电路领域,特别是涉及一种数据传输电路、方法及存储装置。

背景技术:

2.半导体存储装置通常包括存储阵列区和外围电路区,其中,存储阵列区设置有包括多个存储单元的存储单元阵列,外围电路区设置有控制读写的控制电路和用于存储设置参数的模式寄存器。存储在模式寄存器中的设置参数可以通过发出模式寄存器读命令读出。如果能够设置响应模式寄存器读命令读出设置参数的传输路径,与响应阵列区数据读命令读出阵列区数据的传输路径共用一数据发送通道,将数据准确地经由半导体存储装置的数据终端输出,能够有效减小数据传输电路占用空间的面积。

3.然而,对于特定类型的半导体存储装置来说,其内部工作电路的工作参数基本确定,且确定的功能单元电路一般需满足对应的标准,以满足客户定制化及批量化生产的要求。如何在满足特定类型的半导体存储装置的工作参数需求的前提下,设置响应模式寄存器读命令读出设置参数的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配,以实现响应模式寄存器读命令读出设置参数的传输路径,与响应阵列区数据读命令读出阵列区数据的传输路径共用一数据发送通道,成为设计特定类型半导体存储装置中数据传输电路的过程中亟待解决的技术难题之一。

技术实现要素:

4.基于此,有必要针对上述背景技术中的技术问题提供一种数据传输电路、方法及存储装置,能够在满足特定类型半导体存储装置的工作参数需求的前提下,设置响应模式寄存器读命令读出设置参数的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配。

5.为了实现上述目的及其他目的,本技术的一方面提供了一种数据传输电路,包括延迟模块及模式寄存器数据处理单元,延迟模块用于自接收模式寄存器读命令时刻起,延迟第一预设时间后,生成延迟读命令;模式寄存器数据处理单元与所述延迟模块连接,用于响应所述模式寄存器读命令从模式寄存器读出设置参数,以及还用于响应所述延迟读命令而输出所述设置参数。

6.于上述实施例中的数据传输电路中,通过设置延迟模块自接收模式寄存器读命令时刻起,延迟第一预设时间后,生成延迟读命令,使得模式寄存器数据处理单元响应所述模式寄存器读命令从模式寄存器读出设置参数,并响应所述延迟读命令而输出所述设置参数,从而使得响应模式寄存器读命令读出设置参数的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配,实现响应模式寄存器读命令读出设置参数的传输路径,与响应阵列区数据读命令读出阵列区数据的传输路径共用一数据发送通道,以减小数据传输电路占用面积。

7.在其中一个实施例中,所述延迟模块包括第一延迟单元、第二延迟单元及第三延

迟单元,第一延迟单元用于自接收所述模式寄存器读命令时刻起,延迟第二预设时间后,生成第一延迟读命令;第二延迟单元与所述第一延迟单元的输出端连接,用于自接收所述第一延迟读命令时刻起,延迟第三预设时间后,生成第二延迟读命令,所述第三预设时间与列选择控制模块的操作延迟相等;第三延迟单元与所述第二延迟单元的输出端及所述模式寄存器数据处理单元的输入端均连接,用于自接收所述第二延迟读命令时刻起,延迟第四预设时间后,生成所述延迟读命令;其中,所述第二预设时间、所述第三预设时间及所述第四预设时间之和,与所述第一预设时间相等。

8.于上述实施例中的数据传输电路中,通过设置延迟模块包括串联的第一延迟单元、第二延迟单元及第三延迟单元,设置第二延迟单元的延迟时间等于列选择控制模块的操作延迟,并设置第一延迟单元的延迟时间、第二延迟单元的延迟时间与第三延迟单元的延迟时间之和等于所述第一预设时间,使得响应模式寄存器读命令读出设置参数的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配,并避免特定类型半导体存储装置中列选择控制模块的操作延迟对传输电路的影响。

9.在其中一个实施例中,所述第三延迟单元包括第一子延迟单元及第二子延迟单元,第一子延迟单元与所述第二延迟单元的输出端连接,用于自接收所述第二延迟读命令时刻起,延迟第五预设时间后,生成第三延迟读命令,所述第五预设时间与读写放大器的操作延迟相等;第二子延迟单元与所述第一子延迟单元的输出端及所述模式寄存器数据处理单元的输入端均连接,用于自接收所述第三延迟读命令时刻起,延迟第六预设时间后,生成所述延迟读命令;其中,所述第五预设时间与所述第六预设时间之和,与所述第四预设时间相等。

10.于上述实施例中的数据传输电路中,通过设置第三延迟单元包括串联的第一子延迟单元及第二子延迟单元,设置第一子延迟单元的延迟时间等于读写放大器的操作延迟,并设置第一子延迟单元的延迟时间与第二子延迟单元的延迟时间之和等于第三延迟单元的延迟时间,使得响应模式寄存器读命令读出设置参数的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配,并避免特定类型半导体存储装置中读写放大器的操作延迟对传输电路的影响。

11.在其中一个实施例中,所述模式寄存器数据处理单元还包括先入先出指针处理单元及先入先出数据处理单元,先入先出指针处理单元与所述延迟模块的输出端连接,用于响应所述模式寄存器读命令生成第一指针信号,以及还用于响应所述延迟读命令生成第二指针信号;先入先出数据处理单元与所述先入先出指针处理单元及所述模式寄存器均连接,用于响应第一指针信号从模式寄存器读出设置参数,以及还用于响应所述第二指针信号输出所述设置参数。

12.于上述实施例中的数据传输电路中,通过设置模式寄存器数据处理单元包括先入先出指针处理单元及先入先出数据处理单元,先入先出指针处理单元根据模式寄存器读命令生成用于驱动先入先出数据处理单元从模式寄存器读出设置参数的第一指针信号,并根据延迟读命令生成用于驱动先入先出数据处理单元输出设置参数的第二指针信号,实现对响应模式寄存器读命令从模式寄存器读出设置参数的时间的精准控制,从而能够精准控制响应模式寄存器读命令读出设置参数的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配。

13.在其中一个实施例中,所述第一指针信号与所述第二指针信号的驱动时钟频率相同,以便于实现对先入先出数据处理单元读取数据与输出数据之间时间差的精准控制。

14.在其中一个实施例中,所述先入先出数据处理单元包括存储单元,多个所述存储单元的输出端均连接于同一节点;所述存储单元包括存储子单元和驱动器,所述驱动器的输入端连接于所述存储子单元的输出端,所述存储子单元在所述第一指针信号驱动下接收所述设置参数,所述驱动器在所述第二指针信号驱动下输出所述设置参数,使得先入先出数据处理单元配合先入先出指针处理单元,实现对响应模式寄存器读命令从模式寄存器读出设置参数的时间的精准控制,从而能够精准控制响应模式寄存器读命令读出设置参数的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配。

15.在其中一个实施例中,各所述存储子单元的数据输入端均连接于模式寄存器,以便于各所述存储子单元响应所述第一指针信号从所述模式寄存器读出设置参数。

16.在其中一个实施例中,所述的数据传输电路还包括命令解码电路及阵列区数据处理单元,命令解码电路的第一输出端与所述延迟模块的输入端及所述模式寄存器数据处理单元的输入端均连接,命令解码电路用于接收读命令,对所述读命令解码并判断所述读命令是否为所述模式寄存器读命令,若是,则输出所述模式寄存器读命令,反之,则生成阵列区数据读命令;阵列区数据处理单元的输入端与所述命令解码电路的第二输出端及存储单元阵列均连接,用于响应所述阵列区数据读命令而从所述存储单元阵列中读出阵列区数据。本实施例实现经由所述数据传输电路读出设置参数及阵列区数据,相对于采用不同的数据传输电路读出设置参数及阵列区数据,本实施例能够有效减小数据传输电路占用面积,以便于进一步提高半导体存储装置的集成度。

17.在其中一个实施例中,所述阵列区数据处理单元的操作延迟,与所述第一预设时间的差值为预设阈值,以满足特定类型半导体存储装置例如动态随机存取存储器(dynamic random access memory,dram)的工作参数需求。

18.在其中一个实施例中,所述预设阈值为列刷新周期的整数倍,以满足特定类型半导体存储装置例如lpddr4的工作参数需求。

19.在其中一个实施例中,所述的数据传输电路还包括第一选择器及先入先出存储器,第一选择器与所述阵列区数据处理单元的输出端及所述模式寄存器数据处理单元的输出端均连接;先入先出存储器与所述第一选择器的输出端连接,用于存储所述设置参数或所述阵列区数据。本实施例实现响应模式寄存器读命令读出设置参数的传输路径,与响应阵列区数据读命令读出阵列区数据的传输路径共用一数据发送通道,实现经由本技术提供的数据传输电路读出设置参数及阵列区数据,能够有效减小数据传输电路占用面积。

20.在其中一个实施例中,所述的数据传输电路还包括并串行转换电路及数据驱动模块,并串行转换电路与所述先入先出存储器的输出端连接;数据驱动模块与所述并串行转换电路的输出端连接,用于输出所述设置参数或所述阵列区数据,以提高数据传输的效率。

21.本技术的另一方面提供了一种存储装置,包括存储单元阵列、模式寄存器,以及如任一本技术实施例中所述的数据传输电路,使得响应模式寄存器读命令读出设置参数的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配,实现响应模式寄存器读命令读出设置参数的传输路径,与响应阵列区数据读命令读出阵列区数据的传输路径共用一数据发送通道,减小数据传输电路占用面积。

22.本技术的又一方面提供了一种数据传输方法,包括:

23.基于延迟模块响应模式寄存器读命令,生成延迟读命令,所述延迟模块的操作延迟为第一预设时间;

24.响应所述模式寄存器读命令,基于模式寄存器数据处理单元从模式寄存器读出设置参数;以及

25.响应所述延迟读命令,所述模式寄存器数据处理单元输出所述设置参数。

26.于上述实施例中的数据传输方法中,通过基于延迟模块自接收模式寄存器读命令时刻起,延迟第一预设时间后,生成延迟读命令,使得模式寄存器数据处理单元响应所述模式寄存器读命令从模式寄存器读出设置参数,并响应所述延迟读命令而输出所述设置参数,从而使得响应模式寄存器读命令读出设置参数的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配,实现响应模式寄存器读命令读出设置参数的传输路径,与响应阵列区数据读命令读出阵列区数据的传输路径共用一数据发送通道,以减小数据传输电路占用面积。

27.在其中一个实施例中,所述基于延迟模块响应模式寄存器读命令,生成延迟读命令,包括:

28.控制第一延迟单元自接收所述模式寄存器读命令时刻起,延迟第二预设时间后,生成第一延迟读命令;

29.控制第二延迟单元自接收所述第一延迟读命令时刻起,延迟第三预设时间后,生成第二延迟读命令,所述第三预设时间与列选择控制模块的操作延迟相等;

30.控制第三延迟单元自接收所述第二延迟读命令时刻起,延迟第四预设时间后,生成所述延迟读命令;其中,所述第二预设时间、所述第三预设时间及所述第四预设时间之和,与所述第一预设时间相等。

31.于上述实施例中的数据传输方法中,通过控制第一延迟单元自接收模式寄存器读命令时刻起,延迟第二预设时间后,生成第一延迟读命令;控制第二延迟单元自接收所述第一延迟读命令时刻起,延迟第三预设时间后,生成第二延迟读命令,所述第三预设时间与列选择控制模块的操作延迟相等;控制第三延迟单元自接收所述第二延迟读命令时刻起,延迟第四预设时间后,生成所述延迟读命令;其中,所述第二预设时间、所述第三预设时间及所述第四预设时间之和与所述第一预设时间相等;使得响应模式寄存器读命令读出设置参数的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配,并避免特定类型半导体存储装置中列选择控制模块的操作延迟对传输电路的影响。

32.在其中一个实施例中,所述基于延迟模块响应模式寄存器读命令,生成延迟读命令之前,还包括:

33.接收读命令;

34.对所述读命令解码并判断所述读命令是否为所述模式寄存器读命令;

35.若是,则输出所述模式寄存器读命令;

36.反之,则生成阵列区数据读命令;

37.响应所述阵列区数据读命令从存储单元阵列中读出阵列区数据。

38.于上述实施例中的数据传输方法中,通过对接收的读命令解码并判断所述读命令是否为所述模式寄存器读命令;若是,则输出所述模式寄存器读命令;反之,则生成阵列区

数据读命令;然后响应所述阵列区数据读命令从存储单元阵列中读出阵列区数据,基于模式寄存器数据处理单元响应所述模式寄存器读命令从模式寄存器读出设置参数,并响应延迟读命令并输出所述设置参数,其中,所述延迟读命令为延迟模块自接收模式寄存器读命令时刻起,延迟第一预设时间后生成;使得响应模式寄存器读命令读出设置参数的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配,实现响应模式寄存器读命令读出设置参数的传输路径,与响应阵列区数据读命令读出阵列区数据的传输路径共用一数据发送通道,减小数据传输电路占用面积,以便于进一步提高半导体存储装置的集成度。

附图说明

39.为了更清楚地说明本技术实施例技术中的技术方案,下面将对实施例技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

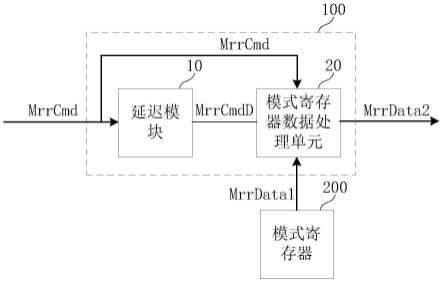

40.图1为本技术第一实施例中提供的一种数据传输电路的结构框图;

41.图2为本技术第二实施例中提供的一种数据传输电路的结构框图;

42.图3为本技术第三实施例中提供的一种数据传输电路的结构框图;

43.图4为本技术第四实施例中提供的一种数据传输电路的结构框图;

44.图5为本技术一实施例中提供的一种数据传输电路中先入先出数据处理单元的结构框图;

45.图6为本技术另一实施例中提供的一种数据传输电路中先入先出数据处理单元的结构框图;

46.图7为本技术第五实施例中提供的一种数据传输电路的结构框图;

47.图8a为本技术一实施例中提供的一种数据传输电路对读命令的响应时序示意图;

48.图8b为图7所示数据传输电路的工作时序示意图;

49.图9为本技术第六实施例中提供的一种数据传输电路的结构框图;

50.图10a为本技术第七实施例中提供的一种数据传输电路的结构框图;

51.图10b为图10a的一种实施方式示意图;

52.图11为本技术一实施例中提供的一种存储装置的结构框图;

53.图12为本技术一实施例中提供的一种数据传输方法的流程示意图;

54.图13为本技术另一实施例中提供的一种数据传输方法的流程示意图;

55.图14为本技术又一实施例中提供的一种数据传输方法的流程示意图。

56.附图标记说明:

57.100、数据传输电路;10、延迟模块;20、模式寄存器数据处理单元;200、模式寄存器;11、第一延迟单元;12、第二延迟单元;13、第三延迟单元;131、第一子延迟单元;132、第二子延迟单元;1101、第一读操作延迟单元;1201、列选择控制模块;1301、第三读操作延迟单元;21、先入先出指针处理单元;22、先入先出数据处理单元;221、存储单元;2211、存储子单元;2212、驱动器;30、命令解码电路;40、阵列区数据处理单元;300、存储单元阵列;50、第一选择器;60、先入先出存储器;70、并串行转换电路;80、数据驱动模块;501、第一触发器;502、第二触发器;503、第三触发器;504、第四触发器;400、延迟链;1000、存储装置;2000、延

迟电路。

具体实施方式

58.为了便于理解本技术,下面将参照相关附图对本技术进行更全面的描述。附图中给出了本技术的首选实施例。但是,本技术可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本技术的公开内容更加透彻全面。

59.除非另有定义,本文所使用的所有的技术和科学术语与属于本技术的技术领域的技术人员通常理解的含义相同。本文中在本技术的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本技术。

60.另外,贯穿说明书和跟随的权利要求中所使用的某些术语指代特定元件。本领域的技术人员会理解为,制造商可以用不同的名字指代元件。本文件不想要区分名字不同但是功能相同的元件。在以下的描述和实施例中,术语“包含”和“包括”都是开放式使用的,因此应该解读为“包含,但不限于

……”

。同样,术语“连接”想要表达间接或直接的电气连接。相应地,如果一个设备被连接到另一个设备上,连接可以通过直接的电气连接完成,或者通过其他设备和连接件的间接电气连接完成。

61.应当理解,尽管本文可以使用术语“第一”、“第二”等来描述各种元件,但是这些元件不应受这些术语的限制。这些术语仅用于将一个元件和另一个元件区分开。例如,在不脱离本技术的范围的情况下,第一元件可以被称为第二元件,并且类似地,第二元件可以被称为第一元件。

62.请参考图1,在本技术的一个实施例中,提供了一种数据传输电路100,包括延迟模块10及模式寄存器数据处理单元20,延迟模块10用于自接收模式寄存器读命令mrrcmd时刻起,延迟第一预设时间后,生成延迟读命令mrrcmdd;模式寄存器数据处理单元20与延迟模块10连接,用于响应模式寄存器读命令mrrcmd从模式寄存器200读出设置参数mrrdata1,模式寄存器数据处理单元20还用于响应延迟读命令mrrcmdd而输出设置参数mrrdata2。

63.作为示例,请继续参考图1,通过设置延迟模块10自接收模式寄存器读命令mrrcmd时刻起,延迟第一预设时间后,生成延迟读命令mrrcmdd,使得模式寄存器数据处理单元20响应模式寄存器读命令mrrcmd从模式寄存器200读出设置参数mrrdata1,并响应延迟读命令mrrcmdd而输出设置参数mrrdata2;可以根据具体需求设置延迟模块10的延迟时间,使得响应模式寄存器读命令mrrcmd读出设置参数mrrdata2的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配,实现响应模式寄存器读命令读出设置参数的传输路径,与响应阵列区数据读命令读出阵列区数据的传输路径共用一数据发送通道,以减小数据传输电路占用面积。这里的mrrdata1和mrrdata2可以相同,也可以匹配一种预设算法。

64.进一步地,请参考图2,在本技术的一个实施例中,延迟模块10包括第一延迟单元11、第二延迟单元12及第三延迟单元13,第一延迟单元11用于自接收模式寄存器读命令mrrcmd时刻起,延迟第二预设时间后,生成第一延迟读命令;第二延迟单元12与第一延迟单元11的输出端连接,用于自接收第一延迟读命令时刻起,延迟第三预设时间后,生成第二延迟读命令,第三预设时间与列选择控制模块的操作延迟相等;第三延迟单元13与第二延迟单元12的输出端及模式寄存器数据处理单元20的输入端均连接,用于自接收第二延迟读命令时刻起,延迟第四预设时间后,生成延迟读命令;其中,第二预设时间、第三预设时间及第

四预设时间之和与第一预设时间相等。

65.作为示例,请继续参考图2,通过设置延迟模块10包括串联的第一延迟单元11、第二延迟单元12及第三延迟单元13,设置第二延迟单元12的延迟时间等于列选择控制模块的操作延迟,并设置第一延迟单元11的延迟时间、第二延迟单元12的延迟时间与第三延迟单元13的延迟时间之和等于所述第一预设时间,使得响应模式寄存器读命令mrrcmd读出设置参数mrrdata2的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配,并避免特定类型半导体存储装置中列选择控制模块的操作延迟对传输电路的影响。

66.进一步地,请参考图3,在本技术的一个实施例中,第三延迟单元13包括第一子延迟单元131及第二子延迟单元132,第一子延迟单元131与第二延迟单元12的输出端连接,用于自接收所述第二延迟读命令时刻起,延迟第五预设时间后,生成第三延迟读命令,所述第五预设时间与读写放大器的操作延迟相等;第二子延迟单元132与第一子延迟单元131的输出端及模式寄存器数据处理单元20的输入端均连接,用于自接收所述第三延迟读命令时刻起,延迟第六预设时间后,生成所述延迟读命令;其中,所述第五预设时间与所述第六预设时间之和,与所述第四预设时间相等。

67.作为示例,请继续参考图3,通过设置第三延迟单元13包括串联的第一子延迟单元131及第二子延迟单元132,设置第一子延迟单元131的延迟时间等于读写放大器的操作延迟,并设置第一子延迟单元131的延迟时间与第二子延迟单元132的延迟时间之和等于第三延迟单元13的延迟时间,使得响应模式寄存器读命令mrrcmd读出设置参数mrrdata2的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配,并避免特定类型半导体存储装置中读写放大器的操作延迟对传输电路的影响。

68.进一步地,请参考图4,在本技术的一个实施例中,模式寄存器数据处理单元20还包括先入先出指针处理单元21及先入先出数据处理单元22,先入先出指针处理单元21与延迟模块10的输出端连接,用于响应模式寄存器读命令mrrcmd生成第一指针信号fifoin《n:0》,以及还用于响应延迟读命令mrrcmdd生成第二指针信号fifoout《n:0》;先入先出数据处理单元22与先入先出指针处理单元21及模式寄存器200均连接,用于响应第一指针信号fifoin《n:0》从模式寄存器200读出设置参数mrrdata1,以及还用于响应第二指针信号fifoout《n:0》输出设置参数mrrdata2。通过设置模式寄存器数据处理单元20包括先入先出指针处理单元21及先入先出数据处理单元22,其中,先入先出指针处理单元21根据模式寄存器读命令mrrcmd生成用于驱动先入先出数据处理单元22从模式寄存器200读出设置参数mrrdata1的第一指针信号fifoin《n:0》,n可以等于设置参数mrrdata1的位宽,并根据延迟读命令mrrcmdd生成用于驱动先入先出数据处理单元22输出设置参数mrrdata2的第二指针信号fifoout《n:0》,实现对响应模式寄存器读命令mrrcmd从模式寄存器200读出设置参数mrrdata1的时间的控制,从而能够控制响应模式寄存器读命令mrrcmd读出设置参数mrrdata2的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配。在本技术的一个实施例中,第一指针信号fifoin《n:0》与第二指针信号fifoout《n:0》的驱动时钟频率相同,以便于实现对先入先出数据处理单元22读取数据与输出数据之间时间差的精准控制。

69.进一步地,在本技术的一个实施例中,所述先入先出数据处理单元包括存储单元,多个所述存储单元的输出端均连接于同一节点;所述存储单元包括存储子单元和驱动器,所述驱动器的输入端连接于所述存储子单元的输出端,所述存储子单元在所述第一指针信

号驱动下接收所述设置参数,所述驱动器在所述第二指针信号驱动下输出所述设置参数。

70.作为示例,请参考图5,在本技术的一个实施例中,先入先出数据处理单元22包括8个存储单元221,8个存储单元221的输出端均连接于节点o;存储单元221包括存储子单元2211和驱动器2212,驱动器2212的输入端连接于存储子单元2211的输出端,存储子单元2211在第一指针信号fifoin《n:0》驱动下接收设置参数mrrdata1,n=8,驱动器2212在第二指针信号fifoout《n:0》驱动下输出设置参数mrrdata2,使得先入先出数据处理单元22配合先入先出指针处理单元21,实现对响应模式寄存器读命令mrrcmd从模式寄存器200读出设置参数mrrdata1的时间的精准控制,从而能够精准控制响应模式寄存器读命令mrrcmd读出设置参数mrrdata2的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配。

71.作为示例,请参考图6,在本技术的一个实施例中,各存储子单元2211的数据输入端均连接于模式寄存器200,以便于各存储子单元2211响应第一指针信号fifoin《n:0》从模式寄存器200读出设置参数mrrdata1。

72.进一步地,请参考图7,在本技术的一个实施例中,数据传输电路100还包括命令解码电路30及阵列区数据处理单元40,命令解码电路30的第一输出端与延迟模块10的输入端及模式寄存器数据处理单元20的输入端均连接,命令解码电路30用于接收读命令read,对读命令read解码并判断读命令read是否为模式寄存器读命令mrrcmd,若是,命令解码电路30输出模式寄存器读命令mrrcmd,反之,命令解码电路30生成阵列区数据读命令readcmd;阵列区数据处理单元40的输入端与命令解码电路30的第二输出端及存储单元阵列300均连接,用于响应阵列区数据读命令readcmd而从存储单元阵列300中读出阵列区数据arraydata。本实施例实现经由数据传输电路100读出设置参数mrrdata2及阵列区数据arraydata,相对于采用不同的数据传输电路100读出模式寄存器200中的设置参数mrrdata2及阵列区数据arraydata,本实施例能够有效减小数据传输电路100占用的面积,以便于进一步提高半导体存储装置的集成度。

73.进一步地,请继续参考图7,在本技术的一个实施例中,可以设置阵列区数据处理单元40的操作延迟与所述第一预设时间的差值为预设阈值,以满足特定类型半导体存储装置例如动态随机存取存储器(dynamic random access memory,dram)的工作参数需求。

74.作为示例,请参考图8a和图8b,在本技术的一个实施例中,可以设置第一指针信号fifoin《n:0》与模式寄存器读命令mrrcmd的频率相同,并设置第二指针信号fifoout《n:0》与延迟读命令mrrcmdd的频率相同,设置延迟读命令mrrcmdd的驱动时间与模式寄存器读命令mrrcmd的驱动时间的时间差为第一预设时间td,设置阵列区数据处理单元40的操作延迟与所述第一预设时间的差值为预设阈值,使得响应模式寄存器读命令mrrcmd读出设置参数mrrdata的时间,与响应阵列区数据读命令readcmd读出阵列区数据arraydata的时间匹配。

75.作为示例,在本技术的一个实施例中,可以设置预设阈值为列刷新周期的整数倍,以满足特定类型半导体存储装置例如lpddr4的工作参数的需求。

76.进一步地,请参考图9,在本技术的一个实施例中,数据传输电路100还包括第一选择器50及先入先出存储器60,第一选择器50与阵列区数据处理单元40的输出端及模式寄存器数据处理单元20的输出端均连接;先入先出存储器60与第一选择器50的输出端连接,用于存储设置参数mrrdata2或阵列区数据arraydata。本实施例能够实现响应模式寄存器读命令mrrcmd读出设置参数mrrdata2的传输路径,与响应阵列区数据读命令readcmd读出阵

列区数据arraydata的传输路径共用一数据发送通道,并经由先入先出存储器60向外输出,从而能够有效减小数据传输电路100占用的面积。

77.进一步地,请参考图10a及图10b,在本技术的一个实施例中,数据传输电路100还包括并串行转换电路70及数据驱动模块80,并串行转换电路70与先入先出存储器60的输出端连接;数据驱动模块80与并串行转换电路70的输出端连接,用于输出设置参数mrrdata2或阵列区数据arraydata。通过设置并串行转换电路70将先入先出存储器60提供的串行数据转化为串行数据后经由数据驱动模块80输出,以提高数据传输的效率。

78.作为示例,请继续参考图10b,可以将阵列区数据处理单元40响应阵列区数据读命令readcmd并读出阵列区数据arraydata的延迟时间等效为第一读操作延迟单元1101的延迟时间、列选择控制模块1201的操作延迟、第三读操作延迟单元1301的延迟时间之和,通过设置第二延迟单元12复制列选择控制模块1201的操作延迟,设置第一延迟单元11的延迟时间与第一读操作延迟单元1101的延迟时间匹配,并设置第三延迟单元13的延迟时间与第三读操作延迟单元1301的延迟时间匹配,使得响应模式寄存器读命令mrrcmd读出设置参数mrrdata2的时间,与响应阵列区数据读命令readcmd读出阵列区数据arraydata的时间匹配。为便于理解,做举例说明,继续参考图10b,例如第一读操作延迟单元1101的延迟时间为1纳秒,列选择控制模块1201的操作延迟为1.5纳秒(包括信号进入列选择控制模块1201的时间到存储单元阵列300输出arraydata的这段时间),第三读操作延迟单元1301的延迟时间为2纳秒,那么可以设置第一延迟单元11的延迟时间为1纳秒,设置第二延迟单元12的延迟时间为1.5纳秒,设置第三延迟单元13的延迟时间为2纳秒,即第一延迟单元11可以具有与第一读操作延迟单元1101一样的电路结构,第二延迟单元12可以模拟列选择控制模块1201操作存储单元阵列300的延迟时间(尽管电路结构不同,但延迟时间可以设置为相同),第三延迟单元13可以具有与第三读操作延迟单元1301一样的电路结构。

79.本技术中通过设置延迟模块10自接收模式寄存器读命令mrrcmd时刻起,延迟第一预设时间后,生成延迟读命令mrrcmdd,使得模式寄存器数据处理单元20响应模式寄存器读命令mrrcmd从模式寄存器200读出设置参数mrrdata1,并响应延迟读命令mrrcmdd而输出设置参数mrrdata2;可以根据具体需求设置延迟模块10的延迟时间,使得响应模式寄存器读命令mrrcmd读出设置参数mrrdata2的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配。本技术中可以设置延迟模块10的延迟时间跟随用于响应阵列区数据读命令读出阵列区数据的电路中功能模块的操作延迟,使得延迟模块10与被跟随的功能模块受工作环境变化的影响一致,从而能够有效避免因工作环境影响导致数据传输通路出现控制错误。

80.请参考图11,在本技术的一个实施例中,提供了一种存储装置1000,包括存储单元阵列300、模式寄存器200,以及如任一本技术实施例中的数据传输电路100。由于采用了如任一本技术实施例中的数据传输电路100来传输阵列区数据arraydata及设置参数mrrdata2,可以根据具体需求设置延迟模块10的延迟时间,使得响应模式寄存器读命令mrrcmd读出设置参数mrrdata2的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配,实现响应模式寄存器读命令读出设置参数的传输路径,与响应阵列区数据读命令读出阵列区数据的传输路径共用一数据发送通道,以减小数据传输电路占用面积。

81.请参考图12,在本技术的一个实施例中,提供了一种数据传输方法,包括:

82.步骤502,基于延迟模块响应模式寄存器读命令,生成延迟读命令,所述延迟模块

的操作延迟为第一预设时间;

83.步骤504,响应所述模式寄存器读命令,基于模式寄存器数据处理单元从模式寄存器读出设置参数;

84.步骤506,响应所述延迟读命令,所述模式寄存器数据处理单元输出所述设置参数。

85.具体地,请继续参考图12,通过控制延迟模块自接收模式寄存器读命令时刻起,延迟第一预设时间后,生成延迟读命令,使得模式寄存器数据处理单元响应所述模式寄存器读命令从模式寄存器读出设置参数,并响应所述延迟读命令而输出所述设置参数,从而使得响应模式寄存器读命令读出设置参数的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配,实现响应模式寄存器读命令读出设置参数的传输路径,与响应阵列区数据读命令读出阵列区数据的传输路径共用一数据发送通道,以减小数据传输电路占用面积。

86.进一步地,请参考图13,在本技术的一个实施例中,所述基于延迟模块响应模式寄存器读命令,生成延迟读命令,包括:

87.步骤5021,控制第一延迟单元自接收所述模式寄存器读命令时刻起,延迟第二预设时间后,生成第一延迟读命令;

88.步骤5022,控制第二延迟单元自接收所述第一延迟读命令时刻起,延迟第三预设时间后,生成第二延迟读命令,所述第三预设时间与列选择控制模块的操作延迟相等;

89.步骤5023,控制第三延迟单元自接收所述第二延迟读命令时刻起,延迟第四预设时间后,生成所述延迟读命令;其中,所述第二预设时间、所述第三预设时间及所述第四预设时间之和,与所述第一预设时间相等。

90.具体地,请继续参考图13,通过控制第一延迟单元自接收模式寄存器读命令时刻起,延迟第二预设时间后,生成第一延迟读命令;控制第二延迟单元自接收所述第一延迟读命令时刻起,延迟第三预设时间后,生成第二延迟读命令,所述第三预设时间与列选择控制模块的操作延迟相等;控制第三延迟单元自接收所述第二延迟读命令时刻起,延迟第四预设时间后,生成所述延迟读命令;其中,所述第二预设时间、所述第三预设时间及所述第四预设时间之和与所述第一预设时间相等;使得响应模式寄存器读命令读出设置参数的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配,并避免特定类型半导体存储装置中列选择控制模块的操作延迟对传输电路的影响。

91.进一步地,请参考图14,在本技术的一个实施例中,所述基于延迟模块响应模式寄存器读命令,生成延迟读命令之前,还包括:

92.步骤5011,接收读命令;

93.步骤5012,对所述读命令解码并判断所述读命令是否为所述模式寄存器读命令;

94.步骤5013,若是,则输出所述模式寄存器读命令;

95.步骤5014,反之,则生成阵列区数据读命令;

96.步骤507,响应所述阵列区数据读命令从存储单元阵列中读出阵列区数据。

97.具体地,请继续参考图14,通过对接收的读命令解码并判断所述读命令是否为所述模式寄存器读命令;若是,则输出所述模式寄存器读命令;反之,则生成阵列区数据读命令;然后响应所述阵列区数据读命令从存储单元阵列中读出阵列区数据,基于模式寄存器数据处理单元响应所述模式寄存器读命令从模式寄存器读出设置参数,并响应延迟读命令

并输出所述设置参数,其中,所述延迟读命令为延迟模块自接收模式寄存器读命令时刻起,延迟第一预设时间后生成;使得响应模式寄存器读命令读出设置参数的时间,与响应阵列区数据读命令读出阵列区数据的时间匹配,实现响应模式寄存器读命令读出设置参数的传输路径,与响应阵列区数据读命令读出阵列区数据的传输路径共用一数据发送通道,减小数据传输电路占用面积,以便于进一步提高半导体存储装置的集成度。

98.关于上述实施例中的数据传输方法的具体限定可以参见上文中对于数据传输装置的限定,在此不再赘述。

99.应该理解的是,虽然图12-图14的流程图中的各个步骤按照箭头的指示依次显示,但是这些步骤并不是必然按照箭头指示的顺序依次执行。除非本文中有明确的说明,这些步骤的执行并没有严格的顺序限制,这些步骤可以以其它的顺序执行。而且,图12-图14中的至少一部分步骤可以包括多个步骤或者多个阶段,这些步骤或者阶段并不必然是在同一时刻执行完成,而是可以在不同的时刻执行,这些步骤或者阶段的执行顺序也不必然是依次进行,而是可以与其它步骤或者其它步骤中的步骤或者阶段的至少一部分轮流或者交替地执行。

100.本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,是可以通过计算机程序来指令相关的硬件来完成,所述的计算机程序可存储于一非易失性计算机可读取存储介质中,该计算机程序在执行时,可包括如上述各方法的实施例的流程。其中,本技术所提供的各实施例中所使用的对存储器、存储、数据库或其它介质的任何引用,均可包括非易失性和/或易失性存储器。非易失性存储器可包括只读存储器(rom)、可编程rom(prom)、电可编程rom(eprom)、电可擦除可编程rom(eeprom)或闪存。易失性存储器可包括随机存取存储器(ram)或者外部高速缓冲存储器。作为说明而非局限,ram以多种形式可得,诸如静态ram(sram)、动态ram(dram)、同步dram(sdram)、双数据率sdram(ddrsdram)、增强型sdram(esdram)、同步链路(synchlink)dram(sldram)、存储器总线(rambus)直接ram(rdram)、直接存储器总线动态ram(drdram)、以及存储器总线动态ram(rdram)等。

101.请注意,上述实施例仅出于说明性目的而不意味对本发明的限制。

102.上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

103.以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对申请专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1