一种调整感测电流的电路及其内存组件的制作方法

1.本实用新型涉及一种电子电路,且特别是涉及一种调整感测电流的电路。

背景技术:

2.半导体内存组件的最新发展是有关于将半导体技术与磁性材料及组件相结合的自旋电子学(spin electronics)。电子的自旋极化可用于指示「1」或「0」的状态。一个此种自旋电子组件是自旋矩转移(spin torque transfer,stt)磁性穿隧接面(magnetic tunneling junction,mtj)组件。磁阻式随机存取内存 (magneto-resistive random access memory,mram)是使用mtj组件储存数据的非挥发性随机存取内存技术。在mram胞元中,可变的磁化层可相对于永久磁化层在两个位向上被磁化,进而提供明显不同的串联电阻。磁性层的平行对准状态具有相对低的电阻,而磁性层的反平行对准状态具有相对高的电阻。

3.须注意的是,“先前技术”段落的内容是用来帮助了解本实用新型。在“先前技术”段落所揭露的部份内容(或全部内容)可能不是所属技术领域中具有通常知识者所知道的习知技术。在“先前技术”段落所揭露的内容,不代表该内容在本实用新型申请前已被所属技术领域中具有通常知识者所知悉。

技术实现要素:

4.本实用新型提供一种调整感测电流的电路及内存组件。

5.本实用新型的一些实施例提供一种调整感测电流的电路,电路包括感测放大器、第一箝位电路、第二箝位电路及回馈电路。第一箝位电路包括并联耦接于感测放大器与内存阵列之间的多个第一箝位分支。第二箝位电路包括并联耦接于感测放大器与参考阵列之间的多个第二箝位分支。回馈电路被配置成因应于由感测放大器输出的输出数据而选择性地对一或多个第一箝位分支中或一或多个第二箝位分支进行启用或禁用。

6.本实用新型的一些实施例提供一种电路中的内存组件,所述内存组件包括:内存阵列;参考阵列;第一箝位电路,耦接至内存阵列;第二箝位电路,耦接至参考阵列;感测放大器,被配置成因应于流经所述第一箝位电路的胞元电流及流经第二箝位电路的参考电流而输出一输出数据;以及回馈电路,被配置成因应于输出数据而对胞元电流或参考电流进行调整。

7.为让本实用新型的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

8.包含随附图式以提供对本实用新型的进一步理解,且随附图式并入本说明书中且构成本说明书的一部分。图式说明本实用新型的实施例,且与描述一起用于解释本实用新型的原理。

9.结合附图阅读以下详细说明,会最佳地理解本揭露的各个态样。应注意,根据本行业中的标准惯例,各种特征并非按比例绘制。事实上,为使论述清晰起见,可任意增大或减小各种特征的大小。

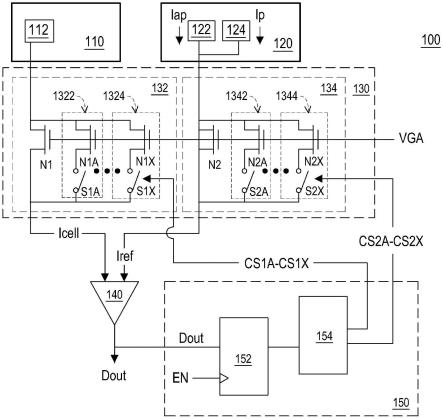

10.图1是示出根据本实用新型一些实施例的示例性内存组件的图。

11.图2是示出根据本实用新型一些实施例的表示经训练神经网络权重的数据的示例性分布的图。

12.图3是示出根据本实用新型一些实施例的表示经训练神经网络权重的数据的另一示例性分布的图。

13.图4是根据本实用新型一些实施例的对内存组件的感测电流进行调整的方法的示例性流程图。

14.附图标记说明

15.100:内存组件

16.110:内存阵列

17.112:记忆胞元

18.120:参考阵列

19.122、124:参考胞元

20.130:感测电路

21.132、134:箝位电路

22.140:感测放大器

23.150:回馈电路

24.152:锁存电路

25.154:调整电路

26.200、300:分布

27.210、220、230、240、250、260、270:线

28.400:方法

29.410、420、430:操作

30.1322、1324、1342、1344:箝位分支

31.cs1a~cs1x、cs2a~cs2x:控制信号

32.d1[1]、d1[1]、d1[3:0]、d2[3:0]、d3[3:0]、w[2:0]、w[3:0]:数据

[0033]

d[3]:数据值

[0034]

d[n]、d[n+1]、w[0]:位

[0035]

dout:输出信号/输出数据

[0036]

en:启动信号

[0037]

iap、ip:电流

[0038]

icell:胞元电流

[0039]

iref:参考电流

[0040]

m[0]、m[1]、m[2]、m[3]、m[3:0]、m[n]、m[n:0]、m[n+1]:预设预测值

[0041]

n1、n1a~n1x、n2、n2a~n2x:箝位组件

[0042]

p[0]、p[1]、p[2]、p[3]、p[n]、p[n:0]:预测值

[0043]

p[n+1]:先前数据位

[0044]

s1a~s1x、s2a~s2x:开关组件

[0045]

vga:栅极偏压

[0046]

w[1]:后续位/位

[0047]

w[2]:最高有效位(msb)/位

具体实施方式

[0048]

以下揭露提供用于实施所提供目标的不同特征的许多不同的示例性实施例或实例。以下阐述组件及排列的具体简化实例以阐释本实用新型。当然,该些仅为实例且不旨在进行限制。举例而言,以下说明中将第一特征形成于第二特征之上或第二特征上可包括其中第一特征与第二特征被形成为直接接触的实施例,且亦可包括其中第一特征与第二特征之间可形成有附加特征进而使得所述第一特征与所述第二特征可不直接接触的实施例。另外,本实用新型可能在各种实例中重复使用参考编号及/或字母。此种重复使用是出于简洁及清晰的目的,而不是自身指示所论述的各种实施例及/或配置之间的关系。

[0049]

本说明书中使用的用语一般而言具有其在此项技术中以及在其中使用每一用语的特定上下文中的普通含义。本说明书中的实例(包括本文中论述的任何用语的实例)的使用仅为例示性的,且决非限制本实用新型或任何示例性用语的范围及含义。同样,本实用新型并不限于本说明书中给出的各种实施例。

[0050]

尽管用语「第一」、「第二」等可在本文中用来阐述各种组件,但该些组件不应被该些用语所限制。该些用语用于区分一个组件与另一组件。举例而言,在不背离实施例的范围的条件下,第一组件可被称为第二组件,且类似地,第二组件可被称为第一组件。如本文中所使用,用语「及/或」包括相关联列出项中的一或多个项的任何及所有组合。

[0051]

此外,为易于说明,本文中可能使用例如「位于

…

之下(beneath)」、「位于

…

下方(below)」、「下部的(lower)」、「位于

…

上方(above)」、「上部的(upper)」等空间相对性用语来阐述图中所示的一个组件或特征与另一(其他)组件或特征的关系。所述空间相对性用语旨在除图中所绘示的定向外亦囊括组件在使用或操作中的不同定向。设备可具有其他定向(旋转 90度或处于其他定向),且本文中所使用的空间相对性描述语可同样相应地进行解释。

[0052]

在本文件中,用语「耦接」亦可被称为「电性耦接」,且用语「连接」可被称为「电性连接」。「耦接」及「连接」亦可用于指示二或更多个组件相互合作或相互作用。

[0053]

将针对特定上下文中的实施例(即磁性随机存取内存(magneticrandom-access memory,mram))来阐述本实用新型的各种实施例。然而,本实用新型中的概念亦可应用于其他内存组件或内存技术。对于mram内存,所述两个逻辑状态(即逻辑1与逻辑0)之间的胞元电流分离(cell currentseparation)预计为微安(培)(μa)或小于微安(培)的量级(order)。感测电流被置于与逻辑1状态相关联的第一读取电流值和与逻辑0状态相关联的第二读取电流值之间。

[0054]

图1是示出根据本实用新型一些实施例的示例性内存组件100的图。在一些实施例中,内存组件100可为磁性随机存取内存(mram)。举例而言,内存组件100包括:mram内存阵列110,具有mram记忆胞元112;参考阵列120,具有参考胞元122、124;感测电路130,包括箝

位电路132、134;感测放大器140,被配置成根据自所选择的记忆胞元112经由箝位电路132 流动的胞元电流icell以及自参考阵列120经由箝位电路134流动的参考电流 iref而输出一输出数据dout。内存组件100亦包括回馈电路150,回馈电路 150耦接于感测放大器140与感测电路130之间,且被配置成对流经感测电路130的参考电流iref或胞元电流icell进行微调。

[0055]

端视记忆胞元112是被配置成具有高逻辑状态亦或低逻辑状态的数据而定,内存阵列110中的mram记忆胞元112中的任一者可在低电阻状态与高电阻状态之间切换。举例而言,一个记忆胞元112可被写入至表示逻辑1的平行mram状态(p),或者被写入至表示逻辑0的反平行mram状态(ap)。胞元电流icell表示以高电阻状态或低电阻状态储存数据的对应的记忆胞元112的电阻,且可藉由向记忆胞元112施加预定电压而产生。由于制程的变异,因此内存阵列110中的各个mram胞元112可能具有不同的高电阻值及不同的低电阻值。此种制程变异可能导致不同逻辑状态的电阻值的微小差异,或者甚至重迭,此可能导致读取误差。

[0056]

如图1中所示,参考阵列120可包括被写入至反平行mram状态(ap) 的一或多个低逻辑状态(「0」)参考胞元122及被写入至平行mram状态 (p)的一或多个高逻辑状态(「1」)参考胞元124。在一些实施例中,参考阵列120中的参考胞元中的一半被写入至平行mram状态(p),且参考胞元中的一半被写入至反平行mram状态(ap),以获得(ip+iap)/2的平均参考电流iref,其中ip及iap分别是p状态及ap状态的平均电流值。类似地,可藉由向参考阵列120中的低逻辑状态参考胞元122及高逻辑状态参考胞元124施加与被施加至记忆胞元112相同的预定电压来产生参考电流 iref。

[0057]

一般而言,感测放大器140被配置成藉由对来自记忆胞元112的胞元电流icell与自参考阵列120处所获得的参考电流iref进行比较来确定储存于记忆胞元112中的数据的二进制逻辑状态。因此,感测放大器140可在感测放大器140的输出节点处提供输出信号dout,输出信号dout指示储存于所选择的mram记忆胞元112中的数据的逻辑低状态或逻辑高状态。

[0058]

在一些实施例中,感测电路130耦接于感测放大器140与内存阵列110 或参考阵列120之间。如图1中所示,感测电路130包括箝位电路132及134。箝位电路132电性耦接于感测放大器140与内存阵列110之间且被配置成在记忆体操作期间定义位线(bit line,bl)读取电压。类似地,箝位电路134 电性耦接于感测放大器140与参考阵列120之间,以在记忆体操作期间定义参考位线读取电压。

[0059]

在一些实施例中,感测比例可以改变以补偿参考电流iref或胞元电流 icell。举例而言,假设与第一逻辑状态相关联的第一电流(例如,电流iap) 及与第二逻辑状态相关联的第二电流(例如,电流ip)的目标值分别是10微安及30微安,目标参考电流电平可为10微安与30微安之间的平均值(即, 20微安)。因此,胞元电流icell可被确定为高于或低于此目标参考电流电平。感测比例通常可为2:1,使得0.5的权重因子被应用于感测放大器140的一个输入(例如,参考电流iref是第一电流iap与第二电流ip之和除以2,即平均参考电流)。

[0060]

然而,藉由改变感测比例,可根据基于工作负载分析的预测结果来对参考电流iref进行调整,以为高机率逻辑状态提供更大的感测裕度。在一些实施例中,可根据预测结果来预定义参考电流iref的调整量(例如,偏移值)。因此,可对用于读取储存于记忆胞元中的数据的临界点进行调谐,以扩大及保持高机率逻辑状态的感测裕度。因此,可降低读取误

差率。

[0061]

举例而言,若根据预测结果,后续位更可能是逻辑1,则感测电路130 可对感测比例进行调整以降低参考电流iref(例如,藉由将感测比例设定成5: 2而非2:1)。另一方面,若根据预测结果,后续位更可能是逻辑0,则感测电路130可对感测比例进行调整以增大参考电流iref(例如,藉由将感测比例设定成5:3而非2:1),进而确保改善的感测功能及更大的感测裕度。在一些实施例中,可针对内存组件100中的所有感测放大器140(或者基于每i/o组件(例如,针对与特定i/o组件相关联的感测放大器140))对感测比例进行全局调整。

[0062]

在一些实施例中,mram记忆胞元112及逻辑状态参考胞元122、124 可为磁性穿隧接面(magnetic tunnel junction,mtj)胞元。mtj胞元包括固定磁性层、薄介电穿隧障壁及自由磁性层。当自由层的磁矩平行于固定层时, mtj胞元具有低电阻。当自由层磁矩反向平行于固定层磁矩定向时,mtj胞元具有高电阻。mtj胞元的架构使得能够使用自旋矩转移(stt)来切换自由磁性层的磁化。

[0063]

在一些实施例中,自由磁性层的磁矩最初被假设为反平行于固定磁性层。可从自由磁性层朝向固定磁性层供应电流,以将自由磁性层的磁化状态切换成平行于固定磁性层的磁化状态。当电流从自由磁性层流被驱动至固定磁性层时,传导电子自固定磁性层向自由磁性层移动。自固定磁性层移动进的大多数传导电子具有在与固定磁性层的磁矩相同的方向上极化的自旋。该些电子与靠近自由磁性层和薄介电穿隧障壁之间的接口的自由磁性层的磁矩相互作用。由于相互作用,电子转移其自旋角动量,此与自由磁性层的磁化反平行。当足够的角动量被转移时,自由磁性层的磁化状态被切换成平行于固定磁性层的磁化状态。因此,记忆胞元112被写入至平行mram状态(p)。

[0064]

作为另一种选择,可自相反的方向(自固定磁性层至自由磁性层)供应电流,以将自由磁性层的磁化状态切换成反平行于固定磁性层的磁化状态。当电流自固定磁性层被驱动至自由磁性层时,传导电子在相反的方向上移动,其中大多数传导电子具有在自由磁性层的磁化的方向(例如,与固定磁性层相同的方向)上极化的自旋。大多数传导电子藉由固定磁性层传输。然而,少数传导电子具有反平行于自由磁性层及固定磁性层的磁化状态而极化的自旋。该些电子自固定磁性层散射回来且在返回自由磁性层的移动过程时与自由磁性层的磁矩相互作用。当足够充分的角动量被转移至自由磁性层时,自由磁性层的磁化状态被切换成反平行于固定磁性层的磁化状态。因此,记忆胞元112被写入至反平行mram状态(ap)。应理解,自旋矩转移的上述说明是示例性的且并非意味着限制本实用新型的范围。

[0065]

所述两个磁性层之间的薄介电穿隧障壁足够薄以使得电子能够穿隧。在一些实施例中,薄介电穿隧障壁具有非磁性组成物且可由可作为电性绝缘体的任何合适的材料形成。在一些实施例中,薄介电穿隧障壁包含氧化铝。在一些其他替代实施例中,薄介电穿隧障壁包含mgo。可包括于薄介电穿隧障壁中的其它介电材料的实例包括al、mg、si、hf、sr或ti的氧化物或氮化物,例如siox、sinx、sioxny、alox、tox、tiox、alnx或其任意组合。薄介电穿隧障壁可藉由例如以下各种制程形成:微影、化学气相沈积(chemicalvapor deposition,cvd)、电浆增强型化学气相沈积(plasma enhanced chemicalvapor deposition,pecvd)、物理气相沈积(physical vapor deposition,pvd)、电化学沈积、分子操纵、氧化、蚀刻、化学机械研磨及/或其他合适的制程。在一些实施例中,薄介电穿隧障壁可独立地或与插入固定磁性层和自由磁性层的其他层相结合,将固定磁性层与自由磁性层

电性绝缘。

[0066]

在一些实施例中,固定磁性层及自由磁性层是铁磁层。固定磁性层及自由磁性层可包含co、fe、ni、mn、b及/或其合金(包括例如nife、cofe、 cofeb或其化合物),包括其他铁磁材料。固定磁性层及/或自由磁性层可藉由例如以下各种制程形成:微影、化学气相沈积(cvd)、物理气相沈积(pvd)、电化学沈积、分子操纵、蚀刻、化学机械研磨及/或其它制程。

[0067]

如图1中所示,箝位电路132包括:箝位组件(clamp device)n1,耦接于内存阵列110与感测放大器140之间;以及多个可选的箝位分支1322与1324,彼此并联耦接。具体而言,可选的箝位分支1322及1324包括箝位组件n1a至n1x,箝位组件n1a至n1x可由对应的控制信号独立地开启或关断,以对用于感测放大器140的胞元电流icell进行调整,进而达成感测放大器预微调且对感测比例进行调整。

[0068]

举例而言,箝位分支1322包括串联耦接的箝位组件n1a(例如,晶体管) 与开关组件s1a。类似地,箝位分支1324包括串联耦接的箝位组件n1x(例如,晶体管)与开关组件s1x。因此,开关组件s1a、s1x的相应状态会决定是否使用可选的箝位组件n1a及n1x。可使用此种箝位组件的各种数目以按照各种方式调整相应的电流。举例而言,藉由关闭对应的开关组件以对该些箝位组件中的一者进行启用,流经箝位电路132的胞元电流icell增大。另一方面,藉由打开对应的开关组件以对该些箝位组件中的一者进行禁用,流经箝位电路132的胞元电流icell减小。

[0069]

类似地,箝位电路134包括:箝位组件n2,耦接于参考阵列120与感测放大器140之间;以及多个可选的箝位分支1342与1344,彼此并联耦接。箝位分支1342及1344包括箝位组件n2a至n2x,箝位组件n2a至n2x亦可由对应的控制信号接通或关断,以达成感测放大器预微调且对感测比例进行调整。

[0070]

举例而言,箝位分支1342包括串联耦接的箝位组件n2a(例如,晶体管) 与开关组件s2a。类似地,箝位分支1344包括串联耦接的箝位组件n2x(例如,晶体管)与开关组件s2x。因此,开关组件s2a、s2x的相应状态会决定是否使用可选的箝位组件n2a及n2x。藉由闭合对应的开关组件以对该些箝位组件中的一者进行启用,流经箝位电路134的参考电流iref增大。另一方面,藉由打开对应的开关组件以对该些箝位组件中的一者进行禁用,流经箝位电路134的参考电流iref减小。在一些实施例中,箝位组件n1a至n1x 的栅极与n2a至n2x的栅极彼此耦接且由栅极偏压(gate bias)vga控制。在一些实施例中,栅极偏压vga可由芯片上模拟电路(on-chip analog circuit) (未示出)产生。

[0071]

在一些实施例中,相应晶体管的宽度可决定在每一晶体管的源极端子与漏极端子之间传导的电流的摆幅。被启用的可选的箝位分支的不同数目或箝位分支中的该些晶体管的不同宽度可用于提供对参考电流iref及胞元电流icell进行控制的各种选项。由于箝位分支中的晶体管可为任何大小,因此可达成分子与分母的任意组合,且因此达成任意感测比例。另外,应理解,实施例并不限于箝位电路132及134中的两个箝位分支。在各种实施例中,箝位电路132及134中的任意者可包括任何数目的箝位分支。

[0072]

图2是示出根据本实用新型一些实施例的表示经训练的神经网络权重的数据w[2:0]的示例性分布200的图。在一些实施例中,储存于内存中的经训练的神经网络权重常常具有非均匀分布(例如高斯分布(gaussiandistribution)或类高斯分布)。举例而言,图2中所示的分布200可为以2 补码表示来表示3位权重数据w[2:0]的以0为中心的高斯分布。三

位数的2 补码可用来表示自-4至3的带正负号整数。具体而言,以2补码形式表示十进制值4至3的二进制数是100、101、110、111、000、001、010、011,其中非负数由普通二进制表示来表示,且其2补码(可藉由将位反转(invert) 且加一来计算)对逆负数进行编码。

[0073]

在经训练的神经网络权重的高斯分布或类高斯分布的情况下,2补码表示会保证不对称的数据机率。举例而言,当读取数据的最高有效位(mostsignificant bit,msb)w[2]时,如图2中的线210所示,位w[2]为1的机率实质上等于位w[2]为0的机率。当读取数据的后续位w[1]时,位w[1]为1 的机率与位w[1]为0的机率根据位w[2]的值而不同。当位w[2]为1时,如图2中的线220所示,位w[1]为1的机率大于位w[1]为0的机率。当位w[2] 为0时,如图2中的线230所示,位w[1]为1的机率小于位w[1]为0的机率。

[0074]

类似地,当位w[2]为1时,如图2中的线240及250所示,位w[0]为1 的机率大于位w[0]为0的机率。当位w[2]为0时,如图2中的线260及线 270所示,位w[0]为1的机率小于位w[0]为0的机率。因此,可根据最高有效位w[2]来预测后续位w[1]及w[0]。

[0075]

图3是示出根据本实用新型一些实施例的表示经训练的神经网络权重的数据w[3:0]的另一示例性分布300的图。与图2相比,图3中所示的分布 300可为以2补码表示来表示4位权重分布的非以0为中心的分布。对于非以0为中心的分布,可自最高有效位(msb)数据至最低有效位(least significantbit,lsb)数据获得储存位d[n]的预测值p[n]。在一些实施例中,可根据对应于分布峰值的预设预测值m[n]以及先前数据位p[n+1]的预测精度来确定预测值p[n]。

[0076]

举例而言,参照图3所示的示例性分布300,分布峰值出现于值1100处,值1100被定义为预设预测值m[3:0]。对于最高有效位,默认预测值m[3] 被用作预测值p[3]。对于数据的后续位,若先前的预测是正确的,则预设预测值m[n]继续用作预测值p[n],直至出现不正确的预测。换言之,当实际数据值d[3]等于预测值p[3]时,预设预测值m[2]被用作预测值p[2]。可重复实行上述过程。当对于位d[n+1]出现不正确的预测时,预设预测值m[n+1]被用作所有后续位的预测值p[n:0]。

[0077]

在一些实施例中,在对数据进行训练之后,可以统计方式决定每一位的默认预测值m[n:0]。另外,在一些实施例中,当数据具有高分布(例如,紧密聚集的数据更接近中间值)时,数据预测的成功率可能相对高,而当数据具有低分布(例如,分散的数据)时,数据预测的成功率可能相对低。

[0078]

举例而言,若预设预测值m[3:0]是1100(基于图3中的示例性分布300 具有最高机率的值),且储存的实际数据d1[3:0]是1000(其为具有低机率的值),则首先基于预设预测值m[3](即,1)获得msb数据的预测值p[3]。由于预测是正确的(p[3]=1且d1[3]=1),因此亦基于预设预测值m[2](即, 1)获得之后的位的预测值p[2]。然而,第一次的预测是不正确的(p[2]=1且 d1[2]=0),因此预设预测值m[2](即,1)被分派给剩余位的预测值p[1] 及p[0]。以上预测是朝着更高的机率实施,但在此实例中,实际数据d1[1] 及d1[0]的两个预测均为不正确的。

[0079]

在另一实例中,若储存的实际数据d2[3:0]是1110(其为基于图3中的示例性分布300具有中等机率的值),则首先基于预设预测值m[3](即,1) 获得msb数据的预测值p[3]。由于预测是正确的(p[3]=1且d2[3]=1),因此亦可基于预设预测值m[2](即,1)获得之后的位的预测值p[2]。由于预测是正确的(p[2]=1且d2[2]=1),因此亦基于预设预测值m1.(即,0)获得之后的位的预测值p[1]。然而,第一次的预测是不正确的(p[1]=0且 d2[2]=1),因此预设预测值m[1](即,0)被分派给预测值p[0]。

[0080]

在又一实例中,若储存的实际数据d3[3:0]是1101(其为基于图3中的示例性分布300具有高机率的值),则首先基于预设预测值m[3](即,1) 获得msb数据的预测值p[3]。由于预测是正确的(p[3]=1且d3[3]=1),因此亦基于预设预测值m[2](即,1)获得之后的位的预测值p[2]。预测亦是正确的(p[2]=1且d3[2]=1),且基于预设预测值m[1](即,0)再次获得之后的位的预测值p[1]。预测亦是正确的(p[1]=0且d3[1]=0),且基于预设预测值m[0](即,0)再次获得之后的位的预测值p[0]。

[0081]

如以上实例中所示,对于储存于内存中的经训练的神经网络权重,由于数据分布可藉由以统计方式评估神经网络模型及在训练中使用的数据集而获得,因此内存组件100可使用最高有效位值作为基于数据机率来预测后续位的指针。

[0082]

再次参照图1,当内存组件100预测之后的位为逻辑1时,回馈电路150 可向感测电路130输出对应的控制信号cs1a至cs1x及cs2a至cs2x,以增大参考电流iref,或者作为另一种选择,降低胞元电流icell,以提供更大的感测裕度。另一方面,当内存组件100预测之后的位为逻辑0时,回馈电路150可向感测电路130输出对应的控制信号cs1a至cs1x及cs2a至 cs2x,以降低参考电流iref,或者作为另一种选择,增大胞元电流icell,以提供更大的感测裕度。

[0083]

举例而言,回馈电路150可输出控制信号cs1a至cs1x及cs2a至 cs2x,以因应于由感测放大器140输出的输出数据dout而选择性地对一或多个箝位分支1322、1324或者一或多个箝位分支1342、1344进行启用或禁用,以对胞元电流icell或参考电流iref进行调整。在图1所示实施例中,回馈电路150包括锁存电路152及电性耦接至锁存电路152的调整电路154。锁存电路152被配置成接收输出数据dout及启动信号en(此可由内存组件 100中的独立电路(未示出)产生)。在一些实施例中,若欲读取的数据是最高有效位(msb),则触发启动信号en。启动信号en可自内存控制器提供。当启动信号en被启用时,回馈电路150被启用且被配置成根据输出数据dout分别向箝位电路132、134输出控制信号cs1a至cs1x、cs2a至 cs2x。在一些实施例中,启动信号en是在输出数据dout是最高有效位 (msb)数据时被启用,以触发对参考电流iref或胞元电流icell的微调。注意,在一些其他实施例中,启动信号en亦可在输出数据dout不是最高有效位(msb)数据时被启用。举例而言,启动信号en亦可在输出数据dout是msb-n位时被启用。因此,在各种实施例中,内存组件100可基于工作负荷分析使用后面的位来预测前面的位或使用前面的位来预测后面的位(工作负荷分析包括但不限于与在神经网络训练中使用的模型及数据集相关联的数据分布),且因应于启动信号en而根据锁存的输出数据dout对胞元电流icell 或参考电流iref进行调整,以有利于后续位的相对高机率状态。

[0084]

在一些实施例中,因应于msb输出数据dout为逻辑1,调整电路154 被配置成藉由使用控制信号cs2a至cs2x对一或多个箝位分支1342、1344 进行禁用来降低流经箝位电路134的参考电流iref。因应于msb输出数据 dout为逻辑0,调整电路154被配置成藉由使用控制信号cs2a至cs2x对一或多个箝位分支1342、1344进行启用来增大流经箝位电路134的参考电流 iref。换言之,调整电路154被配置成基于msb输出数据dout的逻辑值来实行参考侧调整以提供更大的感测裕度。

[0085]

在一些其他实施例中,调整电路154亦可被配置成基于msb输出数据 dout的逻辑值来实行胞元侧调整以提供更大的感测裕度。当调整电路154实行胞元侧调整时,因应于msb输出数据dout为逻辑1,调整电路154被配置成藉由使用控制信号cs1a至cs1x对一或多个箝位分支1322、1324进行启用来增大流经箝位电路132的胞元电流icell。因应于msb输出数据dout 为逻辑0,调整电路154被配置成藉由使用控制信号cs1a至cs1x对一或多个箝位分支1322、1324进行禁用来降低流经箝位电路132的胞元电流icell。

[0086]

在一些其他实施例中,调整电路154亦可被配置成藉由由利用控制信号 cs1a至cs1x、cs2a至cs2x对箝位电路132中的m个箝位分支及箝位电路134中的n个箝位分支进行启用来实行胞元侧的调整及参考侧的调整,其中m及n是整数。因应于输出数据dout为逻辑1,调整电路154输出控制信号cs1a至cs1x、cs2a至cs2x以使m大于n,以相对于参考电流iref相对增大胞元电流icell。举例而言,调整电路154可对箝位电路132中的两个箝位分支1322及1324以及箝位电路134中的仅一个箝位分支1342进行启用。

[0087]

因应于输出数据dout为逻辑0,调整电路154输出控制信号cs1a至 cs1x、cs2a至cs2x以使m小于n,以相对于参考电流iref相对降低胞元电流icell。举例而言,调整电路154可对箝位电路132中的仅一个箝位分支 1322以及箝位电路134中的两个箝位分支1342及1344进行启用。

[0088]

如图1中所示,箝位电路132中的箝位分支1322、1324或箝位电路134 中的箝位分支1342、1344中的任意者可包括以串联方式电性耦接的对应的箝位组件(例如,箝位组件n1a至n1x、n2a至n2x)与对应的开关组件(例如,开关组件s1a至s1x、s2a至s2x)。箝位组件n1a至n1x、n2a至 n2x由栅极偏压vga控制,且开关组件s1a至s1x、s2a至s2x由回馈电路150控制。回馈电路150可藉由对应的控制信号cs1a至cs1x、cs2a至 cs2x单独地接通或关断开关组件s1a至s1x、s2a至s2x,以对与对应的开关组件s1a至s1x、s2a至s2x相关联的电流箝位分支1322、1324、1342、 1344进行启用或禁用。

[0089]

图4是根据本实用新型一些实施例的对内存组件的感测电流进行调整的方法400的示例性流程图。应理解,可在图4中绘示的方法400之前、期间及/或之后实行附加的操作,且可仅在本文中简要阐述一些其他操作。可对图 1至图3所示实施例中所示的内存组件100实行方法400,但本实用新型并不限于此。

[0090]

在操作410中,感测放大器(例如,图1中的感测放大器140)因应于自内存阵列(例如,图1中的内存阵列110)的位线感测的胞元电流(例如,图1中的胞元电流icell)以及参考电流(例如,图1中的参考电流iref)而输出一输出数据dout。

[0091]

在操作420中,回馈电路(例如,图1中的回馈电路150)判断输出数据是否是最高有效位(msb)数据。举例而言,回馈电路中的锁存电路可接收启动信号(例如,图1中的锁存电路152接收启动信号en)。在一些实施例中,在操作420中,锁存电路的启动信号是因应于输出数据是msb数据而被启用。

[0092]

在操作430中,回馈电路因应于由感测放大器输出的最高有效位数据而对参考电流或胞元电流进行调整。在一些实施例中,回馈电路150中的锁存电路152接收输出数据dout。当启动信号被启用时,回馈电路中的调整电路 (例如,图1中的调整电路154)因应于输出数据而选择性地对与胞元电流相关联的第一箝位电路(例如,图1中的箝位电路132)中的一或多个第一箝位分支(例如,图1中的箝位分支1322及1324)或者与参考电流相关联的

第二箝位电路(例如,图1中的箝位电路134)中的一或多个第二箝位分支(例如,图1中的箝位分支1342及1344)进行启用或禁用。

[0093]

在一些实施例中,操作430中的对参考电流或胞元电流进行调整的步骤包括参考电流调整,以因应于输出数据为逻辑1而降低参考电流,且因应于输出数据为逻辑0而增大参考电流。在一些其他实施例中,操作430中的对参考电流或胞元电流进行调整的步骤包括胞元电流调整,以因应于输出数据为逻辑0而降低胞元电流且因应于输出数据为逻辑1而增大胞元电流。

[0094]

在一些实施例中,在操作430中,调整电路被配置成对m个第一箝位分支及n个第二箝位分支进行启用,其中m及n是整数。因应于输出数据为逻辑1,m大于n。因应于输出数据为逻辑0,m小于n。换言之,当msb输出数据为逻辑1时,与胞元电流相关联的被启用箝位分支的数目大于与参考电流相关联的被启用箝位分支的数目。当msb输出数据为逻辑0时,与胞元电流相关的被启用箝位分支的数目少于与参考电流相关的被启用箝位分支的数目。

[0095]

藉由上述操作,可因此实行用于对内存组件的感测电流进行调整的方法,以基于根据msb数据的数据预测来实行参考侧电流调整及/或胞元侧电流调整,以提供更大的感测裕度。因此,可减少读取误差,且可改善内存组件的精度及效率。

[0096]

应理解,尽管结合mram胞元(例如stt-mram胞元)来例示以上阐述的电路架构及方法,但本文中所阐述的方式可应用于读取其它类型的记忆胞元,其中制程变化可能导致逻辑高胞元特性与逻辑低胞元特性的分布中的微小差异,此意味着固定参考电流可能不是提供精确结果的理想感测临限值。同样,应理解,本实用新型并不限于用于stt-mram,而是亦可用于其他类型的mram。

[0097]

在一些实施例中,揭露一种电路,所述电路包括感测放大器、第一箝位电路、第二箝位电路及回馈电路。所述第一箝位电路包括并联耦接于所述感测放大器与内存阵列之间的多个第一箝位分支。所述第二箝位电路包括并联耦接于所述感测放大器与参考阵列之间的多个第二箝位分支。回馈电路被配置成因应于由所述感测放大器输出的输出数据而选择性地对一或多个第一箝位分支中或一或多个第二箝位分支进行启用或禁用。在一些实施例中,所述回馈电路包括:锁存电路,被配置成接收所述输出数据及启动信号;以及调整电路,被配置成当所述启动信号被启用时,根据所述输出数据向所述第一箝位电路及所述第二箝位电路输出多个控制信号。在一些实施例中,所述启动信号是在所述输出数据是最高有效位(msb)数据时被启用。在一些实施例中,所述调整电路被配置成藉由因应于所述输出数据为逻辑1而对所述多个第二箝位分支中的一或多者进行禁用来降低流经所述第二箝位电路的参考电流。在一些实施例中,所述调整电路被配置成藉由因应于所述输出数据为逻辑0而对所述多个第二箝位分支中的一或多者进行启用来增大流经所述第二箝位电路的参考电流。在一些实施例中,所述调整电路被配置成藉由因应于所述输出数据为逻辑1而对所述多个第一箝位分支中的一或多者进行启用来增加流经所述第一箝位电路的胞元电流。在一些实施例中,所述调整电路被配置成藉由因应于所述输出数据为逻辑0而对所述多个第一箝位分支中的一或多者进行禁用来降低流经所述第一箝位电路的胞元电流。在一些实施例中,所述调整电路被配置成藉由所述多个控制信号对m个第一箝位分支及n 个第二箝位分支进行启用,其中因应于所述输出数据为逻辑1,m大于n,且因应于所述输出数据为逻辑0,m小于n,m及n是整数。在一些实施例中,当所述输出数据是最高有效位数据时,所述回馈电路

被配置成因应于所述输出数据而对流经所述第二箝位电路的参考电流进行调整。在一些实施例中,其中当所述输出数据是最高有效位数据时,所述回馈电路被配置成因应于所述输出数据而对流经所述第一箝位电路的胞元电流进行调整。在一些实施例中,所述多个第一箝位分支或所述多个第二箝位分支中的一者包括:箝位组件,由栅极偏压控制;以及开关组件,串联耦接至所述箝位组件且由所述回馈电路控制。

[0098]

在一些实施例中,揭露一种对电路中的内存组件的感测电流进行调整的方法。所述方法包括:由感测放大器因应于自内存阵列的位线感测的胞元电流以及参考电流而输出一输出数据;判断所述输出数据是否是最高有效位数据;以及因应于由所述感测放大器输出的所述最高有效位数据而对所述参考电流或所述胞元电流进行调整。在一些实施例中,所述的方法更包括:因应于所述输出数据是所述最高有效位数据而将启动信号启用至锁存电路;由所述锁存电路接收所述输出数据;以及当所述启动信号被启用时,因应于所述输出数据,选择性地对与所述胞元电流相关联的第一箝位电路中的一或多个第一箝位分支或者与所述参考电流相关联的第二箝位电路中的一或多个第二箝位分支进行启用或禁用。在一些实施例中,所述的方法更包括:对m个第一箝位分支及n个第二箝位分支进行启用,其中因应于所述输出数据为逻辑 1,m大于n,且因应于所述输出数据为逻辑0,m小于n,m及n是整数。在一些实施例中,其中对所述参考电流或所述胞元电流进行调整包括:因应于所述输出数据为逻辑1而降低所述参考电流;以及因应于所述输出数据为逻辑0而增大所述参考电流。在一些实施例中,其中对所述参考电流或所述胞元电流进行调整包括:因应于所述输出数据为逻辑0而降低所述胞元电流;以及因应于所述输出数据为逻辑1而增大所述胞元电流。

[0099]

在一些实施例中,揭露一种电路中的内存组件,所述内存组件包括:内存阵列;参考阵列;第一箝位电路,耦接至所述内存阵列;第二箝位电路,耦接至所述参考阵列;感测放大器,被配置成因应于流经所述第一箝位电路的胞元电流及流经所述第二箝位电路的参考电流而输出一输出数据;以及回馈电路,被配置成因应于所述输出数据而对所述胞元电流或所述参考电流进行调整。在一些实施例中,所述回馈电路包括:锁存电路,被配置成接收所述输出数据及启动信号,所述启动信号是在所述输出数据是最高有效位 (msb)数据时被启用;以及调整电路,被配置成当所述启动信号被启用时,输出多个控制信号以根据所述输出数据选择性地对所述第一箝位电路中的一或多个箝位分支或所述第二箝位电路中的一或多个箝位分支进行启用或禁用。在一些实施例中,所述调整电路被配置成因应于所述输出数据为逻辑0 而增大所述参考电流或降低所述胞元电流。在一些实施例中,所述调整电路被配置成因应于所述输出数据为逻辑1而增加所述胞元电流或降低所述参考电流。

[0100]

最后应说明的是:以上各实施例仅用以说明本实用新型的技术方案,而非对其限制;尽管参照前述各实施例对本实用新型进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本实用新型各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1