记忆体装置及其操作方法以及记忆体系统与流程

本揭露的一实施例是关于一种记忆体装置,特别是关于一种包含位元线、第一可程序位元线、电荷共享电路以及放电电路的记忆体装置。

背景技术:

1、静态随机存取记忆体(static random access memory,sram)装置是一种挥发性半导体记忆体,使用不需要更新的双稳电路系统储存数据位元。sram装置通常包括一或多个记忆体阵列,其中各个阵列包括多个sram单元。sram单元通常称为位元格,因为其储存信息的一个位元,由两个交叉耦合反向器的逻辑状态表示。各个记忆体阵列包括配置成行与列的多个位元格。记忆体阵列中的各个位元格通常包括与电力供应电压及参考电压的连接。位元线上的逻辑信号控制自位元格读取及写入至位元格,而字元线控制位元线与反向器的连接,否则反向器会浮动。字元线可沿记忆体阵列的一行耦合至多个位元格,为不同的行提供不同的字元线。

技术实现思路

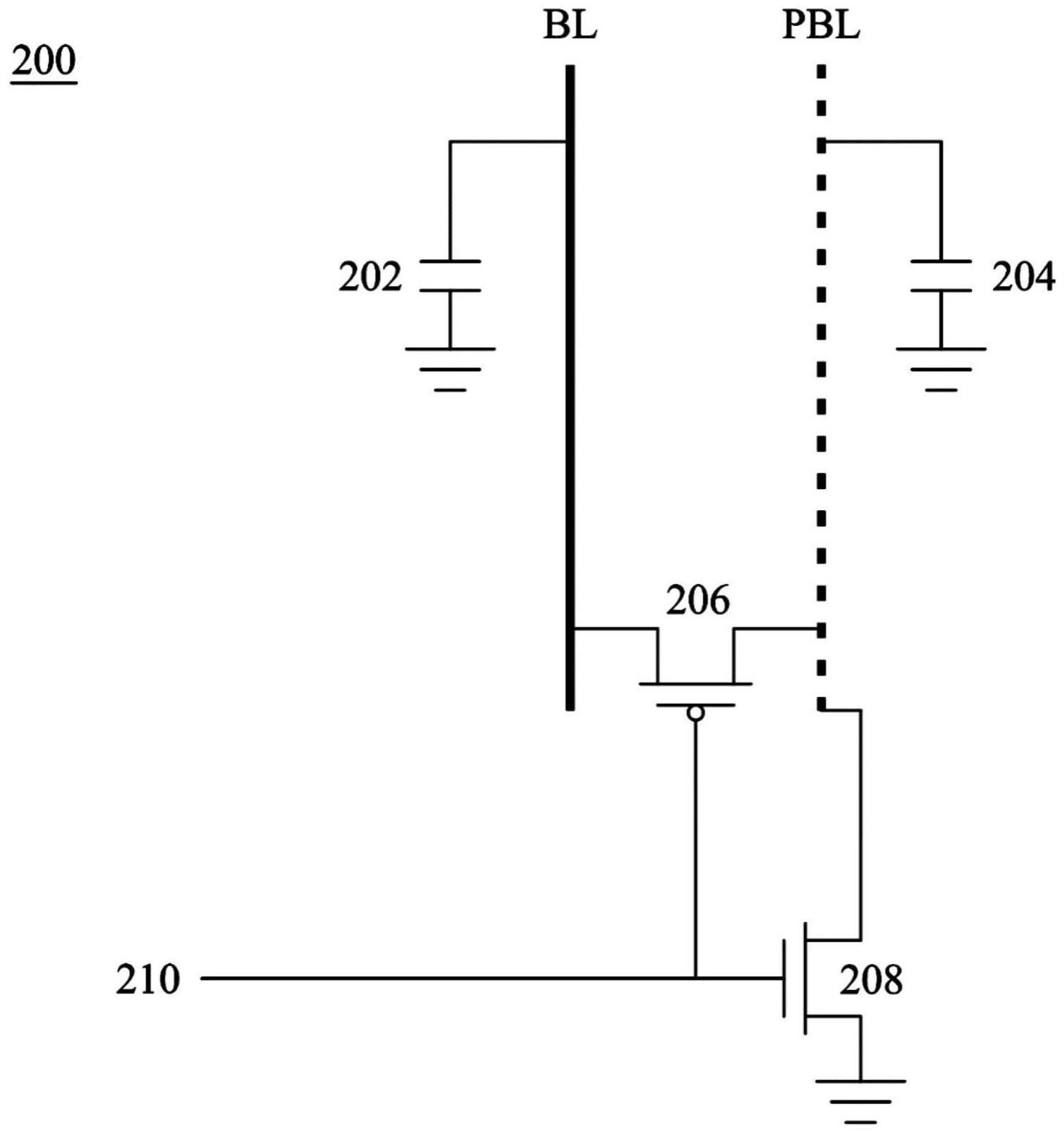

1、本揭露的一实施例提供一种记忆体装置,包含位元线、第一可程序位元线、电荷共享电路以及放电电路。位元线连接至记忆体阵列的多个记忆体单元,其中位元线具有第一长度。第一可程序位元线具有第二长度,第二长度是基于记忆体阵列的大小决定。电荷共享电路连接至位元线及第一可程序位元线,其中电荷共享电路用以将电荷自位元线转移至第一可程序位元线。放电电路连接至第一可程序位元线,其中放电电路用以对第一可程序位元线中的储存电荷放电。

2、本揭露的另一实施例提供一种记忆体系统,包含记忆体阵列、控制器以及可程序电荷共享电路。记忆体阵列包括具有第一长度的位元线。控制器用以提供控制信号至记忆体阵列。可程序电荷共享电路连接至控制器及位元线。可程序电荷共享电路包含具有基于记忆体阵列的大小决定的第二长度的第一可程序位元线、连接至位元线及第一可程序位元线的电荷共享电路以及连接至第一可程序位元线的放电电路。电荷共享电路用以将电荷自位元线转移至第一可程序位元线。放电电路用以对第一可程序位元线中的储存电荷放电。

3、本揭露的另一实施例提供一种操作记忆体装置的方法,方法包含以下步骤:在记忆体单元的读取操作期间,将第一电压提供至连接至放电电路及电荷共享电路的控制信号线;基于控制信号线上的第一电压,用放电电路对可程序位元线放电;将不同于第一电压的第二电压提供至控制信号线;及基于控制信号线上的第二电压将位元线连接至可程序位元线。

技术特征:

1.一种记忆体装置,其特征在于,其包含:

2.如权利要求1所述的记忆体装置,其特征在于,其中该位元线形成为一第一金属结构,且其中该第一可程序位元线形成为实质上平行于该第一金属结构的一第二金属结构。

3.如权利要求1所述的记忆体装置,其特征在于,其中该电荷共享电路包括并联连接的一p型晶体管及一n型晶体管,其中一第一控制信号连接至该p型晶体管,且其中自该第一控制信号反向的一第二控制信号连接至该n型晶体管。

4.如权利要求1所述的记忆体装置,其特征在于,进一步包含连接至该电荷共享电路的一栅极端子的多个反向器,其中一控制信号连接至所述多个反向器的输入及该放电电路的一栅极端子。

5.如权利要求4所述的记忆体装置,其特征在于,其中该电荷共享电路包括并联连接的一p型晶体管及一n型晶体管,且其中该n型晶体管的一栅极端子连接至一第一反向器的一输出及一第二反向器的一输入。

6.一种记忆体系统,其特征在于,其包含:

7.如权利要求6所述的记忆体系统,其特征在于,进一步包含用以追踪该位元线的一行为并提供一追踪信号至该控制器的一追踪电路,其中该控制器用以基于该追踪信号产生该控制信号。

8.如权利要求7所述的记忆体系统,其特征在于,进一步包含一预充电电路,用以基于来自该控制器的一预充电控制信号对该位元线预充电,其中该控制器包括一与非门,用以接收该追踪信号及该预充电控制信号作为输入并输出该控制信号。

9.一种操作一记忆体装置的方法,其特征在于,该方法包含以下步骤:

10.如权利要求9所述的方法,其特征在于,进一步包含以下步骤:在启动该电荷共享控制信号线之前对该位元线预充电。

技术总结

揭示一种记忆体装置及其操作方法以及记忆体系统。在一个态样中,记忆体装置包括连接至记忆体阵列的多个记忆体单元的位元线,位元线具有第一长度。记忆体装置包括具有基于记忆体阵列的大小决定的第二长度的第一可程序位元线,及连接至位元线及第一可程序位元线的电荷共享电路。电荷共享电路用以将电荷自位元线转移至第一可程序位元线。记忆体装置包括连接至第一可程序位元线的放电电路,放电电路用以对第一可程序位元线中的储存电荷放电。

技术研发人员:陈建源,李哲安,谢豪泰,李政宏

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!