一种3D存储装置、芯片、测试系统及测试方法与流程

本申请涉及电子,具体涉及一种3d存储装置、芯片、3d存储装置的测试系统及3d存储装置的测试方法。

背景技术:

1、三维集成电路(three-dimensional integrated circuits,3d ic)是将多颗芯片进行三维空间垂直整合,用于减小半导体芯片的尺寸。三维集成电路将不同的晶圆堆叠起来,形成的新芯片由多个晶圆(例如,存储晶圆、逻辑晶圆等)构成。利用三维集成电路可以制造高速处理器与大容量存储器,能够进一步提升电子产品性能。进行三维集成电路测试是为了提高预封装测试品质,以及在堆叠的晶圆之间进行测试。

2、然而,目前的三维集成电路不能根据实际情况对晶圆进行测试调整,不能获得对晶圆进行测试的过程中的具体情况,不能满足晶圆的测试需求,对于发现的问题难以定位。测试过程繁琐,测试的成本高。并且,不能提高三维集成电路的芯片良率。

技术实现思路

1、本申请提出一种3d存储装置、芯片、3d存储装置的测试系统及3d存储装置的测试方法,能够实现对存储晶圆、逻辑晶圆、存储晶圆与逻辑晶圆之间交互的测试,提高测试的灵活性及有效性,提高3d存储装置的良率。

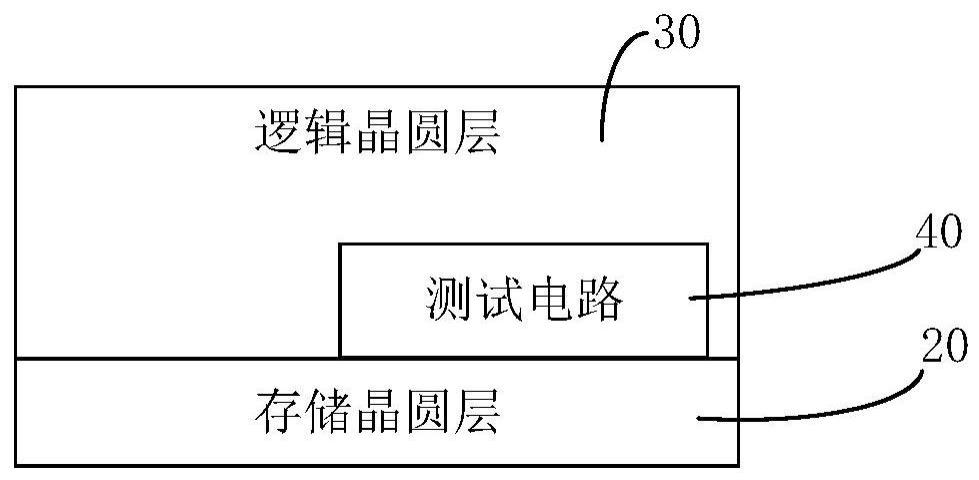

2、为解决上述技术问题,本申请采用的一个技术方案是:提供一种3d存储装置,该3d存储装置包括:存储晶圆层,用于存储数据,存储晶圆层设有第一测试点,第一测试点用于对存储晶圆层的存储晶圆进行测试;逻辑晶圆层,设置在存储晶圆层的一侧,且逻辑晶圆层中的逻辑晶圆与存储晶圆连接,用于对从存储晶圆读出的数据进行逻辑处理及对要存入存储晶圆的数据进行逻辑处理,逻辑晶圆层设有第二测试点及第三测试点,第二测试点用于对逻辑晶圆进行测试,第三测试点用于对存储晶圆与逻辑晶圆之间的交互进行测试;测试电路,设置在逻辑晶圆层,且分别与第一测试点、第二测试点及第三测试点连接,测试电路用于基于测试时序信号对存储晶圆、逻辑晶圆、存储晶圆与逻辑晶圆之间的交互进行测试。

3、其中,测试电路包括:通信接口电路,用于基于测试时序信号生成分别对存储晶圆进行测试的第一测试信号、对逻辑晶圆进行测试的第二测试信号、对存储晶圆与逻辑晶圆之间的交互进行测试的第三测试信号。

4、其中,测试电路还包括:第一测试支路,其第一端与第一测试点连接,其第二端连接通信接口电路,用于将第一测试信号传递给存储晶圆,以对存储晶圆进行测试;第二测试支路,其第一端与第二测试点连接,其第二端连接通信接口电路,用于将第二测试信号传递给逻辑晶圆,以对逻辑晶圆进行测试;第三测试支路,其第一端与第三测试点连接,其第二端连接通信接口电路,用于将第三测试信号传递给逻辑晶圆,以对存储晶圆与逻辑晶圆之间的交互进行测试;测试引脚,设置在逻辑晶圆层背离存储晶圆层的一侧上,且与通信接口电路连接,用于将通信接口电路引出至3d存储装置外。

5、其中,测试电路还包括:切换电路,分别与通信接口电路、第一测试点、第二测试点及第三测试点连接,用于基于切换信号依次将第一测试信号传递给存储晶圆、将第二测试信号传递给逻辑晶圆及将第三测试信号传递给逻辑晶圆。

6、其中,测试电路还包括:切换电路,分别与通信接口电路、第一测试点、第二测试点及第三测试点连接,用于基于测试异常结果依次将第一测试信号传递给存储晶圆、将第二测试信号传递给逻辑晶圆及将第三测试信号传递给逻辑晶圆。

7、其中,通信接口电路包括qspi电路,qspi电路包括qspi pad,qspi pad设置于逻辑晶圆层的表面,用于接收测试时序信号。

8、其中,3d存储装置还包括:冗余测试电路,设置在逻辑晶圆层,且分别与第一测试点、第二测试点及第三测试点连接,用于在测试电路故障时基于测试时序信号对存储晶圆、逻辑晶圆、存储晶圆与逻辑晶圆之间的交互进行测试。

9、为解决上述技术问题,本申请采用的另一个技术方案是:提供一种芯片,包括上述3d存储装置。

10、为解决上述技术问题,本申请采用的另一个技术方案是:提供一种3d存储装置的测试系统,包括上述3d存储装置。

11、其中,测试系统还包括:机台,用于接收测试用例,并基于测试用例生成测试时序信号;探针,分别与机台和测试电路连接,用于将测试时序信号传送给测试电路。

12、其中,测试系统还包括:仿真机构,用于生成测试用例。

13、为解决上述技术问题,本申请采用的另一个技术方案是:提供一种3d存储装置的测试方法,用于上述测试系统,测试方法包括:获取测试时序信号;基于测试时序信号生成第一测试信号、第二测试信号及第三测试信号及测试顺序;基于测试顺序分别利用第一测试信号对存储晶圆进行测试,利用第二测试信号对逻辑晶圆进行测试、利用第三测试信号对存储晶圆与逻辑晶圆之间的交互进行测试。

14、其中,测试方法还包括:获取对存储晶圆、逻辑晶圆、存储晶圆与逻辑晶圆之间的交互进行测试的测试结果;基于测试用例及测试结果确定测试电路是否异常;若异常,则启用测试电路对应的冗余测试电路对存储晶圆、逻辑晶圆、存储晶圆与逻辑晶圆之间的交互进行测试。

15、其中,在基于测试用例及测试结果确定测试电路是否异常之前,还包括:基于测试用例及测试结果确定二者是否匹配;若不匹配,利用另一测试用例对存储晶圆、逻辑晶圆及二者之间的交互进行重新测试;基于测试用例及测试结果确定测试电路是否异常,包括:若重新测试的次数大于或者等于阈值,则确定测试电路异常。

16、其中,获取测试时序信号,包括:生成测试用例,并基于测试用例及3d存储装置的仿真模型对3d存储装置进行仿真测试;在仿真测试过程中采集仿真模型的状态信息;基于状态信息生成测试时序信号。

17、本申请的有益效果是:区别于现有技术的情况,本申请的3d存储装置包括存储晶圆层、逻辑晶圆层及测试电路。存储晶圆层用于存储数据,存储晶圆层设有第一测试点,第一测试点用于对存储晶圆层的存储晶圆进行测试;逻辑晶圆层设置在存储晶圆层的一侧,且逻辑晶圆层中的逻辑晶圆与存储晶圆连接,用于对从存储晶圆读出的数据进行逻辑处理及对要存入存储晶圆的数据进行逻辑处理,逻辑晶圆层设有第二测试点及第三测试点,第二测试点用于对逻辑晶圆进行测试,第三测试点用于对存储晶圆与逻辑晶圆之间的交互进行测试;测试电路设置在逻辑晶圆层,且分别与第一测试点、第二测试点及第三测试点连接,测试电路用于基于测试时序信号对存储晶圆、逻辑晶圆、存储晶圆与逻辑晶圆之间的交互进行测试。通过上述方式,本申请的3d存储装置自带测试电路,测试电路分别与存储晶圆层的第一测试点、逻辑晶圆层的第二测试点及第三测试点连接,并根据需求基于测试时序信号对存储晶圆、逻辑晶圆、存储晶圆与逻辑晶圆之间的交互进行测试,能够提高测试的灵活性及测试的有效性,提高3d存储装置的良率。

技术特征:

1.一种3d存储装置,其特征在于,包括:

2.根据权利要求1所述的3d存储装置,其特征在于,所述测试电路包括:

3.根据权利要求2所述的3d存储装置,其特征在于,所述测试电路还包括:

4.根据权利要求2或3所述的3d存储装置,其特征在于,所述测试电路还包括:

5.根据权利要求2或3所述的3d存储装置,其特征在于,所述测试电路还包括:

6.根据权利要求2所述的3d存储装置,其特征在于,所述通信接口电路包括qspi电路,所述qspi电路包括qspi pad,qspi pad设置于所述逻辑晶圆层的表面,用于接收所述测试时序信号。

7.根据权利要求1所述的3d存储装置,其特征在于,还包括:

8.一种芯片,其特征在于,包括权利要求1至7任一项所述的3d存储装置。

9.一种3d存储装置的测试系统,其特征在于,包括:权利要求1至7任一项所述的3d存储装置。

10.根据权利要求9所述的测试系统,其特征在于,还包括:

11.根据权利要求10所述的测试系统,其特征在于,所述测试系统还包括:

12.一种3d存储装置的测试方法,其特征在于,用于权利要求9至11任一项所述的测试系统,所述测试方法包括:

13.根据权利要求12所述的测试方法,其特征在于,还包括:

14.根据权利要求13所述的测试方法,其特征在于,在所述基于所述测试用例及所述测试结果确定所述测试电路是否异常之前,还包括:

15.根据权利要求12所述的测试方法,其特征在于,所述获取所述测试时序信号,包括:

技术总结

本申请公开了3D存储装置、芯片、3D存储装置的测试系统及测试方法。3D存储装置包括:存储晶圆层,用于存储数据,存储晶圆层设有第一测试点;逻辑晶圆层,设置在存储晶圆层的一侧,且逻辑晶圆层中的逻辑晶圆与存储晶圆连接,用于对从存储晶圆读出的数据进行逻辑处理及对要存入存储晶圆的数据进行逻辑处理,逻辑晶圆层设有第二测试点及第三测试点;测试电路,设置在逻辑晶圆层,且分别与第一测试点、第二测试点及第三测试点连接,测试电路用于基于测试时序信号对存储晶圆、逻辑晶圆、存储晶圆与逻辑晶圆之间的交互进行测试。本申请能够提高测试的灵活性及有效性,提高3D存储装置的良率。

技术研发人员:王玉冰,刘枢

受保护的技术使用者:西安紫光国芯半导体有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!