存储器器件的制作方法

本申请的实施例涉及一种存储器器件。

背景技术:

1、集成电路处理器需要从存储器获取数据。动态随机存取存储器(dram)是经常使用的。然而,dram在存取速度和功耗方面不够高效。数据存取的低效率被称为“存储器墙”。高性能计算处理器必须克服“存储器墙”。

技术实现思路

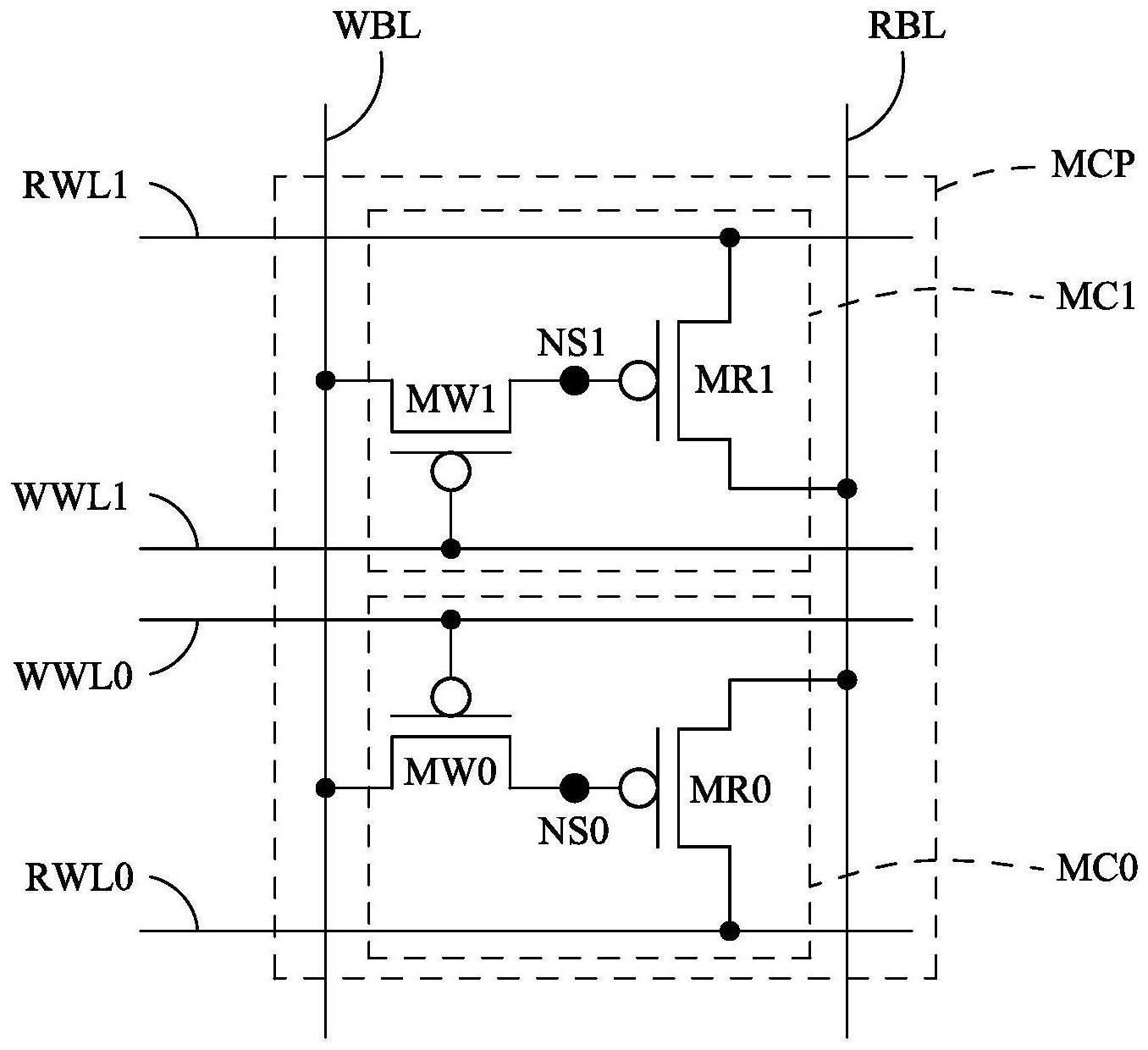

1、根据本申请的实施例的一个方面,提供了一种存储器器件,包括:写入位线和读取位线,在第一方向上延伸;第一写入字线和第一读取字线,在垂直于所述第一方向的第二方向上延伸;以及第一存储器单元,所述第一存储器单元包括:第一写入晶体管,所述第一写入晶体管包括:第一栅极,连接到所述第一写入字线;第一源极/漏极,连接到所述写入位线;和第二源极/漏极,连接到第一数据储存节点;以及第一读取晶体管,所述第一读取晶体管包括:第二栅极,连接到所述第一数据储存节点;第三源极/漏极,连接到所述读取位线;和第四源极/漏极,连接到所述第一读取字线。

2、根据本申请的实施例的另一个方面,提供了一种存储器器件,包括:存储器阵列,所述存储器阵列包括:多个存储器单元对,排列成多个列和多个行,其中多个存储器单元对中的每个存储器单元对包括:第一存储器单元,所述第一存储器单元包括:第一写入晶体管,被配置为响应于第一写入信号将第一输入数据写入到第一数据储存节点;第一读取晶体管,被配置为响应于所述第一数据储存节点上的所述第一输入数据和第一读取信号向读取位线输出第一输出数据;以及第二存储器单元,所述第二存储器单元包括:第二写入晶体管,被配置为响应于第二写入信号将第二输入数据写入到第二数据储存节点;和第二读取晶体管,被配置为响应于所述第二数据储存节点上的所述第二输入数据和第二读取信号向所述读取位线输出第二输出数据。

3、根据本申请的实施例的又一个方面,提供了一种存储器器件,包括:写入位线和读取位线,在第一方向上延伸;写入字线和读取字线,在垂直于所述第一方向的第二方向上延伸;存储器单元,所述存储器单元包括:写入晶体管,包括:第一栅极,连接到所述写入字线;第一源极/漏极,连接到所述写入位线;和第二源极/漏极,连接到数据储存节点;以及读取晶体管,包括:第二栅极,连接到所述数据储存节点;第三源极/漏极,连接到所述读取位线;和第四源极/漏极,连接到所述读取字线;电源供电节点,所述电源供电节点为vdd节点或vss节点;以及伪晶体管,所述伪晶体管包括:第三栅极,连接到所述电源供电节点;和第五源极/漏极,连接到所述数据储存节点。

技术特征:

1.一种存储器器件,包括:

2.根据权利要求1所述的存储器器件,其中:

3.根据权利要求1所述的存储器器件,其中,所述第一存储器单元中的晶体管的总数等于两个。

4.根据权利要求1所述的存储器器件,其中,所述第一写入晶体管和所述第一读取晶体管都是p型晶体管。

5.根据权利要求1所述的存储器器件,其中,所述第一写入晶体管和所述第一读取晶体管都是n型晶体管。

6.根据权利要求1所述的存储器器件,还包括:

7.根据权利要求6所述的存储器器件,还包括:

8.根据权利要求7所述的存储器器件,其中,所述伪晶体管包括:

9.一种存储器器件,包括:

10.一种存储器器件,包括:

技术总结

一种存储器器件包括在第一方向上延伸的写入位线和读取位线,以及在垂直于第一方向的第二方向上延伸的写入字线和读取字线。存储器器件还包括存储器单元,该存储器单元包括写入晶体管和读取晶体管。写入晶体管包括连接到写入字线的第一栅极、连接到写入位线的第一源极/漏极以及连接到数据储存节点的第二源极/漏极。读取晶体管包括连接到数据储存节点的第二栅极、连接到读取位线的第三源极/漏极以及连接到读取字线的第四源极/漏极。

技术研发人员:刘仁杰,吴瑞仁,柯文昇,吕易伦,张孟凡

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!