带有低噪声源跟随器的图像传感器像素结构及其制作方法与流程

[0001]

本发明涉及模拟集成电路领域,尤其涉及一种带有低噪声源跟随器的图像传感器像素结构及其制作方法。

背景技术:

[0002]

随着图像传感器技术的迅速发展,其在消费电子、工业电子、汽车电子、科学研究、广播电视、安防监控、医疗影像、航空航天等场景的工程应用日渐广泛。像素作为图像传感器的核心部分,将直接决定量子效率、噪声、满阱容量、信噪比、动态范围、暗电流等关键特征参数,进而影响图像传感器的整体性能指标。因此,优化像素器件结构并提高像素特征参数是发展高性能图像传感器的主要技术路线。

[0003]

目前,传统四管有源像素结构主要由钳位光电二极管(pinned photodiode, ppd)、浮空扩散(floating diffusion, fd)节点、传输管(tg)、复位管(rst)、源跟随器(source follower, sf)和选通管(sel)组成。随着图像传感器读出电路噪声的降低以及像素单元尺寸的缩小,像素内源跟随器噪声(主要为闪烁噪声,亦称为1/f噪声)在系统总读出噪声中的所占比例逐渐增大,源跟随器已经成为小尺寸(如像素中心距小于2um)四管有源像素的主要噪声来源。在传统四管有源像素中,源跟随器通过浅沟槽隔离(shallow trench isolation, sti)结构与像素内其它部分进行电学隔离。同时,源跟随器的sti结构与硅材料之间存在si-sio2交界面,在该交界面处存在大量的缺陷,这些缺陷的存在将导致源跟随器噪声的增大,进而影响整个图像传感器的成像质量。

技术实现要素:

[0004]

针对现有技术中存在的技术问题,本发明提出了一种带有低噪声源跟随器的图像传感器像素结构及其制作方法。该像素结构中的无浅沟槽隔离源跟随器的第一个特征为,使用p+型隔离层结构代替sti结构,在实现电学隔离功能的基础上,降低晶体管沟道边缘区域的缺陷密度;其第二个特征为,降低源跟随器晶体管栅氧化层厚度,提高单位面积栅氧化层电容值;这两个特征共同作用于像素内源跟随器的噪声(尤其是1/f噪声)的降低,从而提升像素的噪声特性,并最终优化图像传感器的成像质量。此外,该像素结构中的无浅沟槽隔离源跟随器在小尺寸有源像素中的噪声优化效果更加明显。

[0005]

带有低噪声源跟随器的图像传感器像素结构,其像素版图如图1所示。该像素版图的具体描述如下(括号内数字与图1中数字相互对应):钳位光电二极管(ppd)区(101)右下侧连接传输管(tg)多晶硅栅极(102)左侧;tg多晶硅栅极(102)右侧连接n型浮空扩散区(fd区)(103)左侧;n型fd区(103)上侧连接复位管(rst)多晶硅栅极(104)下侧;rst多晶硅栅极(104)上侧连接n型电源(vdd)区(105)下侧;n型vdd区(105)上侧连接源跟随器(sf)多晶硅栅极(106)下侧;sf多晶硅栅极(106)上侧连接n型连接区(107)下侧;该n型连接区(107)上侧连接选通管(sel)多晶硅栅极(108)下侧;sel多晶硅栅极(108)上侧连接n型输出(out)区(109)下侧;sf多晶硅栅极(106)左右两侧通过p+型隔离层(112)进行电学隔离;p+型隔离层

(112)位于环绕sf的p型阱(111)之中;像素版图其余非有源区部分为浅沟槽隔离(sti)结构(110)。当本发明应用于小尺寸像素时,在该像素版图结构的基础上可以采取共享读出型版图布局方案(如两个及两个以上像素单元共用一个sf管和一个sel管),从而进一步缩小像素单元尺寸。因此,本发明提出的无浅沟槽隔离源跟随器结构同样适用于共享读出型版图设计结构。

[0006]

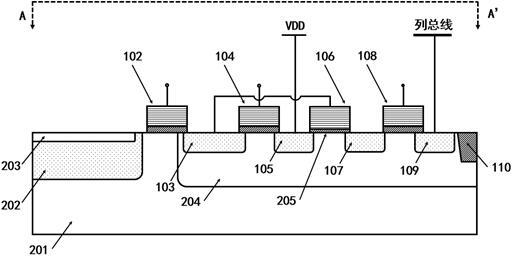

带有低噪声源跟随器的图像传感器像素结构,其截面图如图2所示,即图1像素版图中沿折线段aa’切片的横截面。该像素结构的具体描述如下(括号内数字与图2中数字相互对应):该像素结构基于p型硅外延层(201);p+型钳位层(203)位于p型硅外延层(201)上表面;p+型钳位层(203)位于n型pd区(202)上方;p+型钳位层(203)与n型pd区(202)共同组成ppd区(101);tg多晶硅栅极(102)、rst多晶硅栅极(104)、sel多晶硅栅极(108)与p型硅外延层(201)上表面隔着一层普通厚度栅氧化层相连,形成金属氧化物半导体型结构;sf多晶硅栅极(106)与p型硅外延层(201)上表面隔着一层薄栅氧化层(205)相连,形成金属氧化物半导体型结构;n型fd区(103)、n型vdd区(105)、连接sf栅和sel栅的n型连接区(107)、n型out区(109)、sti结构(110)位于p型阱(204)之中;ppd区(101)右侧与tg多晶硅栅极(102)左侧相连;tg多晶硅栅极(102)右侧与n型fd区(103)左侧相连;n型fd区(103)右侧与rst多晶硅栅极(104)左侧相连;rst多晶硅栅极(104)右侧与n型vdd区(105)左侧相连;n型vdd区(105)右侧与sf多晶硅栅极(106)左侧相连;sf多晶硅栅极(106)右侧与n型连接区(107)左侧相连;该n型连接区(107)右侧与sel多晶硅栅极(108)左侧相连;sel多晶硅栅极(108)右侧与n型out区(109)左侧相连;n型out区(109)右侧与sti结构(110)相连;n型fd区(103)通过金属线与sf多晶硅栅极(106)相连;n型vdd区(105)通过金属线与电源相连;n型out区(109)通过金属线与列总线相连。

[0007]

无浅沟槽隔离源跟随器结构以及与之对比的传统源跟随器结构,具体如图3所示,其中无浅沟槽隔离源跟随器即为图1像素版图中沿直线段bb’切片的横截面。该无浅沟槽源跟随器结构的具体描述如下(括号内数字与图3中数字相互对应):源跟随器基于p型硅外延层(201);sf多晶硅栅极(106)下方为薄栅氧化层(205);sf多晶硅栅极(106)两侧与p+型隔离层(112)相连;p+型隔离层(112)位于环绕sf的p型阱(111)之中。与之对比的传统源跟随器结构的具体描述如下:源跟随器基于p型外延层;sf栅下方为普通厚度栅氧化层;sf栅两侧与sti结构相连。通过对比以上两种源跟随器结构可知,传统源跟随器sti结构与晶体管沟道边缘区域之间的si-sio2交界面处存在大量的缺陷;而无浅沟槽隔离源跟随器通过使用p+型隔离层(112)结构代替sti结构,在保持电学隔离功能的基础上,有效地降低了晶体管沟道边缘区域的缺陷密度。同时,传统源跟随器栅极下方为普通厚度栅氧化层,无浅沟槽隔离源跟随器栅极下方为薄栅氧化层,相比之下提高了单位面积栅氧化层电容值。因此,采用无浅沟槽隔离源跟随器可以有效降低像素内源跟随器噪声(尤其是1/f噪声),进而降低整个像素的噪声。

[0008]

带有低噪声源跟随器的图像传感器像素结构,其工作过程(括号内数字与图1及图2中数字相互对应)为:tg多晶硅栅极(102)和rst多晶硅栅极(104)同时置高电平(如3.3v),对ppd区(101)进行复位,保持一定时间后二者置低电平(如0.0v);入射光由像素正面入射至ppd区(101)产生一定数量的光生电子;rst多晶硅栅极(104)置高电平,对n型fd区(103)进行复位,保持一定时间后rst多晶硅栅极(104)置低电平;sel多晶硅栅极(108)保持高电

平状态,读取此时n型out区(109)的复位信号v(rst);tg多晶硅栅极(102)置高电平,ppd区(101)光生电子转移至n型fd区(103),保持一定时间后tg多晶硅栅极(102)置低电平;sel多晶硅栅极(108)保持高电平状态,读取此时n型out区(109)的光信号v(signal)。根据相关双采样(correlated doubled sampling, cds)原理,v(signal)与v(rst)的差值即为像素的最终输出信号值。

[0009]

带有低噪声源跟随器的图像传感器像素结构,其制作方法(括号内数字与图1、图2及图3中数字相互对应)为:在硅衬底上生长一层p型硅外延层(201);在p型硅外延层(201)上方沉积一层普通厚度氧化层,对后续工艺中将要生成源跟随器栅(106)的区域所对应的氧化层进行刻蚀,形成薄栅氧化层(205);基于p型硅外延层(201)通过多次沉积和刻蚀形成浅沟槽隔离结构(110);选用p型杂质,在相应位置进行离子注入,形成p型阱(204);选用n型杂质,在相应位置进行离子注入,形成光电二极管n型区(202);通过多次沉积和刻蚀,在相应位置上形成多晶硅栅,包括传输栅(102)、复位栅(104)、源跟随器栅(106)、选通管栅(108);选用较高浓度p型杂质,在光电二极管n型区(202)上方进行离子注入,形成p+型钳位层(203);选用p型杂质,在源跟随器栅(106)附近相应位置进行离子注入,形成环绕sf的p型阱(111);选用高浓度p型杂质,在源跟随器栅(106)附近相应位置进行离子注入,形成p+型隔离层(112);选用n型杂质,在相应位置进行离子注入形成源漏区,包括n型浮空扩散区(103)、n型电源区(105)、源跟随器与选通管n型连接区(107)、n型输出区(109);在相应栅极和源漏区形成金属孔及金属线并最终完成像素制作。

[0010]

带有低噪声源跟随器的图像传感器像素结构,在实现电学隔离功能的基础上,降低源跟随器晶体管沟道边缘区域的缺陷密度,提高源跟随器的单位面积栅氧化层电容值,降低源跟随器噪声,提升像素单元及像素阵列的噪声特性,并最终优化整个图像传感器的成像质量。

附图说明

[0011]

图1是本发明带有无浅沟槽隔离低噪声源跟随器的像素版图示意图;图2是本发明带有无浅沟槽隔离低噪声源跟随器的像素结构示意图;图3是传统源跟随器(左)与无浅沟槽隔离低噪声源跟随器(右)结构对比示意图。

具体实施方式

[0012]

下面结合附图和具体实施例对本发明作进一步说明,但本发明所要保护的范围并不限于此。

[0013]

基于不同类型的工艺条件,本发明提出的像素结构涉及的关键参数需要根据实际情况进行调整,从而在相应的工艺条件下达到最佳状态。需要调整的具体工艺参数包括:像素单元的尺寸;硅外延层的厚度和掺杂浓度;多晶硅栅与硅材料之间氧化层的厚度;各次离子注入的能量、剂量和角度;各次沉积或刻蚀材料的厚度;各次退火的温度和时间;光刻胶的厚度等等。下面,基于标准cmos工艺,提出一种应用本发明像素结构的可行性较好的实施方案。

[0014]

对于像素结构关键部分的工艺参数,给出一种实施方式如下(括号内数字与图2中数字相互对应):像素尺寸根据设计需求进行调整,且像素尺寸较小时,本发明像素结构中

的无浅沟槽隔离源跟随器的噪声优化效果更明显;传输管、复位管、源跟随器等结构的实际尺寸根据像素设计尺寸进行增大或减小;对于小尺寸像素,其像素中心距应小于2um;当像素中心距为2um时,源跟随器栅长及栅宽为0.3~0.5um;p型外延层厚度(201)为4~5um;普通厚度栅氧化层的厚度为8~10nm;源跟随器栅极下方的薄栅氧化层(205)厚度为2~6nm;p型硅外延层(201)掺杂浓度为10

15

cm-3

量级;p+型钳位层(203)掺杂浓度为10

17

到10

18

cm-3

量级;n型pd区(202)掺杂浓度为10

15

到10

17

cm-3

量级;n型fd节点区(103)掺杂浓度为10

17

到10

19

cm-3

量级;n型vdd区(105)掺杂浓度为10

17

到10

20

cm-3

量级;n型连接区(107)掺杂浓度为10

17

到10

19

cm-3

量级;n型out区(109)掺杂浓度为10

17

到10

19

cm-3

量级;p型阱(204)掺杂浓度为10

16

到10

17

cm-3

量级。

[0015]

对于无浅沟槽隔离源跟随器结构关键部分的工艺参数,给出一种实施方式如下(括号内数字与图3中数字相互对应):p型硅外延层(201)掺杂浓度为10

15

cm-3

量级;环绕sf的p型阱(111)掺杂浓度为10

16

到10

17

cm-3

量级;p+型隔离层(112)掺杂浓度为10

18

到10

20

cm-3

量级。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1