静电放电防护装置与方法与流程

[0001]

本案是有关于一种静电放电防护装置,且特别是有关于采用中值电压的静电放电防护装置与方法。

背景技术:

[0002]

一般而言,集成电路由一或多个晶体管实现。随着制程发展,晶体管的尺寸越来越小。为了避免静电放电所造成的过度电压应力造成的损坏,通常会使用静电放电防护电路来保护集成电路免于静电放电的伤害。在现有的技术中,考量到耐压,静电放电防护电路皆以输入输出晶体管实施。如此,静电放电防护电路中的放电路径的内阻可能较高,而降低静电放电防护电路的效能。

技术实现要素:

[0003]

为了解决上述问题,本案的一些态样是于提供一种静电放电防护装置,其包含第一箝位电路、第二箝位电路以及二极管电路。第一箝位电路耦接于一第一电源轨与一第二电源轨之间。第二箝位电路耦接于一第三电源轨与该第二电源轨之间。二极管电路用以导向来自一输入输出垫的一静电放电电流至该第一箝位电路或该第三电源轨中的至少一者。其中该第一电源轨接收一第一电压,该第二电源轨接收一第二电压,该第三电源轨接收一第三电压,该第三电压高于该第一电压,且该第一电压高于该第二电压。

[0004]

于一些实施例中,该第一箝位电路由多个核心晶体管实施,且该第二箝位电路由多个输入输出晶体管或多个堆叠核心晶体管实施。

[0005]

于一些实施例中,该第一电压为该第三电压的2/3~3/4倍。

[0006]

于一些实施例中,该第一箝位电路的一放电能力高于该第二箝位电路的一放电能力。

[0007]

于一些实施例中,该第一箝位电路的一内阻低于该第二箝位电路的一内阻。

[0008]

于一些实施例中,该二极管电路包含第一二极管、第二二极管以及第三二极管。该第一二极管的阳极耦接至该输入输出垫,且该第一二极管的阴极耦接至该第一电源轨。该第二二极管的阳极耦接至该第一电源轨,且该第二二极管的阴极耦接至该第三电源轨。该第三二极管的阳极耦接至该第二电源轨,且该第三二极管的阴极耦接至该输入输出垫。

[0009]

于一些实施例中,该静电放电电流经由该第一二极管导向至该第一箝位电路,或依序经由该第一二极管与该第二二极管导向至该第三电源轨。

[0010]

于一些实施例中,该二极管电路包含第一二极管、第二二极管以及第三二极管。该第一二极管的阳极耦接至该输入输出垫,且该第一二极管的阴极耦接至该第一电源轨。其中该第二二极管的阳极耦接至该输入输出垫,且该第二二极管的阴极耦接至该第三电源轨。该第三二极管的阳极耦接至该第二电源轨,且该第三二极管的阴极耦接至该输入输出垫。

[0011]

于一些实施例中,该静电放电电流经由该第一二极管导向至该第一箝位电路,或

经由该第二二极管导向至该第三电源轨。

[0012]

于一些实施例中,该二极管电路包含第一二极管、第二二极管以及第三二极管。该第一二极管的阳极耦接至该输入输出垫,且该第一二极管的阴极耦接至该第一电源轨。该第二二极管的阳极耦接至该第二电源轨,且该第二二极管的阴极耦接至该第三电源轨。该第三二极管的阳极耦接至该第二电源轨,且该第三二极管的阴极耦接至该输入输出垫。

[0013]

于一些实施例中,该静电放电电流经由该第一二极管导向至该第一箝位电路,或依序经由该第一二极管、该第一箝位电路以及该第二二极管导向至该第三电源轨。

[0014]

本案的一些态样是于提供一种静电放电防护方法,其包含下列操作:经由一二极管电路导向来自一输入输出垫的一静电放电电流至一第一箝位电路或一第一电源轨中的至少一者;以及经由该第一箝位电路对该静电放电电流进行放电,其中该第一箝位电路耦接于一第二电源轨与一第三电源轨之间,一第二箝位电路耦接于该第一电源轨与该第二电源轨之间,该第一电源轨接收一第一电压,该第二电源轨接收一第二电压,该第三电源轨接收一第三电压,该第一电压高于该第三电压,且该第三电压高于该第二电压。

[0015]

综上所述,本案一些实施例提供的静电放电防护装置与静电放电防护方法可提供一组具有更低工作电压与更低内阻的箝位电路,以提升静电放电防护装置的效能。

附图说明

[0016]

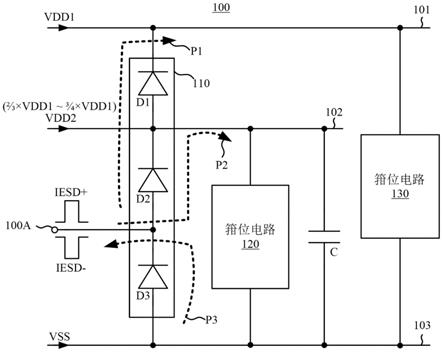

图1为根据本案一些实施例所绘制的静电放电(electrostatic discharge,esd)防护装置的示意图;

[0017]

图2为根据本案一些实施例所绘制的esd防护装置的示意图;

[0018]

图3为根据本案一些实施例所绘制的esd防护装置的示意图;

[0019]

图4为根据本案一些实施例所绘制的箝位电路的示意图;

[0020]

图5为根据本案一些实施例所绘制的箝位电路的示意图;以及

[0021]

图6为根据本案一些实施例所绘制的一种esd防护方法的流程图。

[0022]

【符号说明】

[0023]

100:静电放电防护装置

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

100a:输入输出垫

[0024]

110:二极管电路

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

120、130:箝位电路

[0025]

101:电源轨

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

102:电源轨

[0026]

103:电源轨

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

d1~d3:二极管

[0027]

iesd+:正静电放电电流

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

iesd-:负静电放电电流

[0028]

p1~p3:路径

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

vdd1~vdd2、vss:电压

[0029]

c、c1、c2:电容

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

r1、r2:电阻

[0030]

t1~t5:晶体管

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

q1~q3:晶体管

[0031]

410:反相器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

vc:控制信号

[0032]

600:esd防护方法

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

s610、s620:操作

具体实施方式

[0033]

下文是举实施例配合所附附图作详细说明,但所提供的实施例并非用以限制本案所涵盖的范围,而结构操作的描述非用以限制其执行的顺序,任何由元件重新组合的结构,

所产生具有均等功效的装置,皆为本案所涵盖的范围。

[0034]

另外,关于本文中所使用的“耦接”或“连接”,均可指二或多个元件相互直接作实体或电性接触,或是相互间接作实体或电性接触,亦可指二或多个元件相互操作或动作。

[0035]

在本文中,使用第一、第二与第三等等的词汇,是用于描述各种元件是可以被理解的。但是这些元件不应该被这些术语所限制。这些词汇只限于用来辨别单一元件。因此,在下文中的一第一元件也可被称为第二元件,而不脱离本案的本意。

[0036]

于本文中,用语“电路系统(circuitry)”可泛指包含一或多个电路(circuit)所形成的单一系统。用语“电路”可泛指由一或多个晶体管与/或一或多个主被动元件按一定方式连接以处理信号的物件。

[0037]

关于本文中所使用的“约”、“大约”或“大致

“”

一般通常是指数值的误差或范围约百分之二十以内,较好地是约百分之十以内,而更佳地则是约百分之五以内。文中若无明确说明,其所提及的数值皆视作为近似值,即如“约”、“大约”或“大致约”所表示的误差或范围。

[0038]

为易于理解,以下各附图中的类似元件将被指定为相同标号。

[0039]

图1为根据本案一些实施例所绘制的静电放电(electrostatic discharge,esd)防护装置100的示意图。于一些实施例中,esd防护装置100可应用于晶片或集成电路中的输入输出(input/output,i/o)接口中,以避免来自i/o垫(pad)100a的esd事件损坏晶片或集成电路中的内部元件。

[0040]

于一些实施例中,esd防护装置100包含二极管电路110、箝位电路120以及箝位电路130。二极管电路110耦接至电源轨101、102与103。二极管电路110用以导向因i/o垫100a上的esd事件所产生的esd电流至箝位电路120与/或电源轨101中至少一者。例如,二极管电路110包含多个二极管d1~d3。二极管d1的阳极耦接至电源轨102,且二极管d1的阴极耦接至电源轨101。二极管d2的阳极耦接至i/o垫100a,且二极管d2的阴极耦接至电源轨102。二极管d3的阳极耦接至电源轨103,且二极管d3的阴极耦接至i/o垫100a。当esd事件发生时,i/o垫100a上出现正esd电流iesd+。此正esd电流iesd+可经由二极管d2(即路径p2)导向至电源轨102以及箝位电路120,或依序经由二极管d2与d1(即路径p1)导向至电源轨101(以及箝位电路130)。或者,当esd事件发生时,i/o垫100a上出现负esd电流iesd-。此负esd电流iesd-可经由二极管d3(即路径p3)导向至电源轨103。

[0041]

如图1所示,电源轨101接收电压vdd1,电源轨102接收电压vdd2,且电源轨103接收电压vss。于一些实施例中,电压vdd1高于电压vdd2,且电压vdd2高于电压vss。

[0042]

箝位电路120耦接于电源轨102与电源轨103之间,且箝位电路130耦接于电源轨101与电源轨103之间。响应于来自i/o垫100a的esd事件,箝位电路120与/或箝位电路130中至少一者会导通而提供至少一放电路径。如此一来,因esd事件所产生的正esd电流iesd+可透过箝位电路120或130中至少一者进行放电,以避免误损坏晶片或集成电路中的其他元件。

[0043]

于一些实施例中,箝位电路120的放电能力(相当于电流驱动能力)高于箝位电路130的放电能力。于一些实施例中,箝位电路120的内阻低于箝位电路130的内阻。于一些实施例中,箝位电路120可由核心(core)晶体管实施,且箝位电路130可由i/o晶体管实施。一般而言,核心晶体管用于实施晶片中的主要电路部分,而i/o晶体管具有相对较高的耐压能

力,且通常用于实施i/o接口电路。核心晶体管的临界电压低于i/o晶体管的临界电压。因此,箝位电路120可在较低的工作电压下导通而提供放电路径。此外,相较于i/o晶体管,使用核心晶体管实施的箝位电路120所提供的放电路径具有较低的内阻。如此一来,当存在有正esd电流iesd+时,箝位电路120可以更快地导通而对此正esd电流iesd+进行放电,以提供esd防护。换言之,通过设置箝位电路120,esd防护装置100的效能可以进一步改善。

[0044]

于一些实施例中,箝位电路120的工作电压(例如为电压vdd2)低于箝位电路130的工作电压(例如为电压vdd1)。于一些实施例中,电压vdd2可低于电压vdd1并高于或等于核心晶体管的标称核心(nominal core)电压。于一些实施例中,电压vdd2约为2/3倍~3/4倍的电压vdd1。于一些实施例中,电压vdd2可低于2/3倍的电压vdd1。上述倍数关系用于示例,且本案并不以此些倍数为限。

[0045]

于一些相关应用中,考量到耐压,只使用i/o晶体管实施esd防护装置。然而,由于较高的临界电压与/或是堆叠电路结构,使用i/o晶体管实施的电路会具有较高的内阻。如此,会导致正esd电流iesd+与负esd电流iesd-的放电速度过于不平衡,而降低esd防护的效能。相较于上述技术,通过设置箝位电路120,可有效降低放电路径的内阻,以进一步平衡正esd电流iesd+与负esd电流iesd-的放电速度。

[0046]

于一些实施例中,esd防护装置100可还包含一电容c。电容c耦接于电源轨102与电源轨103之间,以提供一辅助路径来对正esd电流iesd+进行放电。

[0047]

图2为根据本案一些实施例所绘制的esd防护装置100的示意图。相较于图1,在此例中,二极管d1耦接于i/o垫100a与电源轨101之间,其中二极管d1的阳极耦接于i/o垫100a,且二极管d1的阴极耦接于电源轨101。换言之,于此例中,i/o垫100a可在不经由二极管d2耦接至电源轨101。如此,当存在有正esd电流iesd+时,此正esd电流iesd+可经由二极管d1(即路径p1)直接导向至电源轨101(以及箝位电路130),或可经由二极管d2(即路径p2)直接导向至电源轨102以及箝位电路120。

[0048]

图3为根据本案一些实施例所绘制的esd防护装置100的示意图。相较于图1,在此例中,二极管d1耦接于电源轨103与电源轨101之间,其中二极管d1的阳极耦接于电源轨103,且二极管d1的阴极耦接于电源轨101。如此,当存在有正esd电流iesd+时,除了前述的路径p2,此正esd电流iesd+更可依序经由二极管d2、箝位电路120与二极管d1(即路径p1)导向至电源轨101(与箝位电路130)。

[0049]

图4为根据本案一些实施例所绘制的箝位电路120的示意图。于此例中,晶体管t1~t3由核心晶体管实施。

[0050]

箝位电路120包含电阻r1、电容c1以及晶体管t1~t3。电阻r1的第一端耦接至电源轨102,且电阻r1的第二端耦接至电容c1的第一端。电容c1的第二端耦接至电源轨103。晶体管t1与晶体管t2操作为反相器410。晶体管t1的第一端耦接至电源轨102,晶体管t1的第二端耦接至晶体管t2的第一端,且晶体管t1以及晶体管t2的控制端耦接至电容c1的第一端。晶体管t2的第二端耦接至电源轨103。晶体管t3用以提供对正esd电流iesd+的放电路径。晶体管t3的第一端耦接至电源轨102,晶体管t3的第二端耦接至电源轨103,且晶体管t3的控制端耦接至晶体管t1的第二端。

[0051]

当存在有正esd电流iesd+,电容c1的第一端会耦接至电源轨103,以拉低电容c1的第一端的电位至较低的电压vss。反相器410据此输出具有电压vdd2的控制信号vc。响应于

此控制信号vc,晶体管t3被导通以放电正esd电流iesd+。

[0052]

图5为根据本案一些实施例所绘制的箝位电路130的示意图。于此例中,晶体管q1~q3由i/o晶体管实施。

[0053]

箝位电路130包含电阻r2、电容c2以及晶体管q1~q3。相较箝位电路120,箝位电路130耦接至电源轨101而非电源轨102,且箝位电路130的其余电路结构类似于箝位电路120的电路结构,故于此不再重复赘述。

[0054]

上述关于箝位电路120与箝位电路130的电路设置方式用于示例,且本案并不以此为限。例如,于其他实施例中,箝位电路120与箝位电路130亦可由硅控整流器电路实施。或者,如图5所示,于其他实施例中,晶体管q1~q3每一者亦可由多个堆叠核心晶体管实施。以晶体管q3为例,晶体管q3可改由二个或更多的核心晶体管t4与t5实施,其中这些核心晶体管t4与t5相互堆叠,以等效操作为单一晶体管q3。

[0055]

上述各实施例中的元件(二极管、电容、晶体管等等)数量用于示例,依据不同的应用,esd防护装置100中的元件数量可相应地调整。

[0056]

图6为根据本案一些实施例所绘制的一种esd防护方法600的流程图。

[0057]

于操作s610,经由二极管电路110导向来自输入输出垫100a的静电放电电流iesd+至箝位电路120或电源轨101中的至少一者。

[0058]

于操作s620,经由箝位电路120对正esd电流iesd+进行放电。

[0059]

上述操作s610与操作s620的说明可参照前述图1~图5的实施例,故不重复赘述。上述esd防护方法600的多个操作仅为示例,并非限于上述示例的顺序执行。在不违背本案各实施例的操作方式与范围下,在esd防护方法600下的各种操作当可适当地增加、替换、省略或以不同顺序执行。

[0060]

综上所述,本案一些实施例提供的esd防护装置与esd防护方法可提供一组具有更低工作电压与更低内阻的箝位电路,以提升esd防护装置的效能。

[0061]

虽然本案已以实施方式揭露如上,然其并非限定本案,任何熟悉此技艺者,在不脱离本案的精神和范围内,当可作各种的更动与润饰,因此本案的保护范围当视所附的权利要求书所界定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1