存储器装置的制作方法

存储器装置

[0001]

本申请要求于2019年8月6日在韩国知识产权局提交的第10-2019-0095526号韩国专利申请的优先权的权益,该韩国专利申请的公开通过引用全部包含于此。

技术领域

[0002]

本公开涉及存储器装置。

背景技术:

[0003]

存储器装置可以提供写入数据和擦除数据或者读取写入的数据的功能。存储器装置可以被分类为非易失性存储器装置和易失性存储器装置。即使当非易失性存储器装置的电源被中断时,非易失性存储器装置也保留其存储的数据。存储器装置所需的数据存储容量趋于增加。因此,已经提出各种方法以增加存储器装置的集成密度。

技术实现要素:

[0004]

示例实施例提供了一种存储器装置,所述存储器装置的集成密度通过将包括在存储器装置中的单元区域形成为在与基底的上表面平行的方向之中的至少一个方向上不对称而增加。

[0005]

根据一些示例实施例,一种存储器装置包括:外围电路区域,包括第一基底和位于第一基底上的电路元件,电路元件包括行解码器;单元阵列区域,包括字线和沟道结构,字线堆叠在外围电路区域上的第二基底上,沟道结构在与第二基底的上表面垂直的方向上延伸并穿透字线;以及单元接触区域,包括单元接触件,单元接触件连接到字线并位于单元阵列区域的在与第二基底的上表面平行的第一方向上的两侧上,单元接触件包括第一单元接触区域和第二单元接触区域,第一单元接触区域和第二单元接触区域在第一方向上具有彼此不同的长度。第一单元接触区域和第二单元接触区域中的每个包括在第一方向上具有彼此不同的长度的第一垫以及与第一垫不同的第二垫,并且单元接触件在第一垫中连接到字线。包括在第一单元接触区域中的第二垫的数量比包括在第二单元接触区域中的第二垫的数量大。

[0006]

根据一些示例实施例,一种存储器装置包括:外围电路区域,包括位于第一基底上的传输元件;以及多个单元区域,位于外围电路区域上方的第二基底上,多个单元区域中的每个包括至少一个存储器块。多个单元区域中的每个包括单元阵列区域和单元连接区域,在单元阵列区域中,多条字线连接到传输元件并且多个沟道结构穿透字线,在单元连接区域中,从单元阵列区域延伸的字线连接到多个单元接触件。传输元件中的至少一个公共地连接到包括在单元接触件之中的彼此相邻的一对单元区域中的一对字线,并且所述一对字线位于距第二基底的上表面相同的水平上。

[0007]

根据一些示例实施例,一种存储器装置包括:外围电路区域,包括传输元件;以及多个单元区域,多个单元区域中的每个包括单元阵列区域,单元阵列区域包括堆叠在外围电路区域上方的基底上的字线和穿透字线的沟道结构。多个单元区域中的每个包括在与基

底的上表面平行的第一方向上彼此相邻的第一单元区域和第二单元区域以及在第一方向上彼此相邻的第三单元区域和第四单元区域。第一单元区域的单元阵列区域和第二单元区域的单元阵列区域之间的距离不同于第三单元区域的单元阵列区域和第四单元区域的单元阵列区域之间的距离。

附图说明

[0008]

通过以下结合附图进行的详细描述,将更清楚地理解本公开的上面的和其它的方面、特征和优点,在附图中:

[0009]

图1和图2是根据一些示例实施例的存储器装置的示意图;

[0010]

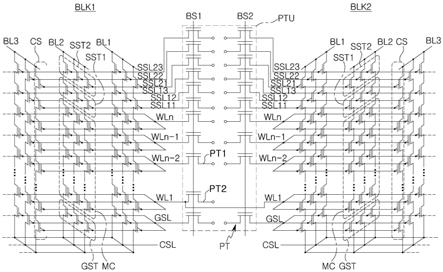

图3和图4示出了根据一些示例实施例的存储器装置中的存储器单元阵列与传输元件(pass element)之间的连接关系;

[0011]

图5是根据一些示例实施例的存储器装置的示意性平面图;

[0012]

图6a和图6b示出了图5中所示的存储器装置的区域;

[0013]

图7a和图7b示出了根据一些示例实施例的存储器装置的部分;

[0014]

图8a和图8b示出了根据一些示例实施例的存储器装置的区域;

[0015]

图9和图10示出了根据一些示例实施例的存储器装置的示意性构造;

[0016]

图11至图14是根据一些示例实施例的存储器装置的示意性平面图;

[0017]

图15是沿图11中的线i-i'截取的剖视图;

[0018]

图16是沿图11中的线ii-ii'截取的剖视图;

[0019]

图17是沿图12中的线iii-iii'截取的剖视图;

[0020]

图18a和图18b是图17中所示的传输元件的示意图;

[0021]

图19和图20是示出根据一些示例实施例的存储器装置的单元接触区域的剖视图;

[0022]

图21是示出根据一些示例实施例的存储器装置的单元阵列区域的剖视图;

[0023]

图22、图23a、图23b、图24a和图24b是图21中的区域的放大图;

[0024]

图25是示出根据一些示例实施例的存储器装置的单元阵列区域的剖视图;

[0025]

图26a、图26b、图27a和图27b是图25中的区域的放大图;以及

[0026]

图28是包括根据一些示例实施例的存储器装置的电子装置的示意性框图。

具体实施方式

[0027]

在下文中,将参照附图描述示例实施例。

[0028]

图1和图2是根据一些示例实施例的存储器装置的示意性框图。

[0029]

参照图1,存储器装置10可以包括存储器单元阵列20和外围电路30。外围电路30可以包括行解码器31、电压生成器32、页缓冲器33、输入/输出电路34、控制逻辑35等。存储器单元阵列20可以包括多个存储器单元,并且可以被划分为多个存储器块。多个存储器单元可以通过串选择线ssl、字线wl和地选择线gsl连接到行解码器31,并且通过位线bl连接到页缓冲器33。在示例实施例中,布置在同一行中的多个存储器单元可以连接到同一条字线wl,并且布置在同一列中的多个存储器单元可以连接到同一条位线bl。

[0030]

行解码器31可以对从控制逻辑35等接收的地址addr进行解码,以生成并传送用于驱动字线wl的电压。行解码器31可以响应于控制逻辑35的控制而将由电压生成器32生成的

字线电压输入到字线wl。作为示例,行解码器31可以通过传输元件单元31a的传输元件连接到字线wl,并且可以在传输元件单元31a的传输元件导通时将字线电压输入到字线wl。

[0031]

页缓冲器33通过位线bl连接到存储器单元阵列20,并且可以读取存储在存储器单元中的数据或将数据写入到存储器单元中。页缓冲器33可以包括列解码器和读出放大器。列解码器可以选择存储器单元阵列20的位线bl的至少部分,读出放大器可以在读取操作期间读取连接到由列解码器选择的位线的存储器单元的数据。

[0032]

输入/输出电路34可以在编程操作期间接收数据data并将接收到的数据data传送到页缓冲器33,并且可以在读取操作期间将由页缓冲器33从存储器单元阵列20读取的数据data输出到外部实体。输入/输出电路34可以将从外部存储器控制器接收的地址或指令传送到控制逻辑35。

[0033]

控制逻辑35可以控制行解码器31、电压生成器32、页缓冲器33等的操作。在一些示例实施例中,控制逻辑35可以根据从外部存储器控制器等传送的控制信号和外部电压来操作。

[0034]

电压生成器32可以使用外部输入电源电压来生成用于存储器装置10的操作的控制电压,例如,编程电压、读取电压、擦除电压、传输电压(pass voltage)等。由电压生成器32生成的电压可以被供应到外围电路30,或者可以通过行解码器31等输入到存储器单元阵列20。

[0035]

作为示例,在编程操作期间,编程电压可以被输入到选择的字线,所述选择的字线连接到将要向其写入数据的选择的存储器单元。比编程电压低的传输电压可以被输入到与未选择的存储器单元连接的字线,未选择的存储器单元包括在单个存储器单元串中且与选择的存储器单元共享沟道区。

[0036]

在一些示例实施例中,在读取操作期间,读取电压可以被输入到选择的字线,所述选择的字线连接到将要从其读取数据的选择的存储器单元,传输电压可以被输入到未选择的字线,所述未选择的字线连接到与选择的存储器单元共享沟道区的未选择的存储器单元。在存储器单元中的每个存储器单元存储具有多位的数据的一些示例实施例中,行解码器31可以将具有彼此不同的幅值的多个读取电压输入到选择的字线中。

[0037]

参照图2,存储器单元阵列20可以包括多个存储器块blk1至blkn。存储器块blk1至blkn中的每个可以包括在由第一方向(x轴方向)和第二方向(y轴方向)限定的平面上沿第三方向(z轴方向)堆叠的字线以及沿第三方向(z轴方向)延伸的沟道结构。字线和沟道结构可以提供三维地布置的存储器单元。存储器块blk1至blkn中的每个可以包括沿第一方向(x轴方向)或第二方向(y轴方向)延伸并且连接到沟道结构的位线。作为示例,在存储器单元阵列20中,存储器块blk1至blkn可以沿第一方向(x轴方向)和第二方向(y轴方向)布置。

[0038]

图3和图4示出了根据一些示例实施例的存储器装置中的存储器单元阵列与传输元件之间的连接关系。

[0039]

参照图3,单个存储器块blk可以包括多个存储器单元串cs,并且存储器单元串cs的至少部分可以共享字线wl1至wln和位线bl1至bl3。

[0040]

存储器单元串cs中的每个可以包括连接在第一串选择晶体管sst1和第二串选择晶体管sst2与地选择晶体管gst之间的多个存储器单元mc。第一串选择晶体管sst1和第二串选择晶体管sst2可以彼此串联连接。上覆的第二串选择晶体管sst2可以连接到位线bl1

至bl2中的一者。地选择晶体管gst可以连接到共源极线csl。

[0041]

多个存储器单元mc可以在第一串选择晶体管sst1和第二串选择晶体管sst2与地选择晶体管gst之间彼此串联连接。在示例实施例中,串选择晶体管sst1和sst2以及地选择晶体管gst的数量可以不同地改变。存储器单元串cs还可以包括至少一个虚设存储器单元。

[0042]

多个存储器单元mc的栅电极可以连接到字线wl1至wln。地选择晶体管gst的栅电极可以连接到地选择线gsl,第一串选择晶体管sst1和第二串选择晶体管sst2的栅电极可以连接到串选择线ssl11至ssl23(即,串选择线ssl11、ssl12、ssl13、ssl21、ssl22和ssl23)。

[0043]

字线wl1至wln、地选择线gsl和串选择线ssl11至ssl23可以连接到包括传输元件pt的传输元件单元ptu。传输元件pt可以通过块选择信号bs导通和截止。可以在传输元件pt导通的同时,通过输入到字线wl1至wln、地选择线gsl和串选择线ssl11至ssl23的电压s1至sn、gs和ss11至ss23(即,电压ss11、ss12、ss13、ss21、ss22和ss23)对多个存储器单元mc执行编程操作、读取操作、擦除操作等。在图3中所示的一些示例实施例中,连接到包括在存储器块blk中的字线wl1至wln的传输元件pt可以不被包括在另一存储器块中的字线共享。

[0044]

参照图4,第一存储器块blk1和第二存储器块blk2可以共享传输元件中的至少一个。在图4中所示的一些示例实施例中,传输元件单元ptu可以包括第一传输元件pt1和至少一个第二传输元件pt2,第二传输元件pt2可以被第一存储器块blk1和第二存储器块blk2的字线wl1至wln中的至少一者共享。参照图4,第二传输元件pt2可以公共地连接到第一存储器块blk1的第一字线wl1和第二存储器块blk2的第一字线wl1。

[0045]

连接到第一存储器块blk1的字线wl1至wln的传输元件可以通过第一块选择信号bs1导通和截止,连接到第二存储器块blk2的字线wl1至wln的传输元件可以通过第二块选择信号bs2导通和截止。在示例实施例中,第一块选择信号bs1和第二块选择信号bs2可以彼此相同或彼此不同。当第一块选择信号bs1和第二块选择信号bs2彼此相同时,包括在传输元件单元ptu中的传输元件可以同时导通或截止。因此,第一存储器块blk1和第二存储器块blk2可以同时被驱动。

[0046]

图5是根据一些示例实施例的存储器装置的示意性平面图。

[0047]

参照图5,根据一些示例实施例的存储器装置40可以包括多个单元区域50。多个单元区域50可以布置在基底41上。单元区域50中的每个可以包括在与基底41的上表面垂直的方向上堆叠的字线、在与基底41的上表面垂直的方向上延伸的沟道结构以及连接到字线的单元接触件等。

[0048]

单元区域50中的每个可以包括其中设置有沟道结构的单元阵列区域和从单元阵列区域延伸的单元接触区域,在单元接触区域中字线和单元接触件彼此连接。例如,单元接触区域可以沿与基底41的上表面平行的方向设置在单元阵列区域周围。因此,单元接触区域可以彼此相邻地设置在单元区域50之间的边界上。

[0049]

在根据图5中所示的示例实施例的存储器装置40中,外围电路区域可以设置在其上设置有单元区域50的基底41下方。外围电路区域可以包括用于驱动包括在单元区域50中的存储器单元的电路的至少部分,例如,行解码器、电压生成器、页缓冲器、输入/输出电路和控制逻辑。

[0050]

行解码器可以包括连接到单元区域50的字线的传输元件。在一些示例实施例中,

在包括在彼此不同的单元区域50中的字线之中,至少一条字线可以共享传输元件。设置在单元阵列区域周围的单元接触区域可以具有不对称结构,使得在包括在彼此相邻的单元区域50中的字线之中的至少一条字线可以共享传输元件。在下文中,将参照图6a和图6b进一步详细描述这点。

[0051]

图6a和图6b示出了图5中所示的存储器装置的区域。作为示例,图6a可以是图5中的区域a1的放大图,图6b可以是图5中的区域a2的放大图。参照图6a和图6b,存储器装置40可以包括竖直地堆叠的单元区域50和外围电路区域60。作为示例,单元区域50可以设置在外围电路区域60上方。

[0052]

单元区域50中的每个可以包括第一单元接触区域51、第二单元接触区域52以及设置在第一单元接触区域51与第二单元接触区域52之间的单元阵列区域53。单元阵列区域53可以包括彼此堆叠的字线、穿透字线的沟道结构等。第一单元接触区域51和第二单元接触区域52中的每个可以是其中从单元阵列区域53延伸的字线和单元接触件彼此连接的区域,并且可以在第一方向(x轴方向)上设置在单元阵列区域53的的两侧上。

[0053]

在一些示例实施例中,第一单元接触区域51和第二单元接触区域52可以具有在第一方向(x轴方向)上彼此不同的长度。例如,在第一方向(x轴方向)上,第一单元接触区域51的长度l1可以比第二单元接触区域52的长度l2大。

[0054]

参照示出图5中的区域a1的放大图的图6a,第一单元接触区域51可以在单元区域50之间彼此相邻。参照示出图5中的区域a2的放大图的图6b,第二单元接触区域52可以在单元区域50之间彼此相邻。因此,包括在存储器装置40中的彼此相邻的单元区域50中的单元阵列区域53之间的距离可以根据其位置而彼此不同。在图6a中所示的示例实施例中,单元阵列区域53之间的第一距离dc1可以比图6b中所示的示例实施例中的单元阵列区域53之间的第二距离dc2大。

[0055]

在一些示例实施例中,连接到字线的传输元件可以在第一单元接触区域51和第二单元接触区域52中的每个下方设置在外围电路区域60中。字线和传输元件可以通过设置在第一单元接触区域51和第二单元接触区域52中的单元接触件而彼此连接。在一些示例实施例中,连接到第二单元接触区域52中的字线的单元接触件的至少部分可以公共地连接到传输元件中的一个。因此,包括在外围电路区域60中的传输元件的数量可以减少,并且第二单元接触区域52的面积可以减小以增加存储器装置40的集成密度。

[0056]

图7a和图7b示出了根据一些示例实施例的存储器装置的部分。

[0057]

图7a可以是示出根据一些示例实施例的存储器装置的区域的剖视图,图7b可以是与图7a对应的等效电路图。作为示例,在参照图7a和图7b描述的示例实施例中,第一单元接触区域可以与如上面图6a中描述的彼此相邻的区域对应。

[0058]

首先参照图7a,存储器装置可以包括外围电路区域200和设置在外围电路区域200上方的单元区域100。外围电路区域200可以包括第一基底210、形成在第一基底210上的多个电路元件220、连接到电路元件220的下互连线230和下层间电介质240。下层间电介质240可以设置为覆盖电路元件220和下互连线230,并且可以包括诸如氧化硅、氮化硅等的绝缘材料。

[0059]

单元区域100可以包括第一单元区域100a和第二单元区域100b,第一单元区域100a和第二单元区域100b具有相同的结构。在下文中,将参照第一单元区域100a描述单元

区域100的结构。作为示例,第一单元区域100a和第二单元区域100b中的每个可以提供至少一个存储器块。

[0060]

第一单元区域100a可以包括设置在下层间电介质240上的第二基底110a。多条字线131a至136a(130a)可以在与第二基底110a的上表面垂直的第三方向(z轴方向)上堆叠在第二基底110a上。串选择线141a至142a(140a)和地选择线120a可以分别设置在字线130a上方和下方。沟道结构150a可以在第三方向上延伸以穿透字线130a、串选择线140a和地选择线120a。沟道结构150a可以包括数据存储层151a、沟道层152a、掩埋绝缘层153a等,沟道层152a可以通过位线接触件blc电连接到位线bl。在一些示例实施例中,位线bl可以在第二方向(y轴方向)上延伸。其中设置有沟道结构150a和位线bl的区域可以被定义为单元阵列区域ca。

[0061]

字线130a可以在第一方向(x轴方向)上延伸,并且可以连接到在第一方向上与单元阵列区域ca相邻的第一单元接触区域ct1中的多个单元接触件161a至164a(160a)。在一些示例实施例中,字线130a可以在第一方向和第二方向上以彼此不同的长度延伸,以提供垫pad1和pad2。单元接触件160a和字线130a可以在垫pad1上彼此连接。

[0062]

参照图7a,第一单元接触区域ct1可以包括第一垫pad1和具有与第一垫pad1的面积不同的面积的第二垫pad2。第二垫pad2中的每个可以具有比第一垫pad1中的每个的面积大的面积。在一些示例实施例中,第二垫pad2中的每个在第一方向上的长度可以比第一垫pad1中的每个在第一方向上的长度大。

[0063]

竖直过孔181a至184a(180a)可以设置在垫pad2的至少部分中,以穿过字线130a的部分和第二基底110a连接到外围电路区域200的下互连线230。其中设置有竖直过孔180a的垫pad2可以在第二方向上设置在与单元接触件160a和字线130a连接到的垫pad1的位置不同的位置中。

[0064]

竖直过孔180a可以通过上互连线170a连接到单元接触件160a。第二垫pad2、字线130a和设置在第二垫pad2下方的竖直过孔180a可以彼此电隔离。作为示例,竖直过孔180a可以穿过其中用于形成字线130的牺牲层未被去除而保留的区域延伸到下互连线230。

[0065]

图7b可以是图7a中所示的存储器装置的等效电路图。参照图7b,第一单元区域100a和第二单元区域100b中的每个可以包括存储器单元mc、地选择晶体管gst、第一串选择晶体管sst1、第二串选择晶体管sst2等。地选择晶体管gst可以连接到共源极线csl,第二串选择晶体管sst2可以连接到位线bl。

[0066]

在图7a和图7b中所示的示例实施例中,第一单元区域100a和第二单元区域100b可以不共享传输元件pt。参照图7b,连接到第一单元区域100a中的存储器单元mc、地选择晶体管gst、第一串选择晶体管sst1和第二串选择晶体管sst2的传输元件可以与第二单元区域100b隔离。

[0067]

连接到第一单元区域100a的传输元件pt可以由第一块选择信号bs1控制,连接到第二单元区域100b的传输元件pt可以由第二块选择信号bs2控制。根据第一块选择信号bs1和第二块选择信号bs2的设置,可以同时或独立地驱动第一单元区域100a和第二单元区域100b。

[0068]

图8a和图8b示出了根据一些示例实施例的存储器装置的区域。

[0069]

图8a可以是示出根据一些示例实施例的存储器装置的区域的剖视图,图8b可以是

与图8a对应的等效电路图。根据参照图8a和图8b描述的示例实施例的存储器装置可以与根据参照图7a和图7b描述的示例实施例的存储器装置相同。然而,图8a中所示的区域可以与图7a中所示的区域不同。作为示例,在根据参照图8a和图8b描述的一些示例实施例的存储器装置中,第二单元接触区域可以与如上面参照图6b描述的彼此相邻的区域对应。

[0070]

参照图8a,存储器装置可以包括外围电路区域200和设置在外围电路区域200上方的单元区域100。外围电路区域200可以包括第一基底210、形成在第一基底210上的多个电路元件220、连接到电路元件220的下互连线230、下层间电介质240等。外围电路区域200可以从图7a中所示的存储器装置的区域连续地延伸。

[0071]

单元区域100可以包括第二单元区域100b和第三单元区域100c,第二单元区域100b和第三单元区域100c可以具有与参照图7a描述的第一单元区域100a的结构相同的结构。将参照图8a中所示的第二单元区域100b详细地描述包括在单元区域100中的单元阵列区域ca和第二单元接触区域ct2。

[0072]

第二单元区域100b可以包括设置在下层间电介质240上的第二基底110b,多条字线131b至136b(130b)可以在与第二基底110b的上表面垂直的第三方向(z轴方向)上堆叠在第二基底110b上。串选择线141b至142b(140b)和地选择线120b可以分别设置在字线130b上方和下方。沟道结构150b可以在第三方向上延伸并且可以穿透字线130b、串选择线140b和地选择线120b。沟道结构150b可以包括数据存储层151b、沟道层152b、掩埋绝缘层153b等,沟道层152b可以通过位线接触件blc电连接到位线bl。在一些示例实施例中,位线bl可以在第二方向(y轴方向)上延伸。其中设置有沟道结构150b、位线bl等的区域可以被定义为单元阵列区域ca。

[0073]

字线130b可以在第一方向(x轴方向)上延伸,并且可以连接到在第一方向上与单元阵列区域ca相邻的第二单元接触区域ct2中的多个单元接触件161b至164b(160b)。在一些示例实施例中,字线130b可以在第一方向和第二方向上以彼此不同的长度延伸,以提供垫pad1和pad2。单元接触件160b和字线130b可以在垫pad1的部分上彼此连接。

[0074]

与参照图7a描述的第一单元接触区域ct1类似,第二单元接触区域ct2可以包括与第一垫pad1不同的至少一个第二垫pad2。第二垫pad2可以具有比第一垫pad1中的每个的面积大的面积。在一些示例实施例中,第二垫pad2在第一方向上的长度可以比第一垫pad1中的每个在第一方向上的长度大。

[0075]

参照图7a和图8a两者,第二单元区域100b中的第一单元接触区域ct1中包括的第二垫pad2的数量可以比第二单元区域100b中的第二单元接触区域ct2中包括的第二垫pad2的数量大。因此,第二单元接触区域ct2可以延伸为在第一方向上比第一单元接触区域ct1相对短,并且可以增加单元区域100a、100b和100c的集成密度。

[0076]

作为示例,彼此相邻的单元区域100b和100c可以共享传输元件中的至少一个,第二单元接触区域ct2插置在彼此相邻的单元区域100b和100c之间。参照图8a,电路元件220可以包括第一传输元件221和第二传输元件222。在包括在第二单元区域100b中的字线130b之中的字线130b的至少部分可以与包括在第三单元区域100c中的字线共享第二传输元件222。共享第二传输元件222的字线可以在第三方向上设置在相同的高度处。

[0077]

参照图8a,第二单元接触区域ct2可以包括共竖直过孔181b至183b(180b),共竖直过孔181b至183b(180b)使连接到第二传输元件222的下互连线连接到单元接触件160b之中

的一些单元接触件161b至163b。共竖直过孔180b可以通过共上互连线171b至173b(170b)公共地连接到第二单元区域100b和第三单元区域100c的字线的至少部分。共上互连线171b至173b可以在第二方向上设置在彼此不同的位置中以彼此电隔离。共竖直过孔180b可以在不穿透第二基底110b的情况下延伸到外围电路区域200。

[0078]

在单元接触件160b之中,某些单元接触件164b可以通过单独的竖直过孔191b连接到外围电路区域200的第一传输元件221。单独的竖直过孔191b可以通过单独的上互连线192b连接到单元接触件164b。作为示例,单独的竖直过孔191b可以从垫pad2中的至少一个延伸到外围电路区域200。

[0079]

如图8a中所示,在第二单元接触区域ct2中,包括在相邻的单元区域100b和100c中的字线的部分可以连接到共竖直过孔180b以共享第二传输元件222。因此,用于使单独的竖直过孔191b延伸到外围电路区域200的第二垫pad2的数量可以减少,第二单元接触区域ct2的面积可以减小以增加存储器装置100的集成密度。此外,在一些实施例中,包括在第一单元接触区域ct1中的第一垫pad1和第二垫pad2的面积之和比包括在第二单元接触区域ct2中的第一垫pad1和第二垫pad2的面积之和大。另外,在一些实施例中,包括在第一单元接触区域ct1中的第一垫pad1的数量和第二垫pad2的数量之和比包括在第二单元接触区域ct2中的第一垫pad1的数量和第二垫pad2的数量之和大。

[0080]

图8b可以是图8a中所示的存储器装置的等效电路图。参照图8b,第二单元区域100b和第三单元区域100c中的每个可以包括存储器单元mc、地选择晶体管gst、第一串选择晶体管sst1、第二串选择晶体管sst2等。地选择晶体管gst可以连接到共源极线csl,第二串选择晶体管sst2可以连接到位线bl。

[0081]

可以根据连接到存储器单元mc的传输元件pt1和pt2是否公共地连接到第二单元区域100b和第三单元区域100c而将传输元件pt1和pt2划分为第一传输元件pt1和第二传输元件pt2。例如,第一传输元件pt1可以连接到第二单元区域100b和第三单元区域100c中的任何一者的存储器单元mc,第二传输元件pt2可以公共地连接到包括在第二单元区域100b和第三单元区域100c中的存储器单元mc的部分。

[0082]

当对第三单元区域100c执行控制操作时,可以使用第一块选择信号bs1使第二传输元件pt2导通。然而,可以通过控制通过连接到第二单元区域100b的第一传输元件pt1输入到第二单元区域100b的电压来彼此独立地驱动第二单元区域100b和第三单元区域100c。在示例实施例中,可以同时驱动第二单元区域100b和第三单元区域100c。

[0083]

图9和图10示出了根据一些示例实施例的存储器装置的示意性构造。

[0084]

首先参照图9,存储器装置300可以包括外围电路区域p以及单元区域c1和c2。存储器装置300可以具有其中单元区域c1和c2设置在外围电路区域p上方的外围上单元(cop)结构。例如,单元区域c1和c2可以沿第三方向(z轴方向)设置在外围电路区域p上方。外围电路区域p可以包括形成在第一基底301上的多个电路元件,并且可以被划分为第一外围电路区域p1和第二外围电路区域p2。

[0085]

单元区域c1和c2可以包括设置在第一方向(x轴方向)上的第一单元区域c1和第二单元区域c2。第一单元区域c1和第二单元区域c2可以分别形成在彼此不同的第二基底302和303中。第一单元区域c1和第二单元区域c2中的每个可以包括单元阵列区域ca、设置在单元阵列区域ca的在第一方向上的两侧上的第一单元接触区域ct1、以及第二单元接触区域

ct2。第一单元区域c1和第二单元区域c2可以具有相同的结构,并且可以设置为相对于第一单元区域c1与第二单元区域c2之间的边界水平地对称或者基本上对称。

[0086]

参照第一单元区域c1,单元阵列区域ca可以包括在第二方向(y轴方向)上划分的第一存储器块blk1和第二存储器块blk2。作为示例,第一存储器块blk1和第二存储器块blk2可以由在第一方向上延伸的字线切割区域划分。

[0087]

第一存储器块blk1的字线可以在第一方向上延伸以提供包括在第一单元接触区域ct1中的第一连接区域cr1和包括在第二单元接触区域ct2中的第二连接区域cr2。另外,第二存储器块blk2的字线可以在第一方向上延伸以提供包括在第二单元接触区域ct2中的第一连接区域cr1和包括在第一单元接触区域ct1中的第二连接区域cr2。

[0088]

第一连接区域cr1和第二连接区域cr2可以包括由字线提供的第一垫和第二垫。在第一连接区域cr1中,第一垫和第二垫可以在第一方向和第二方向上形成台阶,也就是说,它们可以在剖面方向上具有不同的深度。在第二连接区域cr2中,第一垫和第二垫可以在第一方向上形成台阶。在一些示例实施例中,第一垫中的每个可以在第一方向上比第二垫中的每个短。

[0089]

在示例中,第一存储器块blk1的字线可以连接到第一单元接触区域ct1的第一连接区域cr1中的多个单元接触件。在第一单元接触区域ct1的第一连接区域cr1中的连接到第一存储器块blk1的字线的单元接触件的至少部分可以连接到在第一单元接触区域ct1的第二连接区域cr2中的第一外围电路区域p1的传输元件。

[0090]

连接到传输元件的多个竖直过孔可以设置在第一单元接触区域ct1的第二连接区域cr2中的第一垫和第二垫的至少部分中。在一些示例实施例中,竖直过孔可以通过在第二方向上延伸的上互连线连接到在第一单元接触区域ct1的第一连接区域cr1中连接到第一存储器块blk1的字线的单元接触件的至少部分。

[0091]

在第二单元接触区域ct2的第一连接区域cr1中连接到第一存储器块blk1的字线的单元接触件可以连接到在第二单元接触区域ct2的第二连接区域cr2中的第一外围电路区域p1的传输元件或者第一单元区域c1与第二单元区域c2之间的边界区域中的第一外围电路区域p1的传输元件。连接到传输元件的多个竖直过孔可以设置在第二单元接触区域ct2的第二连接区域cr2和边界区域ba中。

[0092]

在多个竖直过孔之中,设置在第二单元接触区域ct2的第二连接区域cr2中的竖直过孔可以通过设置在第一单元区域c1上方的上互连线连接到单元接触件的至少部分,所述单元接触件连接到在第二单元接触区域ct2的第一连接区域cr1中的第二存储器块blk2的字线。在竖直过孔之中,设置在边界区域ba中的竖直过孔可以通过设置在第一单元区域c1上方的上互连线连接到在第二单元接触区域ct2的第一连接区域cr1中连接到第二存储器块blk2的字线的单元接触件。

[0093]

设置在边界区域ba中的竖直过孔可以公共地连接到第二存储器块blk2的字线的部分和第四存储器块blk4的字线的部分。第二存储器块blk2和第四存储器块blk4的字线的部分可以通过设置在边界区域ba中的竖直过孔共享传输元件。因此,在与边界区域ba相邻的第二单元接触区域ct2中的第二垫pad2的数量可以减少,第一单元区域c1和第二单元区域c2之间的距离可以减小以增加存储器装置300的集成密度。

[0094]

在图9中所示的示例实施例中,设置在第二单元接触区域ct2下方的传输元件的部

分可以被包括在不同的存储器块blk1至blk4中的字线共享。因此,设置在第一单元接触区域ct1下方的传输元件的数量可以比设置在第二单元接触区域ct2下方的传输元件的数量大。

[0095]

参照图10,存储器装置300a可以包括外围电路区域p以及单元区域c1和c2。外围电路区域p以及单元区域c1和c2的构造可以与参照图9描述的外围电路区域p以及单元区域c1和c2的构造类似。然而,第一单元区域c1和第二单元区域c2可以一起形成在一个第二基底302上。因此,形成在边界区域ba中的竖直过孔可以通过第二基底302连接到第一外围电路区域p1的传输元件。在边界区域ba中,基底绝缘层可以被设置为使竖直过孔和第二基底302彼此电隔离。

[0096]

图11至图14是根据一些示例实施例的存储器装置的示意性平面图。图15是沿图11中的线i-i'截取的剖视图,图16是沿图11中的线ii-ii'截取的剖视图。图17是沿图12中的线iii-iii'截取的剖视图,图18a和图18b是图17中所示的传输元件的示意图。

[0097]

参照图11和图12,存储器装置400可以包括第一存储器块410和第二存储器块420。第一存储器块410和第二存储器块420中的每个可以包括单元阵列区域ca以及设置在单元阵列区域ca的在第一方向(x轴方向)上的两侧上的第一单元接触区域ct1和第二单元接触区域ct2。第一存储器块410和第二存储器块420可以在第二方向(y轴方向)上彼此相邻。

[0098]

第一单元接触区域ct1和第二单元接触区域ct2中的每个可以包括第一连接区域cr1和第二连接区域cr2。参照图11和图12,第一存储器块410的第一单元接触区域ct1可以提供第一连接区域cr1,第一存储器块410的第二单元接触区域ct2可以提供第二连接区域cr2。第二存储器块420的第一单元接触区域ct1可以提供第二连接区域cr2,第二存储器块420的第二单元接触区域ct2可以提供第一连接区域cr1。

[0099]

第一垫pad1和第二垫pad2可以形成在第一连接区域cr1和第二连接区域cr2中。在第一连接区域cr1中,第一垫pad1和第二垫pad2在第一方向和第二方向上形成台阶。在第二连接区域cr2中,第一垫pad1和第二垫pad2可以在第一方向上形成台阶。

[0100]

第二垫pad2中的每个可以具有比第一垫pad1中的每个的面积大的面积。作为示例,第二垫pad2可以在第一方向上延伸为比第一垫pad1长。图11和图12中所示的第一垫pad1和第二垫pad2可以是示例实施例,第一垫pad1和第二垫pad2的长度可以不同地改变。作为示例,第二垫pad2中的每个在第一方向上的长度可以是第一垫pad1中的每个在第一方向上的长度的至少10倍。

[0101]

第一存储器块410和第二存储器块420可以包括在第三方向(z轴方向)上堆叠的多条字线wl。在单元阵列区域ca中,多个沟道结构ch可以设置为在第三方向上延伸并且穿透字线wl。多条字线wl可以通过字线切割部wc被划分为第一存储器块410和第二存储器块420。

[0102]

第一切割线cl1和第二切割线cl2可以在第二方向上设置在彼此最靠近的字线切割部wc之间。第一切割线cl1可以形成在单元阵列区域ca以及单元接触区域ct1和ct2中,而第二切割线cl2可以仅形成在单元接触区域ct1和ct2中。在图11和图12中所示的示例实施例中,第二切割线cl2可以不形成在第二连接区域cr2中。

[0103]

在形成在第一连接区域cr1中的第一垫pad1和第二垫pad2中,字线wl可以连接到单元接触件cc。单元接触件cc的至少部分可以连接到形成在第二连接区域cr2中的多个竖

直过孔vv的至少部分。在单元阵列区域ca中,竖直过孔vv可以连接到单元阵列区域ca以及在单元接触区域ct1和ct2下方的电路元件。作为示例,竖直过孔vv可以连接到设置在单元接触区域ct1和ct2下方的传输元件。竖直过孔vv的数量和布置不限于图11和图12中所示的数量和布置,竖直过孔vv可以不同地设置在第二连接区域cr2中。可以考虑字线wl的布线来确定竖直过孔vv的数量和布置。

[0104]

如上所述,在第一切割线cl1和第二切割线cl2之中,第二切割线cl2可以不形成在第二连接区域cr2中。因此,可以在第二连接区域cr2的部分中不执行通过用于形成字线切割部wc以及第一切割线cl1和第二切割线cl2的沟槽引入磷酸以用字线wl替换牺牲层的工艺。竖直过孔vv可以在其中未形成字线wl并且保留牺牲层的区域中沿第三方向延伸,以连接到下面的传输元件。

[0105]

参照图11,第一单元接触区域ct1可以包括在第一方向上布置的五个第二垫pad2。参照图12,第二单元接触区域ct2可以包括在第一方向上布置的三个第二垫pad2。因此,第一存储器块410和第二存储器块420可以具有在第一方向上关于单元阵列区域ca不对称的结构。

[0106]

参照图11和图12,在包括在第一单元接触区域ct1中的第二垫pad2之中,考虑到连接到字线wl的单元接触件cc和连接到单元接触件cc的竖直过孔vv的布线,在第二连接区域cr2中可以省略远离单元阵列区域ca的第二垫pad2的部分。在一些示例实施例中,当沟道结构ch包括在第三方向上彼此连接的下沟道结构和上沟道结构时,包括在第二单元接触区域ct2中的第二垫pad2可以仅由上沟道结构穿透其的上字线提供。例如,下沟道结构穿透其的下字线可以仅提供第一垫pad1。

[0107]

由于包括在第二单元接触区域ct2中的第二垫pad2的数量比包括在第一单元接触区域ct1中的第二垫pad2的数量小,因此需要设置竖直过孔vv以使单元接触件cc和传输元件彼此连接的附加方法。在一些示例实施例中,竖直过孔vv可以设置在沿第一方向彼此相邻的第二单元接触区域ct2之间,以连接到单元接触件cc。设置在沿第一方向彼此相邻的第二单元接触区域ct2之间的传输元件可以公共地连接到彼此不同的存储器块的字线之中的字线的至少部分,以解决单元接触件cc和传输元件的连接问题。在下文中,将参照图13和图14对此进行描述。

[0108]

参照图13和图14,存储器装置400可以包括第一存储器块410至第四存储器块440。第一存储器块410的第一连接区域cr1和第三存储器块430的第一连接区域cr1可以在第一方向上彼此相邻,第二存储器块420的第二连接区域cr2和第四存储器块440的第二连接区域cr2可以在第一方向上彼此相邻。

[0109]

传输元件pt1和pt2可以设置在具有第一存储器块410和第二存储器块420的第一单元区域400a与具有第三存储器块430和第四存储器块440的第二单元区域400b之间。传输元件pt1和pt2可以形成在设置在单元区域400a和400b下方的外围电路区域中,并且可以包括第一传输元件pt1和第二传输元件pt2。

[0110]

第一传输元件pt1的至少部分可以包括第一存储器块410的字线wl的至少部分以及第三存储器块430的字线wl的至少部分。第二传输元件pt2可以设置在第一单元区域400a的第二连接区域cr2与第二单元区域400b的第二连接区域cr2之间,以降低使字线wl的至少部分和第二传输元件pt2彼此连接的互连线的复杂性。

[0111]

在图13中所示的示例实施例中,第一单元区域400a和第二单元区域400b可以设置在不同的第二基底401a和401b上。同时,在图14中所示的示例实施例中,第一单元区域400a和第二单元区域400b可以设置在一个第二基底401上。因此,在图14中所示的示例实施例中,连接到第二传输元件pt2的竖直过孔vv可以穿透第二基底401。在一些示例实施例中,基底绝缘层403可以形成在第二基底401上,使得竖直过孔vv和第二基底401彼此隔离。图15可以是沿图11中的线i-i'截取的剖视图。一起参照图11、图15和图16,存储器装置400可以包括外围电路区域p和在外围电路区域p上方的单元区域c。外围电路区域p可以包括第一基底405和形成在第一基底405上的电路元件。例如,电路元件可以是包括在行解码器中且电连接到字线wl的传输元件406,并且电路元件可以被下层间电介质408覆盖。

[0112]

单元区域c可以形成在下层间电介质408上的第二基底401中。在图15中,沿图11中的线i-i'截取的剖面可以与存储器装置400的第二连接区域cr2对应。可以不形成第二切割线cl2并且可以在第二连接区域cr2中不去除而保留牺牲层sl。因此,如图15中所示,牺牲层sl和绝缘层il可以交替地堆叠在第二基底401上。牺牲层sl和绝缘层il可以包括彼此不同的绝缘材料。

[0113]

在第二连接区域cr2中,牺牲层sl和绝缘层il可以提供第一垫pad1和第二垫pad2。在第一方向(x轴方向)上,第一垫pad1中的每个的长度d1可以比第二垫pad2中的每个的长度小。竖直过孔vv可以形成在第二垫pad2中,并且可以延伸到外围电路区域p以连接到传输元件406。在竖直过孔vv穿透其的区域中,第二基底401可以由绝缘材料形成。

[0114]

图16可以是沿图11中的线ii-ii'截取的剖视图,图17可以是沿图12中的线iii-iii'截取的剖视图。参照图11和图12,图16可以是示出第一单元接触区域ct1的第二连接区域cr2的部分的剖视图,图17可以是示出第二单元接触区域ct2的第二连接区域cr2的部分的剖视图。

[0115]

在一些示例实施例中,第一单元接触区域ct1的第二连接区域cr2和第二单元接触区域ct2的第二连接区域cr2可以具有彼此不同的结构。参照图16和图17,第一单元接触区域ct1的第二连接区域cr2和第二单元接触区域ct2的第二连接区域cr2可以在距第二基底401的上表面特定高度处或更小的高度处具有彼此不同的结构。这种结构上的差异可以由包括在第一单元接触区域ct1的第二连接区域cr2中的第二垫pad2的数量与包括在第二单元接触区域ct2的第二连接区域cr2中的第二垫pad2的数量之间的差异引起。

[0116]

在一些示例实施例中,包括在第一单元接触区域ct1的第二连接区域cr2中的第二垫pad2的数量可以比包括在第二单元接触区域ct2的第二连接区域cr2中的第二垫pad2的数量大。由于第一单元接触区域ct1的第二连接区域cr2可以比第二单元接触区域ct2的第二连接区域cr2包括更多的数量的第二垫pad2,所以第一单元接触区域ct1可以在第一方向上延伸为比第二单元接触区域ct2长。因此,延伸到单元阵列区域ca的第一单元接触区域ct1(第一侧)的字线wl中的至少一条字线在第一方向上的长度可以与延伸到单元阵列区域ca的第二单元接触区域ct2(第二侧)的字线wl中的至少一条字线在第一方向上的长度不同。例如,最下面的字线wl可以在第一方向上延伸为比第一单元接触区域ct1中的第二单元接触区域ct2长。

[0117]

作为示例,包括在第一单元接触区域ct1的第二连接区域cr2中的第二垫pad2的数量与包括在第二单元接触区域ct2的第二连接区域cr2中的第二垫pad2的数量之间的差可

以是两个或更多个。在一些示例实施例中,第二单元接触区域ct2在第一方向上的长度可以大于第一单元接触区域ct1在第一方向上的长度的0.6倍且小于第一单元接触区域ct1在第一方向上的长度的0.9倍。在一些示例实施例中,第二垫pad2中的每个在第一方向上的长度可以大于或等于第一垫pad1中的每个在第一方向上的长度的十倍。与第一单元接触区域ct1相比,包括在单元接触区域ct2中的第二垫pad2的数量可以减少两个或更多个,以获得上述长度减小效果。

[0118]

参照图17,传输元件406和407可以包括第一传输元件406和第二传输元件407。第二传输元件407可以在第一方向上设置在第二单元接触区域ct2的第二连接区域cr2的外侧,并且可以包括穿过竖直过孔vv的至少两条字线wl。第二传输元件407可以连接到两条或更多条字线wl,包括在第二单元接触区域ct2的第二连接区域cr2中的第二垫pad2的数量可以减小。因此,可以增加存储器装置400的集成密度。

[0119]

由于第二传输元件407可以连接到两条或更多条字线wl以同时驱动两条或更多条字线wl,所以第二传输元件407可以具有与第一传输元件406的形状或/和尺寸不同的形状或/和尺寸。参照图18a和图18b,第一传输元件406和第二传输元件407中的每个可以包括栅极g以及在与栅极g相邻的相对侧上的源区s和漏区d。作为示例,第二传输元件407的栅极长度lg2可以比第一传输元件406的栅极长度lg1大。在一些示例实施例中,第二传输元件407的源区s和漏区d在第二方向上的长度h2可以比第一传输元件406的源区s和漏区d在第二方向上的长度h1大。在示例实施例中,第二传输元件407具有大于或等于第一传输元件406的面积的面积。

[0120]

图19和图20是示出根据一些示例实施例的存储器装置的单元接触区域的剖视图。

[0121]

参照图19,存储器装置500可以包括在第三方向(z轴方向)上堆叠的外围电路区域p和单元区域c。外围电路区域p可以包括第一基底505、形成在第一基底505上的电路元件506和507、覆盖电路元件506和507的下层间电介质508等。作为示例,电路元件506和507可以是包括在行解码器中的传输元件。

[0122]

单元区域c可以包括第一单元区域500a和第二单元区域500b。另外,单元区域c可以包括多个第二基底501a和501b以及堆叠在多个第二基底501a和501b上的多个牺牲层sl和多个绝缘层il。牺牲层sl和绝缘层il可以在第一方向(x轴方向)和第二方向(y轴方向)上提供台阶,可以通过台阶形成第一垫pad1和第二垫pad2。第一垫pad1中的每个可以在第一方向上具有比第二垫pad2中的每个的长度短的长度。

[0123]

在图19中所示的示例实施例中,牺牲层sl可以是在形成字线的工艺中保留而未被去除的层。牺牲层sl可以保留在其中形成有多个竖直过孔vv的区域中。在其中没有形成竖直过孔vv的区域中,牺牲层sl可以被字线替代。竖直过孔vv可以通过牺牲层sl和绝缘层il连接到传输元件506和507。

[0124]

作为示例,竖直过孔vv中的至少一个可以通过第二垫pad2中的牺牲层sl和绝缘层il连接到第一传输元件506。竖直过孔vv中的至少一个可以在第一单元区域500a的第二基底501a与第二单元区域500b的第二基底501b之间的边界区域ba中连接到第二传输元件507。

[0125]

第二传输元件507可以通过竖直过孔vv、上互连线uw和单元接触件cc连接到包括在第一单元区域500a和第二单元区域500b中的一对字线。作为示例,所述一对字线可以在

第三方向上设置在相同高度处。在图19中所示的示例实施例中,一对字线可以在第二方向上设置在牺牲层sl的后方。

[0126]

参照图20,存储器装置600可以包括外围电路区域p和单元区域c。外围电路区域p和单元区域c的构造可以与上面参照图19描述的存储器装置500的构造类似。例如,单元区域c可以包括在第一方向上彼此相邻的第一单元区域600a和第二单元区域600b。

[0127]

在图20中所示的示例实施例中,第一单元区域600a和第二单元区域600b可以设置在一个第二基底601上。例如,第二基底601可以从第一单元区域600a延伸到第二单元区域600b。竖直过孔vv中的至少一个可以穿透形成在第一单元区域600a与第二单元区域600b之间的边界区域ba中的基底绝缘层603,以延伸到外围电路区域p。

[0128]

存储器装置500和600中的每条字线可以具有与每个牺牲层sl基本上相同的厚度。每个存储器单元的栅极长度可以由每条字线的厚度确定,每个存储器单元的特性可以根据每条字线的厚度而变化。在示例实施例中,每条字线的厚度可以根据每条字线是独立地连接到第一传输元件506和606还是与其它字线中的至少一条共享第二传输元件507和607等而变化,其中字线在第三方向上布置在单元区域c中。

[0129]

图21是示出根据一些示例实施例的存储器装置的单元阵列区域的剖视图。

[0130]

参照图21,存储器装置700可以包括外围电路区域p和单元区域c,单元区域c可以设置在外围电路区域p上方。外围电路区域p包括第一基底701、形成在第一基底701上的电路元件702、连接到电路元件702的下互连线703、下层间电介质704等。作为示例,电路元件702可以提供页缓冲器等。

[0131]

单元区域c可以包括堆叠在第二基底710上的字线wl、穿透字线wl的沟道结构ch(见图22)以及将字线wl划分为多个区域的字线切割部wc。字线wl可以与绝缘层il交替地堆叠,并且可以在第一方向(x轴方向)和第二方向(y轴方向)上延伸以形成具有台阶的垫。如上面在各种实施例中所描述的,垫可以包括第一垫和第二垫,并且第一垫中的每个可以在第一方向上具有比第二垫中的每个的长度短的长度。作为示例,图21中所示的存储器装置700可以包括上面参照图11和图12描述的第一单元接触区域和第二单元接触区域,并且第一单元接触区域和第二单元接触区域可以设置在单元区域c在第一方向上的两侧上。

[0132]

沟道结构ch可以通过位线接触件blc连接到位线bl。在图21中,设置在第一方向上的相同位置中的沟道结构ch被示出为连接到一条位线bl。然而,沟道结构ch的位置不限于此。位线接触件blc可以穿透上层间电介质705以使沟道结构ch和位线bl彼此连接。

[0133]

第二基底710可以包括第一层711至第三层713。设置在字线切割部wc之间的沟道结构ch可以通过第一层711至第三层713彼此连接以连接到单个共源极线。在下文中,将参照图22、图23a、图23b、图24a和图24b进一步详细地描述图21中所示的存储器装置700。

[0134]

图22、图23a、图23b、图24a和图24b是图21中的区域的放大图。

[0135]

图22可以是图21中的区域b的放大图。参照图22,第二基底710可以包括第一层711至第三层713。沟道结构ch可以包括数据存储层720、沟道层730、掩埋绝缘层740等。

[0136]

第二基底710的第一层711至第三层713中的每个可以包括掺杂有具有第一导电类型的杂质的多晶硅。作为示例,第一层711至第三层713可以掺杂有n型杂质。参照图21,在包括在第二基底710中的第一层711至第三层713之中,第三层713和第二层712可以在第二方向上通过字线切割部wc彼此隔离。因此,设置在沿第二方向彼此相邻的一对字线切割部wc

之间的沟道结构ch可以通过第二基底710彼此连接。

[0137]

数据存储层720可以包括多个层721至723。作为示例,数据存储层720可以包括阻挡层721、电荷存储层722和隧穿层723。包括在数据存储层720中的层721至723的数量、设置顺序、材料可以不同地改变。沟道层730可以由半导体材料(例如,多晶硅等)形成,可以用诸如氧化硅等的掩埋绝缘层740填充沟道层730的内部空间。

[0138]

图23a和图23b可以是图21中的区域c1和c2的放大图。参照图23a和图23b,沟道结构ch可以穿透字线wl和绝缘层il,字线wl和绝缘层il可以被字线切割部wc划分为多个区域。

[0139]

在根据图21中所示的示例实施例的存储器装置700中,沟道结构ch和字线切割部wc可以具有其宽度在朝向第二基底710的第三方向(z方向)上减小的形状。例如,沟道结构ch和字线切割部wc在剖面上的侧表面可以不与第二基底710的上表面完全垂直,并且可以具有平缓地倾斜的形状。参照图23a和图23b,字线切割部wc在设置在相对较高位置中的区域c1中具有第一宽度y1,并且在设置在相对较低位置中的区域c2中具有比第一宽度y1小的第二宽度y2。

[0140]

因此,如图23a和图23b中所示,设置在区域c1中的字线wl的第一宽度w1可以比设置在区域c2中的字线wl的第二宽度w2小。由于宽度的差异,区域c1中的字线wl的电阻可以比区域c2中的字线wl的电阻高。在一些示例实施例中,可以考虑字线wl之间的电阻差来确定字线wl与传输元件之间的连接关系。

[0141]

根据一些示例实施例的存储器装置700可以包括设置在外围电路区域p中的第一传输元件和第二传输元件,第二传输元件中的每个可以连接到至少两条字线wl。如上所述,第二传输元件中的每个可以被彼此不同的单元区域中的设置在相同高度处的字线wl共享。另一方面,第一传输元件中的每个可以连接到单条字线wl。

[0142]

在一些示例实施例中,第二传输元件可以连接到具有相对较低的电阻的字线wl。例如,在图23a和图23b中所示的示例实施例中,区域c1中的具有相对较高的电阻的字线wl可以连接到第一传输元件,区域c2中的具有相对较低的电阻的字线wl可以连接到第二传输元件。在存储器装置700的一个单元区域c中,连接到第一传输元件的字线wl的数量可以比连接到第二传输元件的字线wl的数量大。

[0143]

在一些示例实施例中,字线wl的至少部分可以形成为具有彼此不同的厚度,以减小字线wl的电阻特性偏差。参照图24a和图24b,区域c1中的字线wl可以形成为具有第一厚度t1,区域c2中的字线wl可以形成为具有第二厚度t2。第一厚度t1可以比第二厚度t2高。

[0144]

因此,在图24a和图24b中所示的示例实施例中,区域c1中的字线wl的电阻与区域c2中的字线wl的电阻之间的差异可以减小。根据需要,区域c1中的字线wl也可以连接到第二传输元件。作为示例,区域c1中的字线wl可以连接到第二传输元件,并且区域c2中的字线wl可以连接到第一传输元件。

[0145]

可选地,与图24a和图24b中所示的示例实施例相比,区域c2中的字线wl中的每条可以形成为具有比区域c1中的字线wl中的每条的厚度高的厚度,区域c2中的字线wl可以连接到第二传输元件。由于区域c2中的连接到第二传输元件的字线wl的电阻减小,所以第二传输元件的负载可以减小,并且根据示例实施例,第二传输元件可以形成为具有与第一传输元件的尺寸相同的尺寸。

[0146]

图25是示出根据一些示例实施例的存储器装置的单元阵列区域的剖视图。

[0147]

参照图25,存储器装置800可以包括外围电路区域p和单元区域c,单元区域c可以设置在外围电路区域p上方。外围电路区域p的构造可以与参照图21描述的存储器装置700中的外围电路区域p的构造类似。

[0148]

单元区域c可以包括堆叠在第二基底810上的字线lwl、dwl和uwl,穿透字线lwl、dwl和uwl的沟道结构ch,以及将字线lwl、dwl和uwl划分为多个区域的字线切割部wc。第二基底810可以包括第一层811至第三层813,可以根据参照图22描述的内容来理解第二基底810的构造。

[0149]

字线lwl、dwl和uwl可以包括下字线lwl、至少一条虚设字线dwl和上字线uwl。下字线lwl可以从第二基底810的上表面堆叠,从第二基底810的上表面延伸的下沟道结构ch2可以穿透下字线lwl。上字线uwl可以堆叠在下字线lwl上,从下沟道结构ch2延伸的上沟道结构ch1可以穿透上字线uwl。

[0150]

虚设字线dwl可以设置在下字线lwl与上字线uwl之间。作为示例,上沟道结构ch1与下沟道结构ch2之间的边界区域可以掩埋在虚设字线dwl中。根据示例实施例,可以在不同的位置中添加另一虚设字线dwl。

[0151]

在根据图25中所示的示例实施例的存储器装置800中,可以通过将沟道结构ch划分为上沟道结构ch1和下沟道结构ch2来形成沟道结构ch。另一方面,字线切割部wc可以一次形成。因此,在与第一方向(x轴方向)和第二方向(y轴方向)平行的平面中,上字线uwl中的每条可以具有比下字线lwl中的每条的面积小的面积,并且上字线uwl的电阻可以增大。在下文中,将参照图26a至图27b进一步详细地描述这一点。

[0152]

图26a、图26b、图27a和图27b是图25中的区域的放大图。

[0153]

图26a和图26b可以是图25中的区域e1和e2的放大图。参照图26a,上沟道结构ch1可以穿透上字线uwl和绝缘层il,上字线uwl和绝缘层il可以被字线切割部wc划分为多个区域。类似地,参照图26b,下沟道结构ch2可以穿透下字线lwl和绝缘层il,下字线lwl和绝缘层il可以被字线切割部wc划分为多个区域。

[0154]

上沟道结构ch1和下沟道结构ch2中的每者可以包括数据存储层820、沟道层830、掩埋绝缘层840等。数据存储层820可以包括阻挡层821、电荷存储层822、隧穿层823等。

[0155]

作为示例,从上沟道结构ch1的下表面到区域e1的高度可以与从下沟道结构ch2的下表面到区域e2的高度相同。因此,上沟道结构ch1和下沟道结构ch2可以在区域e1和e2中的每个中具有基本上相同的尺寸。然而,字线切割部wc可以在一个工艺中形成在整个单元区域c中,字线切割部wc的宽度可以在朝向第二基底810的方向上逐渐减小。参照图26a和图26b,区域e1中的字线切割部wc的第一宽度y1可以比区域e2中的字线切割部wc的第二宽度y2大。

[0156]

因此,区域e1中的上字线uwl的第一宽度w1可以比区域e2中的下字线lwl的第二宽度w2小,上字线uwl可以具有比下字线lwl的电阻相对高的电阻。在一些示例实施例中,考虑到电阻特性,上字线uwl可以连接到第一传输元件,下字线lwl的至少部分可以连接到第二传输元件。第一传输元件中的每个可以是连接到上字线uwl和下字线lwl中的一条的元件,第二传输元件中的每个可以是连接到彼此不同的两条或更多条下字线lwl的元件。连接到第二传输元件中的每个的两条或更多条下字线lwl可以包括在彼此不同的单元区域c中。

[0157]

在图27a和图27b中所示的示例实施例中,上字线uwl的至少部分可以具有比下字线lwl的厚度高的厚度。参照图27a和图27b,每条上字线uwl可以具有第一厚度t1,每条下字线lwl可以具有比第一厚度t1小的第二厚度t2。因此,上字线uwl的电阻可以减小,并且根据需要,上字线uwl可以连接到第二传输元件。上字线uwl和下字线lwl的厚度可以不同地改变。例如,可以增加连接到第二传输元件的下字线lwl的厚度,以减小第二传输元件的负载并改善驱动特性。

[0158]

图28是包括根据一些示例实施例的存储器装置的电子装置的示意性框图。

[0159]

根据图28中所示的示例实施例的电子装置1000可以包括显示器1010、传感器单元1020、存储器1030、通信单元1040、处理器1050、端口1060等。电子装置1000还可以包括电源、输入/输出装置等。在图28中所示的组件之中,可以提供端口1060以使电子装置1000与显卡、声卡、存储卡、usb装置等通信。电子装置1000可以是包括典型的台式计算机或膝上型计算机以及智能电话、平板pc、智能可穿戴装置等的综合概念。

[0160]

处理器1050可以执行具体的算术运算、命令、任务等。处理器1050可以是中央处理单元(cpu)、微处理器单元(mcu)或芯片上系统(soc),并且可以经由总线1070来与显示器1010、传感器单元1020、存储器1030、通信单元1040和连接到端口1060的其它装置通信。

[0161]

存储器1030可以是被构造为存储用于电子装置1000的操作的数据、多媒体数据等的存储介质。存储器1030可以包括诸如随机存取存储器(ram)的易失性存储器或者诸如快闪存储器的非易失性存储器等。存储器1030可以包括固态驱动器(ssd)、硬盘驱动器(hdd)和光学驱动(odd)中的至少一种作为存储装置。在图28中所示的示例实施例中,存储器1030可以包括根据上面参照图1至图27b描述的各种实施例的存储器装置。

[0162]

如上所述,根据示例实施例,存储器装置可以包括外围电路区域和设置在外围电路区域上方的单元区域。单元区域可以具有其中设置有沟道结构的单元阵列区域和其中设置有连接到字线的单元接触件的单元接触区域。单元接触区域可以在与形成有单元区域的基底的上表面平行的方向上从单元阵列区域延伸,并且可以在与基底的上表面平行的方向中的至少一个方向上具有彼此不同的长度。另外,单元接触件的至少部分可以共享形成在外围电路区域中的传输元件。因此,存储器装置的集成密度可以增加。

[0163]

虽然上面已经示出且描述了示例性实施例,但是本领域技术人员将清楚的是,在不脱离如通过所附权利要求限定的本发明的范围的情况下可以做出修改和变型。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1