半导体器件的制作方法

半导体器件

1.本申请是申请日为2017年2月27日且题为“半导体器件”的第201710107234.x号发明专利申请的分案申请。

技术领域

2.本公开涉及半导体器件。

背景技术:

3.半导体器件是电子工业中的重要元件。用于存储数据的存储器件、用于处理数据的处理器等可以由半导体器件提供。近期,已经进行了旨在改善半导体器件的集成度并且减小其功耗的许多研究。此外,已经执行了旨在开发具有三维结构的半导体器件从而减少由半导体器件中包括的半导体元件的尺寸上的减小所引起的限制的各种研究。

技术实现要素:

4.本公开涉及限制(和/或防止)在制造工艺中在多个沟道区之间形成空隙的半导体器件。

5.根据本发明构思的示例实施方式,一种半导体器件可以包括:衬底、在衬底上的源/漏区、在源/漏区之间的衬底上的多个纳米片、在衬底上并且围绕多个纳米片的栅电极、以及在所述多个纳米片和栅电极之间的衬底上的栅绝缘层。源/漏区垂直于衬底的上表面延伸。所述多个纳米片彼此分离。所述多个纳米片限定在第一方向上延伸的沟道区。栅电极在交叉第一方向的第二方向上延伸。栅电极在第一方向上的长度可以大于所述多个纳米片中的相邻纳米片之间的间隔。

6.根据本发明构思的示例实施方式,一种半导体器件可以包括:衬底、在衬底上并且在第一方向上延伸的多个纳米片、以及掩埋所述多个纳米片的在衬底上的栅电极。栅电极包括在所述多个纳米片之间的第一区域和围绕第一区域的第二区域。第一区域和第二区域具有彼此不同的堆叠结构。

7.根据本发明构思的示例实施方式,一种半导体器件可以包括:衬底、在衬底上的源/漏区、在衬底上的多个纳米片、围绕所述多个纳米片的在衬底上的栅绝缘层、以及在衬底上并且掩埋所述多个纳米片的栅电极。源/漏区垂直于衬底的上表面延伸。所述多个纳米片在衬底的上表面上方沿第一方向延伸并且连接到源/漏区。所述多个纳米片在垂直于衬底的上表面的方向上彼此分离。栅电极包括在所述多个纳米片之间的第一区域和围绕第一区域的第二区域。第一区域中包括的金属层的数目小于第二区域中包括的金属层的数目。栅电极的长度大于或等于所述多个纳米片中的相邻纳米片之间的间隔的约1.2倍。

8.根据本发明构思的示例实施方式,一种半导体器件包括:在第一方向上彼此间隔开的一对源/漏区、在该对源漏区之间的多个纳米片、栅电极、以及栅绝缘层。该对源/漏区包括彼此面对的侧壁。所述多个纳米片沿该对源/漏区的侧壁彼此间隔开。所述多个纳米片包括半导体材料。栅电极包括在所述多个纳米片之间延伸的第一区域和在所述多个纳米片

中的最上一个纳米片上的第二区域。第一区域被连接到第二区域。栅绝缘层在栅电极和所述多个纳米片之间。栅绝缘层在栅电极和该对源/漏区之间延伸。

附图说明

9.从结合附图的以下详细描述,本发明构思的以上及其它方面和特征将被更清楚地理解,其中:

10.图1是根据本发明构思的示例实施方式的半导体器件的示意性平面图;

11.图2是根据本发明构思的示例实施方式的半导体器件的一部分的透视图;

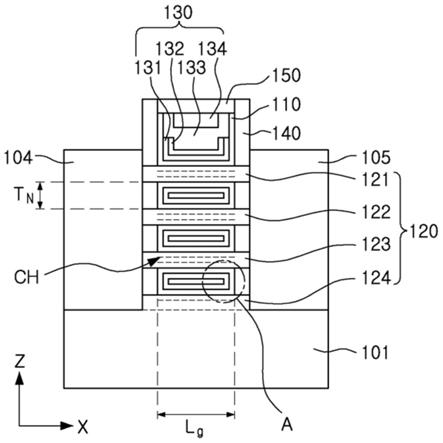

12.图3是沿图2所示的半导体器件的线iii-iii'截取的截面图;

13.图4是图3所示的半导体器件的区域a的放大图;

14.图5是沿图2所示的半导体器件的线v-v'截取的截面图;

15.图6是沿图2所示的半导体器件的线vi-vi'截取的截面图;

16.图7是根据本发明构思的示例实施方式的半导体器件的一部分的透视图;

17.图8是沿图7所示的半导体器件的线viii-viii'截取的截面图;

18.图9是图8所示的半导体器件的区域b的放大图;

19.图10是沿图7所示的半导体器件的线x-x'截取的截面图;

20.图11是沿图7所示的半导体器件的线xi-xi'截取的截面图;

21.图12至53是示出用于制造图2所示的半导体器件的方法的图;

22.图54至65是示出用于制造图7所示的半导体器件的方法的图;

23.图66和67是包括根据本发明构思的示例实施方式的半导体器件的电子设备的框图。

具体实施方式

24.在下文中,本发明构思的示例实施方式将参考附图被描述如下。

25.图1是根据本发明构思的示例实施方式的半导体器件的示意性平面图。

26.参考图1,根据本发明构思的示例实施方式的半导体器件10可以包括提供为有源区的多个鳍结构f和形成为交叉鳍结构f的多个栅电极130。多个鳍结构f可以在垂直于衬底的上表面(图1中的xy平面)的方向上被形成。衬底可以包括半导体材料。多个鳍结构f可以包括用杂质掺杂的源/漏区,并且沟道区可以被形成在源/漏区之间。

27.沟道区可以被掩埋在栅电极130中。例如,栅电极130可以被形成为围绕沟道区并且交叉多个鳍结构f。沟道区可以由设置在源/漏区之间的纳米片提供。在示例实施方式中,纳米片可以具有在几纳米到几十纳米(例如2nm到100nm)的范围内的厚度。

28.栅电极130可以由导电材料形成,诸如金属、金属硅化物、多晶硅等,及其组合。栅电极130可以包括多个层。当栅电极130包括多个层时,栅电极130可以包括功函数金属层、阻挡金属层、栅金属层等。在示例实施方式中,保护层150可以被提供在栅电极130的上部分上,保护层150限制(和/或防止)氧渗透到栅电极130中。

29.栅绝缘层110和间隔物140可以被设置在栅电极130的侧面上。以与栅电极130类似的方式,栅绝缘层110和间隔物140可以被形成为围绕沟道区ch并且交叉多个鳍结构f。栅电极130可以在与鳍结构f接触的同时在一个方向(例如图1中的y轴的方向)上延伸。

30.栅绝缘层110可以包括多个层。在示例实施方式中,栅绝缘层110可以包括第一绝缘层111和第二绝缘层112。第一绝缘层111和第二绝缘层112可以具有不同的电容率(permittivity)。例如,当第一绝缘层111被设置为比设置到沟道区ch的第二绝缘层112更靠近沟道区ch时,第一绝缘层111可以具有比第二绝缘层112的电容率更低的电容率。

31.图2是根据本发明构思的示例实施方式的半导体器件的一部分的透视图。

32.参考图2,根据示例实施方式的半导体器件100可以包括:衬底101、形成在衬底101上的源/漏区104和105、以及形成为交叉源/漏区104和105的栅电极130。栅电极130可以被形成为围绕设置在源/漏区104和105之间的沟道区。此外,栅绝缘层110和间隔物140可以被设置在栅电极130的侧面上。栅绝缘层110也可以被设置在栅电极130和沟道区ch之间。

33.沟道区可以由多个纳米片提供。多个纳米片可以被设置在源/漏区104和105之间。多个纳米片可以在垂直于衬底101的上表面的方向(图2中的z轴的方向)上彼此分离。多个纳米片之间的间隔可以用栅电极130填充。

34.衬底绝缘层103可以被提供在衬底101上,并且被设置为围绕衬底101的一部分。在示例实施方式中,衬底101的一部分可以向上突出以被连接到源/漏区104和105。衬底绝缘层103可以被设置为围绕衬底101的突出部分的侧面。衬底绝缘层103的上表面可以与衬底101的上表面共面。此外,层间绝缘层可以被设置在衬底绝缘层103上以覆盖栅电极130以及源/漏区104和105。

35.图3是沿图2所示的半导体器件的线iii-iii'截取的截面图。图4是图3所示的半导体器件的区域a的放大图。

36.参考图3,半导体器件100可以包括:在衬底101上沿一个方向(图3中的z轴的方向)彼此分离的多个纳米片121至124(纳米片120);通过纳米片120彼此连接的源/漏区104和105;栅电极130等。栅电极130可以形成为掩埋多个纳米片120。栅绝缘层110可以被设置在栅电极130和多个纳米片120之间。纳米片120的数目和设置不限于图3的配置,并且可以被不同地改变。

37.多个纳米片120可以提供沟道区ch。沟道区ch可以由纳米片120的与栅绝缘层110和栅电极130相邻的部分提供。当大于半导体器件100的阈值电压的电压被施加到栅电极130时,耗尽区可以被形成在沟道区ch上以在源/漏区104和105之间流动电流。阈值电压可以由包含在栅电极130中的材料和栅电极130的堆叠结构确定。

38.在示例实施方式中,栅电极130可以包括功函数金属层132和133以及栅金属层134。阻挡金属层131可以被进一步提供在功函数金属层132和133与栅绝缘层110之间。阻挡金属层131可以由钽氮化物(tan)、钽氮氧化物(tano)、钽硅氮化物(tasin)、钛硅氮化物(tisin)等形成。栅电极130的堆叠结构不限于图3的配置,并且可以被不同地改变。

39.功函数金属层132和133可以确定半导体器件100的阈值电压。在示例实施方式中,功函数金属层132和133可以包括彼此堆叠的第一功函数金属层132和第二功函数金属层133。第一功函数金属层132和第二功函数金属层133可以包括彼此不同的材料。功函数金属层132和133的材料可以根据半导体器件100是n型半导体器件还是p型半导体器件而变化。当半导体器件100是n型半导体器件时,功函数金属层132和133可以包括铪、锆、钛、钽、铝和包含上述金属的金属碳化物。当半导体器件100是p型半导体器件时,功函数金属层132和133可以包括钌、钯、铂、钴、镍及其氧化物。然而,除以上材料之外,功函数金属层132和133

的材料可以被不同地修改。

40.栅金属层134可以填充限定在功函数金属层132和133上的间隔。栅金属层134的上表面可以与第二功函数金属层133的上表面共面。栅金属层134可以由钛氮化物(tin)形成。

41.参考图3,在根据示例实施方式的半导体器件100中,栅长度lg可以大于纳米片120中的相邻纳米片120之间的间距t

n

。栅长度lg可以被定义为在第一方向(图3中的x轴的方向)上栅电极130或间隔物之间的间隔的长度。在示例实施方式中,栅长度lg可以大于或等于纳米片120之间的间距t

n

的约1.2倍。纳米片120的厚度(z轴方向的厚度)可以小于或等于约50nm,并且纳米片120的长度(x轴方向的长度)可以是几十纳米(例如2nm至100nm)。纳米片120可以具有大于其厚度的长度。纳米片120还可以具有小于或等于其之间的间距t

n

的厚度。在示例实施方式中,纳米片120之间的间距t

n

可以大于0nm并且小于或等于约30nm。

42.当纳米片120的厚度小于或等于纳米片120之间的间距(spacing)t

n

的约0.8倍时,纳米片120之间的间隔(space)可以用栅绝缘层110和栅电极130填充,而不降低半导体器件100的集成度。此外,纳米片120中的相邻纳米片120之间的间距t

n

与纳米片120的厚度之和可以与栅电极130的栅长度lg基本相同。

43.间隔物140的厚度(x轴方向的厚度)可以是大约10nm(例如在大约5nm至大约15nm的范围内),并且栅电极130的栅长度lg可以通过从纳米片120的长度减去间隔物140的厚度的两倍来被确定。如之前描述的,栅电极130的栅长度lg可以被确定为大于或等于纳米片120之间的间距t

n

的约1.2倍的值。因此,在示例实施方式中,间隔物140的厚度、纳米片120的长度和纳米片120之间的间距t

n

可以根据诸如以下方程式1的条件来被确定。

44.【方程式1】

45.1.2*t

n

≤(纳米片的长度-2*间隔物的厚度)

46.为了限制(和/或防止)纳米片120之间的间隔被栅电极130不完全地填充,栅电极130可以被形成为具有大于纳米片120之间的间距t

n

的栅长度lg。栅电极130可以通过去除提供在间隔物140之间的虚设栅极然后用金属材料填充已经从其去除了虚设栅极的间隔来形成。在用金属材料填充间隔之前,栅绝缘层可以首先被形成在间隔物140的内侧和纳米片120的外侧上。在这种情况下,如果间隔物140之间的间隔在填充纳米片120之间的间隔之前首先用金属材料填充,则纳米片120之间的间隔可以被金属材料不完全地填充。因此,空隙可以由不完全地填充的间隔产生。因此,由于纳米片120之间的间隔中的空隙,半导体器件100的性能可以劣化。

47.因此,为了限制和/或防止纳米片之间的间隔中的空隙,栅电极130可以被形成从而具有比纳米片120之间的间距t

n

更大的长度lg。此外,栅长度lg可以对应于间隔物140之间的间距。因此,通过在间隔物140之间确保足够的间隔,纳米片120之间的间隔可以在用栅电极130填充间隔物140之间的间隔之前首先被栅电极130填充。

48.参考图4,栅绝缘层110可以包括多个层。在示例实施方式中,栅绝缘层110可以包括第一绝缘层和第二绝缘层。第一绝缘层111和第二绝缘层112可以具有彼此不同的电容率。第二绝缘层的电容率可以大于第一绝缘层的电容率。在这种情况下,第二绝缘层可以被设置为比设置到栅电极130的第一绝缘层更靠近栅电极130。换言之,第一绝缘层可以被设置为比设置到沟道区ch的第二绝缘层更靠近沟道区ch。通过将具有相对低的电容率水平的第一绝缘层设置为比具有相对高的电容率水平的第二绝缘层更靠近沟道区ch,存储器件的

特性,诸如擦除特性,可以被改善。同时,具有相对高的电容率水平的第二绝缘层可以比第一绝缘层更厚。

49.具有相对高的电容率水平的第二绝缘层112可以包括硅氧化物(sio2)、硅氮化物(si3n4)、硅氮氧化物(sion)或高介电常数(dielectric constant)材料。高介电常数材料可以是诸如铝氧化物(al2o3)、钽氧化物(ta2o3)、钛氧化物(tio2)、钇氧化物(y2o3)、锆氧化物(zro2)、锆硅氧化物(zrsi

x

o

y

)、铪氧化物(hfo

x

)、铪硅氧化物(hfsi

x

o

y

)、镧氧化物(la2o3)、镧铝氧化物(laal

x

o

y

)、镧铪氧化物(lahf

x

o

y

)、铪铝氧化物(hfal

x

o

y

)和镨氧化物(pr2o3)的材料。

50.此外,多个金属层131至134中的仅阻挡金属层131以及功函数金属层132和133可以被设置在纳米片120中的相邻纳米片120之间。在图4中,纳米片中的相邻纳米片之间的间隔可以仅用阻挡金属层131和第一功函数金属层132填充。设置在纳米片120之间的金属层131至134的数目可以由纳米片120之间的间距t

n

以及金属层131至134的每个厚度确定。

51.图5是沿图2所示的半导体器件的线v-v'截取的截面图。

52.参考图5,多个纳米片120可以被设置在衬底101上。多个纳米片120可以包括第一纳米片121至第四纳米片124。第四纳米片124可以在衬底101的上表面上,并且第一纳米片121至第三纳米片123可以与衬底101分离。第一纳米片121至第四纳米片124可以彼此分离以将栅电极130的一部分和栅绝缘层110的每个设置在纳米片120中的相邻纳米片120之间。换言之,第一纳米片121至第四纳米片124的至少一部分可以被栅电极130掩埋。

53.栅电极130可以包括阻挡金属层131、功函数金属层132和133、以及栅金属层134。栅电极130中包括的多个金属层131至134可以被顺序地堆叠在纳米片120的每个上。在图5中,纳米片120中的相邻纳米片120之间的间隔可以仅用阻挡金属层131和第一功函数金属层132填充。

54.换言之,当栅电极130被划分为设置在纳米片120中的相邻纳米片120之间的第一区域和除第一区域之外的第二区域时,第一区域可以不包括第二功函数金属层133和栅金属层134。因此,设置在纳米片120中的相邻纳米片120之间的第一区域可以具有与第二区域的堆叠结构不同的堆叠结构。在示例实施方式中,第一区域中包括的金属层的数目可以小于第二区域中包括的金属层的数目。同时,第二区域可以被限定为围绕第一区域的区域。

55.图6是沿图2所示的半导体器件的线vi-vi'截取的截面图。

56.参考图6,在沿线vi-vi'截取的截面中,栅电极130未被示出,并且由间隔物140围绕的多个纳米片120的结构可以被示出。在示例实施方式中,第一纳米片121至第三纳米片123在y轴方向和z轴方向上可以被间隔物140围绕。

57.多个纳米片120的至少部分可以穿过间隔物140以被连接到源/漏区104和105。参考图3以及图6,第一纳米片121至第三纳米片123的每个的两侧可以被连接到源/漏区104和105,可以被栅电极130和间隔物140围绕。

58.图7是根据本发明构思的示例实施方式的半导体器件的一部分的透视图。

59.参考图7,根据本发明构思的示例实施方式,半导体器件200可以包括衬底201、形成在衬底201上的源/漏区204和205、形成为交叉源/漏区204和205的栅电极230等。以与图2中的半导体器件100的方式类似的方式,栅绝缘层210和间隔物240可以被形成在栅电极230的侧面上,并且衬底201的一部分可以向上突出以被连接到源/漏区204和205。衬底201的突

出部分可以被衬底绝缘层203围绕。

60.在图7的半导体器件200中,栅电极230可以包括功函数金属层231和232以及栅金属层233。在图2中的半导体器件100中,阻挡金属层131可以被包括在栅电极130中,而阻挡金属层可以不存在于图7中的半导体器件200中。因此,功函数金属层231和232的厚度可以不同于图2所示的示例实施方式的功函数金属层的厚度。由于栅电极的物理性质上的差异,图2和7中所示的半导体器件100和200的每个可以具有彼此不同的阈值电压。

61.图8是沿图7所示的半导体器件的线viii-viii'截取的截面图。图9是图8所示的半导体器件的区域b的放大图。

62.参考图8,在根据本发明构思的示例实施方式的半导体器件200中,多个纳米片220中的相邻纳米片之间的间距t

n

可以小于栅电极230的栅长度lg。

63.如参考图3描述的,栅长度lg可以被定义为栅电极230的在一个方向(图8中的x轴的方向)上的长度,并且可以对应于间隔物240之间的间距。通过如以上描述地定义栅长度lg与纳米片220之间的间距t

n

之间的关系,可以限制(和/或防止)用栅电极230不完全地填充纳米片之间的间隔。

64.参考图9,栅绝缘层210可以包括第一绝缘层211和第二绝缘层212。如参考图4描述地,第一绝缘层211和第二绝缘层212可以具有彼此不同的电容率。第二绝缘层212的电容率可以大于第一绝缘层211的电容率。

65.此外,纳米片220中的相邻纳米片220之间的间隔可以仅用栅绝缘层210和第一功函数金属层231填充。纳米片220中的相邻纳米片之间的间距t

n

可以小于栅绝缘层210的厚度与第一功函数金属层231的厚度之和的约2倍。

66.图10是沿图7所示的半导体器件的线x-x'截取的截面图。图11是沿图7所示的半导体器件的线xi-xi'截取的截面图。

67.参考图10,多个纳米片220可以被栅绝缘层210和栅电极230围绕。栅电极230可以包括功函数金属层231和232以及栅金属层233。功函数金属层231和232可以包括第一功函数金属层231和第二功函数金属层232,并且第一功函数金属层231和第二功函数金属层232可以具有彼此不同的金属材料。

68.参考图11,多个纳米片220可以被设置在源/漏区204和205之间的栅电极230和间隔物240围绕。多个纳米片220的至少部分可以穿过间隔物240以被分别连接到源/漏区204和205。

69.在图8至10中,在多个纳米片220之间限定的间隔可以用栅绝缘层210和第一功函数金属层231填充。换言之,栅绝缘层210和第一功函数金属层231可以被设置在多个纳米片220中的相邻纳米片220之间。栅电极230可以被划分为设置在纳米片220中的相邻纳米片220之间的第一区域和除第一区域之外的第二区域。栅电极230可以包括根据第一区域和第二区域的不同堆叠结构。在第一区域中,栅电极230可以是仅包括第一功函数金属层231的堆叠结构。在第二区域中,栅电极230可以是包括第一功函数金属层231和第二功函数金属层232以及栅金属层233的堆叠结构。

70.图12至53是示出用于制造图2所示的半导体器件的方法的图。图14是沿图13的线xiv-xiv'截取的截面图。图17和18是沿图16的线xvii-xvii'和xviii-xviii'截取的截面图。图21至23是沿图20的线xxi-xxi'、xxii-xxii'和xxiii-xxiii'截取的截面图。图26是沿

图25的线xxvi-xxvi'截取的截面图。图29是沿图28的线xxix-xxix'截取的截面图。图32是沿图31的线xxxii-xxxii'截取的截面图。图35是沿图34的线xxxv-xxxv'截取的截面图。图38是沿图37的线xxxviii-xxxviii'截取的截面图。图41是沿图40的线xli-xli'截取的截面图。图44是沿图43的线xliv-xliv'截取的截面图。图47是沿图46的线xlvii-xlvii'截取的截面图。图50是沿图49的线l-l'截取的截面图。图53是沿图52的线liii-liii'截取的截面图。

71.参考图12至14,多个半导体层121s至124s(半导体层120s)和多个牺牲层161s至163s(牺牲层160s)可以被交替地堆叠在衬底101上。由于图12所示的透视图可以通过x-y平面被观察,所以图13示出了其俯视平面图。多个半导体层120s可以包括半导体材料,并且多个牺牲层160s可以包括相对于多个半导体层120s具有蚀刻选择性的材料。在示例实施方式中,多个半导体层120s可以包括硅(si),并且多个牺牲层160s可以包括硅锗(sige)。

72.根据示例实施方式,多个半导体层120s和牺牲层160s的各自厚度可以被不同地改变。在示例实施方式中,多个半导体层120s的厚度可以小于多个牺牲层160s的厚度。多个牺牲层160s可以在后续工艺中被去除,并且被栅绝缘层110和栅电极130替换。因此,多个牺牲层160s的厚度可以基本上分别等于多个纳米片120之间的间隔距离。

73.参考图15至18,鳍结构f可以通过去除多个半导体层120s和牺牲层160s的部分来被形成。因为图15所示的透视图可以通过x-y平面被观察,所以图16示出其俯视平面图。一起参考图15至18,鳍结构f可以包括交替地堆叠在衬底101上的多个半导体层121f至124f(半导体层120f)和牺牲层161f至163f(牺牲层160f)。

74.为了形成鳍结构f,衬底101的至少一部分可以从其上表面去除,并且衬底绝缘层103可以被设置在其中。在这种情况下,衬底绝缘层103的上表面可以与衬底101的最上表面共面。

75.如图1所示,鳍结构f可以在特定方向(例如在图1的x轴的方向)上在衬底101上延伸。鳍结构f可以以在其之间的期望的(和/或替代地,预定的)间隔被设置。在示例实施方式中,在y轴的方向上鳍结构f的各自宽度和鳍结构f之间的间隔可以是几十纳米(例如20nm至100nm)。多个半导体层120f的每个的厚度可以在三纳米到三十纳米的范围内。多个牺牲层160f的每个的厚度可以大于多个半导体层120f的每个的厚度。

76.参考图19至23,虚设栅极130a和第一间隔物140a可以被形成在鳍结构f上。由于图19所示的透视图可以通过x-y平面被观察,所以图20示出了其俯视平面图。在示例实施方式中,盖层还可以被形成在虚设栅极130a上,并且蚀刻停止层还可以被形成在虚设栅极130a与多个半导体层120f之间。

77.虚设栅极130a和第一间隔物140a可以以它们与鳍结构f接触的形式被形成。虚设栅极130a可以由多晶硅等形成,并且第一间隔物140a可以使用诸如硅氧化物、硅氮化物等的绝缘材料被形成。

78.在后续工艺中,虚设栅极130a可以用栅电极130替换。因此,栅电极130的栅长度lg在一个方向(图19至23中的y轴的方向)上可以基本上等于虚设栅极130a的宽度。在示例实施方式中,虚设栅极130a的宽度可以大于多个牺牲层160f的每个的厚度。因此,在去除虚设栅极130a之后用于形成栅电极130的后续工艺中,在其中牺牲层160f被去除的间隔可以用栅电极130填充而没有空隙。

79.在示例实施方式中,虚设栅极130a的宽度可以由大于或等于多个牺牲层160f的每个厚度的值的约1.2倍来确定。此外,虚设栅极130a的宽度可以与多个半导体层120f的每个厚度和多个牺牲层160f的每个厚度之和基本相同。

80.参考图24至26,通过使用虚设栅极130a和第一间隔物140a作为蚀刻掩模执行蚀刻工艺,鳍结构f的至少一部分可以被去除以形成多个纳米片121至124(纳米片120)。多个纳米片120的每个可以被虚设栅极130a和第一间隔物140a围绕。多个牺牲层161至163(牺牲层160)可以被设置在多个纳米片120之间。

81.如图24至26所示,衬底101的上表面的一部分可以从虚设栅极130a和第一间隔物140a向外暴露。衬底101的上表面可以被用于使用外延工艺形成源/漏区104和105。

82.参考图27至29,在虚设栅极130a和第一间隔物140a的侧面上暴露的牺牲层160的部分可以被去除以形成间隔物间隔s。如图27至29所示,第一牺牲层161至第三牺牲层163的至少部分可以被去除以形成间隔物间隔s。在这种情况下,间隔物间隔s的深度可以基本上等于第一间隔物140a的厚度。

83.参考图30至32,第二间隔物140b可以通过用绝缘材料填充间隔物间隔s而形成。第二间隔物140b的厚度可以基本上等于第一间隔物140a的厚度。第二间隔物140b的外表面可以与第一间隔物140a的外表面共面。第一间隔物140a和第二间隔物140b可以被提供为围绕将被顺序形成的栅电极的间隔物140。第二间隔物140b可以由与第一间隔物140a的材料相同的材料形成。在示例实施方式中,第一间隔物140a和第二间隔物140b可以包括硅氧化物、硅氮化物等。

84.参考图33至35,源/漏区104和105可以使用选择性外延生长(seg)从衬底101的上表面形成。源/漏区104和105可以包括用期望的(和/或替代地,预定的)杂质掺杂的半导体材料。源/漏区104和105的厚度可以被不同地改变。源/漏区104和105的上表面可以与设置在纳米片120中的最上层的纳米片121的上表面共面。

85.参考图36至38,层间绝缘层170可以被形成在衬底101上。层间绝缘层170可以被形成为覆盖间隔物140和源/漏区104和105的外侧。

86.参考图39至41,虚设栅极130a可以被去除。虚设栅极130a可以基于虚设栅极130a相对于第一间隔物140a和源/漏区104和105的蚀刻选择性被选择性地去除。纳米片121至124和牺牲层161至163可以通过去除虚设栅极130a而从第一间隔物140a之间的间隔向外暴露。

87.参考图42至45,牺牲层160可以被选择性地去除以形成水平开口h。如以上描述的,牺牲层160可以包括与纳米片120不同的材料,诸如相对于纳米片120中包括的材料具有期望的(和/或替代地,预定的)蚀刻选择性的材料。在示例实施方式中,纳米片120可以包括诸如硅的半导体材料以提供半导体器件100的沟道区,并且牺牲层160可以包括硅锗。为了选择性地去除牺牲层160的暴露部分同时抑制纳米片120的蚀刻,相对于硅(si)具有硅锗(sige)的显著蚀刻选择性的蚀刻剂可以被使用。例如,包括过氧化氢(h2o2)、氢氟酸(hf)和乙酸(ch3cooh)的蚀刻剂,包括氢氧化铵(nh4oh)、过氧化氢(h2o2)和去离子水(h2o)的蚀刻剂,以及包括过乙酸的蚀刻剂或其组合可以被使用。

88.当牺牲层160被去除时,纳米片120可以被彼此分离。参考图44,纳米片120可以在z轴的方向上彼此分离,并且纳米片120之间的间距t

n

可以小于第一间隔物140a之间的间距

w

d

。在示例实施方式中,第一间隔物140a之间的间距w

d

可以大于或等于纳米片120之间的间距t

n

的约1.2倍。因此,在用于形成栅绝缘层110和栅电极130的后续工艺中,在用栅绝缘层110和栅电极130填充第一间隔物140a之间的间隔之前,水平开口h可以首先用栅绝缘层110和栅电极130填充。因此,可以限制(和/或防止)空隙从不完全地填充的水平开口h产生。

89.参考图45至47,栅绝缘层可以被形成。栅绝缘层110可以被设置在第一间隔物140a的内表面以及纳米片120之间的水平开口h的内表面上。在示例实施方式中,栅绝缘层110可以被设置为在y轴的方向和z轴的方向上围绕纳米片120,并且水平开口h可以不被栅绝缘层110完全填充。换言之,在形成栅绝缘层110之后,在纳米片120之间仍可以存在间隔。

90.栅绝缘层110可以包括具有彼此不同的电容率的第一绝缘层和第二绝缘层。第二绝缘层的电容率可以大于第一绝缘层的电容率。第一绝缘层可以被设置为比第二绝缘层更靠近第一间隔物140a和纳米片120。换言之,第一绝缘层可以在形成第二绝缘层之前被形成。

91.栅绝缘层110可以通过诸如原子层沉积(ald)、化学气相沉积(cvd)等的工艺被形成。在示例实施方式中,第二绝缘层可以被形成为比第一绝缘层更厚。例如,第一绝缘层的厚度可以小于约1nm,并且第二绝缘层的厚度可以是约1nm至约2nm。

92.参考图48至50,阻挡金属层131和第一功函数金属层132可以被顺序地形成在栅绝缘层110上。纳米片120之间的间隔可以用阻挡金属层131和第一功函数金属层132完全填充。因此,如图48至50所示,仅第一功函数金属层132可以从纳米片120向外暴露。

93.参考图50,纳米片120之间的间隔可以用栅绝缘层110、阻挡金属层131和第一功函数金属层132完全填充。同时,参考图48,纳米片120不设置在第一间隔物140a之间处的间隔可以不被栅绝缘层110、阻挡金属层131和第一功函数金属层132完全填充。换言之,因为纳米片120之间的间隔首先被填充,所以可以限制(和/或防止)从不完全填充的间隔产生空隙。

94.参考图51至53,第二功函数金属层133和栅金属层134可以被形成在第一功函数金属层132上。第二功函数金属层133可以包括与第一功函数金属层132不同的材料。半导体器件100的阈值电压可以由每个功函数金属层132和133的材料和厚度确定。栅金属层134可以被设置在第二功函数金属层133上,保护层150可以被进一步提供在栅金属层134上。

95.保护层150可以由具有在几埃至几百埃(例如至)的范围内的厚度的硅氮化物层形成。保护层150可以为了限制(和/或防止)通过将氧渗透到栅电极130中而引起的阈值电压的劣化的目的而被形成。栅电极130的一部分可以被去除,并且保护层150可以被形成在栅电极的被去除的部分中。

96.参考图53,栅电极130可以包括设置在纳米片120中的相邻纳米片120之间的第一区域g1和除第一区域g1之外的第二区域g2。因为第一区域g1被限定为设置在纳米片120中的相邻纳米片120之间的区域,所以图53中的栅电极可以包括总共三个第一区域g1。

97.第一区域g1和第二区域g2可以具有彼此不同的堆叠结构。第一区域g1可以仅包括阻挡金属层131、第一功函数金属层132,并且第二区域可以包括阻挡金属层131、第一功函数金属层132和第二功函数金属层133以及栅金属层134。第一区域g1中包括的金属层的数目可以小于第二区域g2中包括的金属层的数目。第一区域g1和第二区域g2的每个的金属层的数目和类型可以被不同地改变。

98.在根据本发明构思的示例实施方式的制造半导体器件100的工艺中,如图19至23中所示,第一间隔物140a之间的间距w

d

可以大于牺牲层160f的每个的厚度。第一间隔物140a之间的间距w

d

可以由虚设栅极130a的宽度确定。栅电极130可以被形成在去除了虚设栅极的区域中。栅电极130的栅长度lg可以大于纳米片120之间的间距t

n

。因此,通过形成具有比每个牺牲层160f的厚度更大的宽度的虚设栅极130a,纳米片120之间的间隔可以用栅电极130填充而没有空隙。

99.图54至65是示出用于制造图7所示的半导体器件的方法的图。图55是沿图54的线lvi-lvi'截取的截面图。图59是沿图58的线lix-lix'截取的截面图。图62是沿图61的线lxii-lxii'截取的截面图。图65是沿图64的线lxv-lxv'截取的截面图。

100.参考图54至56,形成在衬底201上的虚设栅极可以被去除以暴露在第一间隔物240a之间的间隔中的多个纳米片221至224(纳米片220)。牺牲层可以被选择性地去除以形成水平开口h。纳米片220中的相邻纳米片220之间的间距t

n

可以小于第一间隔物240a之间的宽度w

d

。

101.参考图57至59,第一间隔物240a之间的间隔以及纳米片220之间的水平开口h可以用栅绝缘层210填充。

102.如图9所示,栅绝缘层210可以包括第一绝缘层211和第二绝缘层212。第一绝缘层211和第二绝缘层212可以具有彼此不同的电容率。纳米片220的每个可以被栅绝缘层210围绕。纳米片120之间的间隔可以不被栅绝缘层210完全填充。

103.参考图60至62,第一功函数金属层231可以被形成在栅绝缘层210上。纳米片220之间的间隔可以用第一功函数金属层231填充。因此,如图60所示,第一功函数金属层231可以从纳米片220向外暴露。纳米片220之间的间隔可以用栅绝缘层210和第一功函数金属层231完全填充而没有空隙。

104.在示例实施方式中,纳米片220之间的间距t

n

、栅绝缘层210的厚度以及第一功函数金属层231的厚度可以具有诸如以下方程式2的关系。根据诸如方程式2的关系,通过形成纳米片220之间的间距t

n

、栅绝缘层210和第一功函数金属层231,纳米片220之间的间隔可以用栅绝缘层210和第一功函数金属层231完全填充。

105.【方程式2】

106.t

n

≤(栅绝缘层的厚度+第一功函数金属层的厚度)*2

107.参考图63至65,第二功函数金属层232和栅金属层233可以被形成在第一功函数金属层231上。保护层250可以被形成在栅金属层233上。第二功函数金属层232可以包括不同于第一功函数金属层231的材料。半导体器件200的阈值电压可以由第一功函数金属层231和第二功函数金属层232的每个的厚度和材料确定。

108.参考图65,栅电极230可以包括第一区域g1和第二区域g2。第一区域g1可以被限定为设置在纳米片220之间的区域,第二区域g2可以是除了第一区域g1之外的区域。第一区域g1和第二区域g2可以具有彼此不同的堆叠结构。

109.第一区域g1可以仅包括第一功函数金属层231。另一方面,第二区域g2可以包括第一功函数金属层231和第二功函数金属层232以及栅金属层233。换言之,第一区域g1可以具有比第二区域g2简单的堆叠结构。栅电极230可以具有大于它在第一区域g1中的厚度的宽度。

110.在本发明构思的示例实施方式中,半导体器件100和200可以被形成在一个衬底上。换言之,通过形成具有不同堆叠结构的栅电极130和230的半导体器件100和200,具有不同阈值电压的半导体器件100和200可以被提供在一个衬底中。

111.在本发明构思的示例实施方式中,根据半导体器件100和200的栅电极130和230的结构可以被不同地修改。

112.例如,栅电极130和230中包括的阻挡金属层和功函数金属层的数目可以被改变,并且阻挡金属层可以被设置在功函数金属层和栅金属层之间。以这种方式,通过不同地修改栅电极130和230的每个的堆叠结构,制造具有不同阈值电压的半导体器件100和200是可能的。

113.图66和67是包括根据本发明构思的示例实施方式的半导体器件的电子设备的框图。

114.参考图66,根据示例实施方式,存储设备1000可以包括与主机通信的控制器1010以及存储数据的存储器1020-1、1020-2和1020-3。控制器1010以及存储器1020-1、1020-2和1020-3可以包括根据以上描述的各种示例实施方式的半导体器件100和200。

115.与控制器1010通信的主机可以是配备有存储设备1000的各种电子设备。例如,主机可以是智能电话、数码相机、台式计算机、膝上型计算机、便携式媒体播放器等。控制器1010可以在接收到由主机发送的数据写入或数据读取的请求之后在存储器1020-1、1020-2和1020-3中存储数据,或者可以生成命令(cmd)以从存储器1020-1、1020-2和1020-3输出数据。

116.如图66所示,一个或更多存储器1020-1、1020-2和1020-3可以在存储设备1000中并行连接到控制器1010。通过将多个存储器1020-1、1020-2和1020-3并行连接到控制器1010,可以实现具有大容量的存储设备1000,诸如固态硬盘(ssd)。

117.参考图67,根据示例实施方式,电子设备2000可以包括通信单元2010、输入单元2020、输出单元2030、存储器2040和处理器2050。

118.通信单元2010可以包括有线/无线通信模块,例如无线互连网模块、近场通信模块、全球定位系统(gps)模块、移动通信模块等。通信单元2010中包括的有线/无线通信模块可以通过根据各种通信标准被连接到外部通信网络来发送和接收数据。

119.输入单元2020可以是为用户提供以控制电子设备2000的操作的模块,并且可以包括机械开关、触摸屏、语音识别模块等。另外,输入单元2020还可以包括手指鼠标设备或使用轨迹球、激光指示器等操作的鼠标。输入单元2020还可以包括用户可以通过其输入数据的各种传感器模块。

120.输出单元2030可以以音频或视频的形式输出在电子设备2000中处理的信息,并且存储器2040可以存储程序、数据等以处理和控制处理器2050。存储器2040可以包括根据本发明构思的各种示例实施方式的一个或更多半导体器件100和200,并且处理器2050可以通过根据所需操作向存储器2040发送命令来存储以及输出数据。处理器2050还可以由根据以上描述的示例实施方式的半导体器件100和200实现。

121.存储器2040可以通过嵌入在电子设备2000中的接口或单独的接口与处理器2050通信。当存储器2040通过单独的接口与处理器2050通信时,处理器2050可以通过各种接口标准,诸如sd、sdhc、sdxc、micro sd、usb等,将数据存储在存储器2040中或从存储器2040输

出数据。

122.处理器2050可以控制电子设备2000中包括的各单元的操作。处理器2050可以执行与语音呼叫、视频呼叫、数据通信等相关的控制和处理操作,或者可以执行控制和处理操作以播放和管理多媒体。此外,处理器2050可以处理由用户通过输入单元2020发送的输入,并且可以通过输出单元2030输出结果。此外,处理器2050可以将控制电子设备2000的操作所需的数据存储在存储器2040中,或者可以从其输出数据。

123.虽然示例实施方式已经在以上被示出和描述,但是对本领域技术人员来说将明显的是,能进行修改和变化而不背离由所附权利要求限定的范围。

124.本申请要求享有2016年2月26日在韩国知识产权局提交的韩国专利申请第10-2016-0023387号的优先权,其公开通过引用其全文合并在此。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1