半导体封装结构及其制造方法与流程

1.本公开大体上涉及半导体封装,并且具体地,涉及一种半导体封装结构及其制造方法。

背景技术:

2.随着电子工业的快速发展和半导体加工技术的进步,半导体芯片与越来越多的电子部件集成在一起以实现改进的电性能和额外功能。因此,需要更多的输入/输出(i/o)焊盘以用于这些芯片和部件之间的电连接。为了确保期望的性能和功能,在制造半导体装置封装期间执行电测试以确定目前为止制造的半导体装置封装中的电连接是否良好。

技术实现要素:

3.本公开的实施例提供了一种半导体封装结构。所述半导体封装结构包括第一半导体装置、第二半导体装置,用于第一半导体装置和第二半导体装置之间的电连接的再分布结构,所述再分布结构包括:图案化的第一介电层,所述第一介电层具有第一表面和与所述第一表面相对的第二表面;第二介电层,所述第二介电层位于第一半导体装置和图案化的第一介电层之间,所述第二介电层设置在图案化的第一介电层的第一表面上;以及图案化的第一电路层,所述第一电路层设置在图案化的第一介电层的第一表面上并且在第二介电层中延伸;以及电导体,所述电导体设置在由图案化的第一介电层和图案化的第一电路层界定的凹部中,被用于经由再分布结构的电连接。

4.本公开的一些实施例提供了一种制造半导体封装结构的方法。所述方法包括:在测试阶段之前,提供第一载体,在第一载体上方形成图案化的缓冲层,形成第一再分布结构,所述第一再分布结构包括在图案化的缓冲层上形成第一介电层,形成包括在第一介电层上的第一电路层和在第一电路层上的第二电路层的电路层堆叠,以及在第一介电层和第二电路层上形成第二介电层,以及在测试阶段之后,通过使用激光剥离去除第一载体,使用图案化的缓冲层作为掩模,去除未被图案化的缓冲层掩蔽的第一介电层的部分,得到图案化的第一介电层,所述图案化的第一介电层暴露第一电路层的部分,使用图案化的第一介电层作为掩模,去除第一电路层的暴露部分,得到图案化的第一电路层,并且在由图案化的第一介电层和图案化的第一电路层界定的凹部中形成电导体。

5.本公开的实施例还提供了一种制造半导体封装结构的方法。所述方法包括:提供第一载体,在第一载体上方形成图案化的缓冲层,形成第一再分布结构,所述第一再分布结构包括在图案化的缓冲层上形成第一介电层,在通过向第一再分布结构施加电信号进行电测试之后,去除第一载体,去除第一介电层的部分,得到图案化的第一介电层,所述图案化的第一介电层暴露第一电路层的部分,使用图案化的第一介电层作为掩模,去除第一电路层的暴露部分,得到图案化的第一电路层,并且在由图案化的第一介电层和图案化的第一电路层界定的凹部中形成电导体。

附图说明

6.当结合附图阅读时,从以下详细描述中容易理解本公开的一些实施例的方面。注意,各种结构可以不按比例绘制,并且为了讨论清楚,各种结构的尺寸可以任意增加或减小。

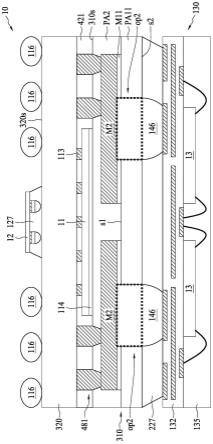

7.图1a是根据本公开的实施例的半导体封装结构的截面图。

8.图1b是根据本公开的另一实施例的半导体封装结构的截面图。

9.图2a至2u是截面图,其各自绘示根据本公开的实施例的制造如参考图1a所描述和绘示的半导体封装结构的方法的一或多个阶段。

10.图3a至3k是截面图,其各自绘示根据本公开的实施例的制造如参考图1b所描述和绘示的半导体封装结构的方法的一或多个阶段。

11.图4a至4p是截面图,其各自绘示与参考图2a至2u所描述和绘示的方法相比,制造半导体封装结构的方法的一或多个阶段。

12.图5a至5e是截面图,其各自绘示与参考图2a至2u所描述和绘示的方法相比,制造半导体封装结构的另一方法的一或多个阶段。

具体实施方式

13.在整个附图和详细描述中使用相同的附图标记来表示相同或相似的部件。从以下结合附图的详细描述中将容易理解本公开的实施例。

14.空间描述,例如“上面”、“下面”、“上”、“左”、“右”、“下”、“顶部”、“底部”、“竖直”、“水平”、“侧”、“较高”、“下部”、“上部”、“上方”、“下方”等,相对于特定部件或部件群组,或部件或部件群组的特定平面,针对相关联的图中所展示的部件的定向来指定。应当理解,这里使用的空间描述仅用于说明的目的,并且这里描述的结构的实际实现可以以任何定向或方式在空间上布置,只要本公开的实施例的优点不被这种布置偏离。

15.以下公开内容提供了用于实现所提供的主题的不同特征的许多不同实施例或实例。下面描述部件和布置的具体实例以解释本公开的某些方面。当然,这些仅仅是实例,并不旨在限制。例如,在以下描述中在第二特征之上方或之上形成第一特征可以包括其中第一特征和第二特征被形成或设置成直接接触的实施例,并且还可以包括其中附加特征可以被形成或设置在第一特征和第二特征之间以使得第一和第二特征可以不直接接触的实施例。此外,本公开可以在各个实例中重复参考数字和/或字母。这种重复是为了简单和清楚的目的,其本身并不表示所讨论的各种实施例和/或配置之间的关系。

16.图1a是根据本公开的实施例的半导体封装结构10的截面图。

17.参考图1a,半导体封装结构10包括第一半导体装置11、第二半导体装置12、封装装置130(所述封装装置130包括一或多个第三半导体装置13)、第一半导体装置11和第三半导体装置13之间的第一再分布结构(redistribution structure)310以及第一半导体装置11和第二半导体装置12之间的第二再分布结构320。在实施例中,第一半导体装置11包括应用处理器(application processor),第二半导体装置12包括集成无源装置(integrated passive device),并且第三半导体装置13包括存储装置(memory devices)。

18.第一再分布结构310提供第一半导体装置11和第三半导体装置13之间的电连接。第一半导体装置11经由第一再分布结构310和部分形成在第一再分布结构310中的电导体

(electrical conductors)146电连接到第三半导体装置13。第二再分布结构320提供第一半导体装置11和第二半导体装置12之间的电连接。此外,第一半导体装置11经由第二再分布结构320和设置在第二再分布结构320上的电导体(electrical conductors)116电连接到外部半导体装置或部件。

19.第一再分布结构包括图案化的第一介电层pa11、图案化的第二介电层pa2,以及电路层m。图案化的第一介电层pa11具有第一表面s1和与第一表面s1相对的第二表面s2。图案化的第二介电层pa2设置在图案化的第一介电层pa11的第一表面s1上并且在第一半导体装置11和图案化的第一介电层pa11之间。电路层m包括图案化的第一导电层m11和第二导电层m2。电路层m在图案化的第二介电层pa2中延伸。图案化的第一导电层m11设置在图案化的第一介电层pa11的第一表面s1上,并且在图案化的第二介电层pa2中延伸。图案化的第一导电层m11可以被用作第二导电层m2的种子层。第二导电层m2堆叠在图案化的第一导电层m11上,并且在图案化的第二介电层pa2中延伸。

20.凹部op2由图案化的第一介电层pa11和图案化的第一导电层m11界定。凹部op2提供用于保持或容纳电导体146的空间。电导体146贯穿图案化的第一介电层pa11,并且将第二导电层m2电连接到一或多个第三半导体装置13。因此,除了图案化的第一介电层pa11和图案化的第一导电层m11之外,凹部op2进一步由第二导电层m2界定。电导体146的一部分被容纳在凹部op2中,并且电导体146的其余部分从图案化的第一介电层pa11的第二表面s2突出。在对应于本公开的第一再分布结构310的现有再分布结构中,这种电导体可以设置在第一介电层的表面上或上方。与现有结构不同,凹部op2为电导体提供了深根(deeply rooted)的空间,使得确保了相对可靠的电连接。

21.设置在第一再分布结构310的表面310s上的第一半导体装置11,其包括用于电连接的柱(studs)113。可以使用粘合膜114来促进将第一半导体装置11附接到第一再分布结构310。图案化的导电层481设置在封装层(encapsulating layer)421中,所述封装层421封装第一半导体装置11并且延伸到图案化的第二介电层pa2中,所述图案化的导电层481电连接在第二导电层m2和第二再分布结构320之间。

22.第二半导体装置12面朝下(face-down)连接到第二再分布结构320的表面320s。底层填料(underfill)127施加在第二半导体装置12和第二再分布结构320之间。底层填料127保护第二半导体装置12免受湿气、离子污染物、辐射和具有热、机械、冲击和振动应力的不利操作环境的影响。设置在第二再分布结构320的表面320s上的电导体116,其提供第一半导体装置11到外部半导体装置的电连接。

23.第三半导体装置13被封装在封装层135中。第三半导体装置13经由再分布结构132和电导体146电连接到第一半导体装置11。电导体146部分地设置在第一再分布结构310的图案化的第一介电层pa11中,且其电连接在第二导电层m2和再分布结构132之间。此外,电导体146的从图案化的第一介电层pa11的第二表面s2突出的部分被密封在底层填料227中,所述底层填料227设置在再分布结构132和第一再分布结构310之间。底层填料227保护电导体146免受湿气、离子污染物、辐射和具有热、机械、冲击和振动应力的不利操作环境的影响。

24.在实施例中,图案化的第一介电层pa11包括有机材料,例如模制化合物(molding compound)、聚酰胺(polyamide,pa)、聚酰亚胺(polyimide,pi)、聚苯并唑

(polybenzoxazole,pbo)或环氧基材料(epoxy-based material)。在另一实施例中,图案化的第一介电层pa11包括无机材料,例如氧化硅(siox)、氮化硅(sinx)或氧化钽(taox)。此外,图案化的第二介电层pa2可以包括有机材料,例如模制化合物、pa、pi、pbo或环氧基材料。此外,图案化的第二介电层pa2可以包括无机材料,例如siox、sinx或taox。图案化的第一介电层pa11的材料可以与图案化的第二介电层pa2的材料相同或不同。

25.在实施例中,图案化的第一导电层m11包括钛(ti)、钛钨合金(tiw)、镍(ni)、铜(cu)、钛铜合金(ticu)、银(ag)、金(au)或其它合适的导电材料。第二导电层m2可以包括铜(cu)、银(ag)、金(au)或其它合适的导电材料。

26.图1b是根据本公开的另一实施例的半导体封装结构20的截面图。

27.参考图1b,半导体封装结构20类似于参考图1a描述和绘示的半导体封装结构10,除了例如由第二导电层m2的凸起部分m2b和图案化的钝化层304界定凹部op4。凹部op4提供用于保持或容纳电导体146的空间。具体地,凹部op4由凸起部分m2b、图案化的钝化层304、图案化的第一介电层pa11和图案化的第一导电层m11所界定。凸起部分m2b从第二导电层m2的主体延伸到图案化的第一导电层m11中,并且与图案化的第一导电层m11邻接。第二导电层m2的凸起部分m2b和未被第一图案化介电层pa11掩蔽的图案化的第一导电层m11的部分m11d形成用于安置电导体146的凹部op4的底表面。电导体146将凸起部分m2b处的第二导电层m2电连接到一或多个第三半导体装置13。电导体146的一部分容纳在凹部op4中,并且电导体146的剩余部分从图案化的钝化层304的表面s3朝向再分布结构132突出。因此,与参考图1a描述和绘示的凹部op2类似,凹部op4为电导体提供了深根的空间,使得确保了相对可靠的电连接。另外,设置在图案化的第一介电层pa11和第三半导体装置13之间的图案化的钝化层304,其用于减轻由于电导体146在图案化的第一介电层pa11上产生的应力。

28.图2a至2u是截面图,其各自绘示根据本公开的实施例的制造如参考图1a所描述和绘示的半导体封装结构10的方法的一或多个阶段。

29.参考图2a,提供了第一载体201和第一释放膜202。第一载体201用于支撑随后形成或设置在其上的半导体部件、装置或结构。在实施例中,第一载体201包括厚度约为800微米(μm)的玻璃载体。第一释放膜202用于促进第一载体201从由第一载体201临时保持的半导体结构释放。在实施例中,第一释放膜202包括聚合物并且具有大约0.5μm的厚度。

30.接着,缓冲层203通过例如涂覆工艺形成在第一释放膜202上。缓冲层203可以包括钛(ti)、钛钨合金(tiw)、镍(ni)、铜(cu)、钛铜合金(ticu)、银(ag)、金(au)或其它合适的导电材料。在实施例中,缓冲层203具有大约0.3μm的厚度。

31.参考图2b,对缓冲层203进行图案化处理。使用例如旋涂技术将光致抗蚀剂(photoresist)放置在缓冲层203上,达到大约50μm至大约250μm的高度。一旦就位,然后可以通过经由光掩模205将光致抗蚀剂暴露于例如紫外光源(由虚线箭头表示)的能量源来图案化光致抗蚀剂。然后将显影剂施加到未被光掩模205掩蔽的光致抗蚀剂的部分上,以选择性地去除未掩蔽部分,得到图案化的光致抗蚀剂204。图案化的光致抗蚀剂204暴露缓冲层203的部分303。随后,缓冲层203的暴露部分303通过例如湿法蚀刻或干法蚀刻工艺去除,使用图案化的光致抗蚀剂204作为掩模,得到如图2c所绘示的图案化的缓冲层208。参考图2c,图案化的缓冲层208使释放膜202的部分通过开口308暴露。图案化的缓冲层208有助于界定随后形成的用于外部连接的电导体的位置。

32.参考图2d,第一再分布结构310形成在图案化的缓冲层208上。第一再分布结构310用于提供互连,并且可包括介电层和电路层。在本实施例中,第一再分布结构310包括构成“2p1m”结构的两个介电层pa1、pa2和一个电路层m。在形成第一再分布结构310时,首先,通过例如涂覆工艺在图案化的缓冲层208和释放膜202的暴露部分上形成第一介电层pa1。第一介电层pa1保持未图案化,然后在第一介电层pa1上形成第一导电层m1,随后形成第二导电层m2。第二导电层m2堆叠在第一导电层m1上,一起构成第一再分布结构310的电路层m。随后,在第一介电层pa1和电路层m上形成图案化的第二介电层pa2,通过开口312暴露第二导电层m2的部分。

33.在实施例中,第一介电层pa1和图案化的第二介电层pa2中的每一个具有大约10μm的厚度。第一导电层m1具有范围从大约0.1μm到大约0.2μm的厚度。第二导电层m2具有范围从大约3μm到大约7μm的厚度。

34.通过比较,在将参考图4a至4p进一步讨论的制造半导体封装结构的一些方法中,未将对应于本公开的缓冲层203的缓冲层图案化。此外,对应于本公开的第一介电层pa1的再分布结构中的第一介电层被图案化,从而暴露未图案化的缓冲层的部分。因此,在这些方法中,未图案化的缓冲层在暴露部分与稍后形成图案化的第一介电层中的电路层电连接,所述图案化的第一介电层在再分布结构中。这种配置可能不利地影响随后的电测试。在测试阶段期间,通过稍后形成在再分布结构上方的焊球向电路层施加测试信号。然而,由于未图案化的缓冲层和电路层是电连接的,因此测试信号可以由未图案化的缓冲层经由再分布结构路由到不同的焊球,导致严重的干扰。最坏的情况甚至可能导致0%的测试产率。此外,考虑到未图案化的缓冲层会干扰测试的事实,在这些方法中,可以在去除未图案化的缓冲层的稍后时间进行电测试。在这种情况下,将参考图5a至5e进一步讨论,需要额外的结合和剥离工艺再加上额外的载体,不可避免地增加了制造成本。

35.在本公开中,与上述方法不同,第一介电层pa1在测试之前没有被图案化。未图案化的第一介电层pa1使图案化的缓冲层208与电路层m电绝缘。具体地,第一导电层m1或第二导电层m2都没有电连接到图案化缓冲层208。因此,防止了在测试阶段期间在方法中发生的干扰。

36.在实施例中,第一介电层pa1可以包括有机材料,例如模制化合物、聚酰胺(pa)、聚酰亚胺(pi)、聚苯并唑(pbo)或环氧基材料。在另一实施例中,第一介电层pa1可以包括无机材料,例如氧化硅(siox)、氮化硅(sinx)或氧化钽(taox)。此外,图案化的第二介电层pa2可以包括有机材料,例如模制化合物、pa、pi、pbo或环氧基材料。此外,图案化的第二介电层pa2可以包括无机材料,例如siox、sinx或taox。第一介电层pa1的材料可以与第二介电层pa2的材料相同或不同。

37.第一导电层m1可以被用作种子层。在实施例中,第一导电层m1包括钛(ti)、钛钨合金(tiw)、镍(ni)、铜(cu)、钛铜合金(ticu)、银(ag)、金(au)或其它合适的导电材料。第二导电层m2可以包括cu、银(ag)、金(au)或其它合适的导电材料。在一些实施例中,第一导电层m1的材料与图案化的缓冲层208的材料相同,这进一步有助于界定随后形成的用于外部连接的电导体的位置,这将在后面详细描述。

38.参考图2e,图案化的导电层48形成在第一再分布结构310的表面310s上。形成图案化的导电层48的示范性工艺包括在第一再分布结构310的表面310s上形成图案化的干膜

410,通过开口312暴露第二导电层m2的部分,以及通过电镀将导电材料设置在暴露部分处的表面310s上。在实施例中,图案化的干膜410包括厚度大约为240μm的丙烯酸膜。另外,图案化的导电层48包括铜并且具有大约170μm和240μm之间的厚度。在形成图案化的导电层48之后,去除图案化的干膜410,得到如图2f所绘示的图案化的导电层48。

39.参考图2g,通过拾放工艺(pick-and-place process)将具有导电柱113'的第一半导体装置11设置在第一再分布结构310的表面310s上。第一半导体装置11包括应用处理器。可以使用粘合膜114来促进将第一半导体装置11附接到第一再分布结构310。

40.参考图2h,封装层420形成在第一再分布结构310上,覆盖图案化的导电层48、第一半导体装置11和导电柱113'。封装层420可以包括模制化合物。

41.参考图2i,然后通过例如诸如机械抛光工艺的研磨工艺减小封装层420的高度,得到减小(减薄)的封装层421。研磨工艺还降低了图案化的导电层48和导电柱113'的高度,从而分别形成图案化的导电层481和导电柱113。图案化的导电层481用于为第一半导体装置11提供互连。在一个实施例中,图案化的导电层481具有大约170μm的厚度。此外,导电柱113被用作第一半导体装置11的输入/输出(i/o)焊盘,并且具有大约25μm的厚度。

42.随后,在减小(减薄)封装层420之后,第二再分布结构320形成在减小的封装层421上,如图2j所绘示。第二再分布结构320可以包括在第一半导体装置11上方彼此堆叠的介电层,并且包括在介电层中的电路层,以提供第一半导体装置11和稍后将在第二再分布结构320上形成的电导体之间的电连接。在实施例中,第二再分布结构320包括“4p4m”配置。

43.参考图2k,电导体116安装在位于减小的封装层421上方的第二再分布结构320的表面320s上。另外,第二半导体装置12安装在第二再分布结构320的表面320s上。电导体116在第一半导体装置11和外部半导体装置或部件(未展示)之间提供电连接。电导体116可以包括焊球,所述焊球可以布置成球栅阵列(ball grid array)“bga”。电导体116可以包括受控塌陷芯片连接(controlled collapse chip connection,c4)凸块,所述凸块包括基于铅的或无铅的凸块或球。第二半导体装置12包括集成无源装置,所述无源装置又可以包括电阻器、电容器、电感器或其组合。在本实施例中,第二半导体装置12管芯向下附接到第二再分布结构320的表面320s上。底层填料127施加在第二半导体装置12和第二再分布结构320之间。底层填料127保护第二半导体装置12免受湿气、离子污染物、辐射和具有热、机械、冲击和振动应力的不利操作环境的影响。

44.随后,执行晶片级功能测试(由三角形表示),以确定迄今为止在载体201上制造的晶片中的半导体结构的电性能是否达到期望。如果是肯定的,则在图2l中,修整晶片的边缘(如表示动作的箭头所示)以去除过多的封装材料,以有助于随后的结合工艺。

45.参考图2m,粘合层510形成在第二再分布结构320的表面320s上,覆盖第二半导体装置12和电导体116。接着,将具有第二释放膜302的第二载体301结合到粘合层510上。粘合层510可以包括胶水,所述胶水有助于将第二载体301附接到第二再分布结构320。第二载体301和第二释放膜302分别包括与第一载体201和第一释放膜202相似或相同的材料,如参考图2a所描述和绘示的,并且分别具有与第一载体201和第一释放膜202相似或相同的尺寸。

46.参考图2n,在第二载体301与第二释放膜302结合之后,通过剥离工艺(de-bonding process)去除第一载体201和第一释放膜202,剥离工艺包括例如机械、化学、热或激光剥离工艺。在本实施例中,采用使用308nm准分子激光器的激光剥离工艺。从第一载体201侧引入

激光(由闪电表示)。未被图案化的缓冲层208所掩蔽的第一介电层pa1的部分pa0经由透明的第一载体201暴露于激光。受到激光辐射的暴露部分pa0从第一载体201上轻轻地被剥离。

47.接着,参考图2o,去除第一载体201和第一释放膜202,暴露图案化的缓冲层208 和第一介电层pa1的剥离部分pa0。第一介电层pa1的剥离部分pa0随后被去除,从而得到如图2p所绘示的图案化的第一介电层pa11。参考图2p,图案化的第一介电层pa11通过开口op1暴露第一导电层m1的部分。开口op1由图案化的缓冲层208、图案化的第一介电层pa11和第一导电层m1所界定,其中剥离部分pa0在被去除之前位于开口op1。

48.参考图2q,去除图案化的缓冲层208和第一导电层m1的暴露部分,得到图案化的第一导电层m11。图案化的第一导电层m11暴露第二导电层m2的部分。在实施例中,图案化的缓冲层208和第一导电层m1包括基本相同的材料,因此可以通过例如蚀刻工艺同时去除。因此,形成凹部op2,所述凹部op2由图案化的第一介电层pa11和图案化的第一导电层m11所界定以用于保持或容纳电导体。具体地,凹部op2由第二导电层m2的暴露部分以及图案化的第一介电层pa11和图案化的第一导电层m11界定。

49.参考图2r,通过预焊接工艺(pre-soldering process)在图案化的第一介电层pa11的与第一表面s1相对的第二表面s2上形成电导体126,填充由图案化的第一介电层pa11、图案化的第一导电层m11和第二导电层m2的暴露部分界定的凹部op2。

50.参考图2s,提供了封装装置130。封装装置130包括一或多个第三半导体装置13、电导体136和再分布结构132。第三半导体装置13被密封在封装层135中。设置在封装层135和电导体1136之间的再分布结构132,其提供半导体装置13通过电导体136到另一半导体装置的电连接。如图2t所绘示,通过回流工艺(reflowing process)将图案化的第一介电层pa11的表面s2上的电导体126和封装装置130的电导体136连接在一起,形成电导体146。参考图2t,然后将底部填充材料227施加在第一再分布结构310和封装装置130之间。底层填料227保护第三半导体装置13免受湿气、离子污染物、辐射和具有热、机械、冲击和振动应力的不利操作环境的影响。

51.随后,参考图2u,第二载体301借助于第二释放膜302通过例如激光剥离工艺去除。然后,也去除粘合层510,以暴露在第二再分布结构320的表面320s上的电导体116和第二半导体装置12。接下来,执行分割工艺以将晶片切割成单独的装置单元,每个装置单元与参考图1a所描述和绘示的半导体装置封装10相似或相同。

52.图3a至3k是截面图,其各自绘示根据本公开的实施例的制造如参考图1b所描述和绘示的半导体封装结构20的方法的一或多个阶段。

53.参考图3a,在缓冲层203形成在第一载体201上方之后,对缓冲层203进行图案化处理。最初,类似于参考图2b描述和绘示的图案化的光致抗蚀剂的形成方式,图案化的钝化层304使用掩模205通过例如涂覆工艺形成在缓冲层203上,随后进行暴露和显影处理。此后,固化图案化的钝化层304。在实施例中,图案化的钝化层304包括聚酰亚胺。另外,图案化的钝化层304具有大约7μm的厚度。随后,缓冲层203的被图案化的钝化层304从开口303暴露的部分通过例如湿法蚀刻或干法蚀刻工艺,使用图案化的钝化层304作为掩模被去除,得到如图3b所绘示的图案化的缓冲层208。图案化的钝化层304和图案化的缓冲层208将第一释放膜202的部分从开口303暴露。图案化的缓冲层208有助于界定随后形成的用于外部连接的电导体的位置。类似地,图案化的钝化层304有助于界定电导体的位置。

54.参考图3c,第一再分布结构310的第一介电层pa1通过例如涂覆工艺形成在图案化的钝化层304和第一释放膜202的暴露部分上。第一介电层pa1保持未图案化直到进行测试。第一介电层pa1与图案化的钝化层304的轮廓共形。这种共形拓扑在参考图2d所描述和绘示的实施例中不重要,因此没有具体示出,因为图案化的缓冲层208的示范性厚度为0.3μm,而其上的第一介电层pa1为10μm。然而,在图3c的本实施例中,对于7μm的图案化的钝化层304,共形拓扑是相对重要的。如图3c所展示的,共形拓扑使得第一介电层pa1从上表面p1处的第一转折点向下表面p2处的第二转折点逐渐下降,然后反之亦然上升。在截面图中,在横向方向上,在图案化的钝化层304的侧壁304w和第二转向点之间存在距离d。同样参考图1b,距离d确定了图案化的第一导电层m11的量,所述第一导电层m11可以在侧壁304w上方延伸到凹部op4中,这将通过参考下面的描述变得清楚和容易理解。

55.参考图3d,在第一介电层pa1上形成第一导电层m1,随后形成第二导电层m2。第二导电层m2堆叠在第一导电层m1上,一起构成第一再分布结构310的电路层m。作为薄膜,第一导电层m1与第一介电层pa1共形并遵循所述轮廓。具体地,第一导电层m1的第一部分设置在第一介电层pa1的上表面p1上,第一导电层m1的第二部分设置在第一介电层pa1的下表面p2上。对于第二导电层m2,共形拓扑不重要,因为第二导电层m2明显比第一导电层m1厚,考虑到前面参考图2d所讨论的示范性尺寸。因此,当第二导电层m2形成在第一导电层m1上时,第二导电层m2的部分,以下称为凸起部分m2b,设置在第一导电层m1的第二部分上。

56.随后,参考图3e,在第一介电层pa1和电路层m上形成图案化的第二介电层pa2,通过开口312暴露第二导电层m2的部分。

57.参考图3f,然后在第一再分布结构310上或上方形成或设置如参考图2e至2m所描述和绘示的其它半导体部件、装置和结构。应当注意,已经在制造时对半导体封装结构20的性能进行测试。可以在图2e至2m的实施例中找到这些部件、装置和结构的示范性制造工艺、材料和尺寸。因此,不再进一步讨论这些由标记为2e2m的框共同表示的半导体部件、装置和结构。

58.接下来,参考图3g,在测试和第二载体301与第二释放膜302结合之后,通过包括例如激光剥离工艺的剥离工艺去除第一载体201和第一释放膜202。未被图案化的缓冲层208掩蔽的第一介电层pa1的部分pa00经由透明的第一载体201暴露于激光。受到激光辐射的暴露部分pa00从第一载体201上轻轻地剥离,如图3h所绘示。

59.参考图3i,去除第一载体201和第一释放膜202,暴露图案化的缓冲层208和第一介电层pa1的剥离部分pa00。第一介电层pa1的剥离部分pa00随后被去除,得到如图3j所绘示的图案化的第一介电层pa11。参考图3j,图案化的第一介电层pa11通过开口op3暴露第一导电层m1的部分。开口op3由图案化的缓冲层208、图案化的第一介电层pa11、图案化的钝化层304和第一导电层m1界定,其中剥离部分pa00在被去除之前位于开口op3。

60.参考图3k,去除图案化的缓冲层208和第一导电层m1的暴露部分,得到图案化的第一导电层m11。图案化的第一导电层m11暴露第二导电层m2的凸起部分m2b。在实施例中,图案化的缓冲层208和第一导电层m1包括基本相同的材料,因此可以通过例如蚀刻工艺同时去除。因此,形成凹部op4,所述凹部op4由图案化的第一介电层pa11和图案化的钝化层304所界定以用于保持或容纳电导体。图案化的第一导电层m11包括未被图案化的第一介电层pa11掩蔽的部分m11d,并且每个所述部分m11d在图案化的钝化层304的对应侧壁304w上延

伸距离d。部分m11d与第二导电层m2的凸起部分m2b邻接,并且与凸起部分m2b一起形成用于安置电导体146的凹部op4的底表面。因此,凹部op4由第二导电层m2的凸起部分m2b以及图案化的第一介电层pa11和图案化的钝化层304界定。具体地,凹部op4由图案化的第一导电层m11的未掩蔽部分m11d、第二导电层m2的凸起部分m2b、图案化的第一介电层pa11和图案化的钝化层304界定。

61.随后,在图案化的钝化层304和第二导电层m2的凸起部分m2b上或上方形成或设置如参考图2r至2u所描述和绘示的其它半导体部件、装置和结构。在图2r至2u的实施例中可找到这些部件、装置和结构的示范性制造工艺、材料和尺寸,并且因此不再进一步讨论。因此,获得与参考图1b所描述和绘示的半导体封装结构20相似或相同的半导体封装结构。

62.图4a至4p是截面图,其各自绘示与参考图2a至2u所描述和绘示的方法相比,制造半导体封装结构的方法的一或多个阶段。

63.参考图4a,提供了第一载体401和第一释放膜402。接着,缓冲层403形成在第一释放膜402上。

64.参考图4b,第一再分布结构404形成在缓冲层203上。第一再分布结构404包括第一介电层404pa1、第二介电层404pa2和导电层404m1。在形成第一再分布结构404时,图案化第一介电层404pa1,从而暴露缓冲层403的部分。随后,在第一介电层404pa1上形成导电层404m1,从而在暴露部分与缓冲层403电连接。

65.接下来,参考图4c,图案化的光致抗蚀剂层405形成在第二介电层404pa2上,暴露导电层404m1的部分。导电柱(conductive pillars)406随后形成在图案化的光致抗蚀剂层405中以在导电层404m1的暴露部分处电连接到第一再分布结构404。然后去除图案化的光致抗蚀剂层405,如图4d所展示的。

66.参考图4e,第一半导体装置411附接在第二介电层404pa2上,借助于粘合层414。第一半导体装置411包括导电柱(conductive studs)413。

67.然后,参考图4f,封装层500形成在第一再分布结构404上,覆盖第二介电层404pa2、导电柱406和导电柱413。封装层500随后在抛光过程中高度减小,导致封装层520减小,如图4g所展示的。减小的封装层520暴露导电柱416和导电柱423,所述导电柱416和导电柱423在抛光工艺期间还可以分别从导电柱406和导电柱413减小高度。

68.接下来,参考图4h,第二再分布结构503形成在减小的封装层520上。第二再分布结构503包括与第一半导体装置411的导电柱423和导电柱416电连接的导电层(未展示),其又与第一再分布结构404和缓冲层403电连接。

69.参考图4i,电导体516安装在第二再分布结构503上。另外,第二半导体装置412安装在第二再分布结构503上。底层填料427施加在第二半导体装置412和第二再分布结构503之间。随后,执行晶片级功能测试(由三角形表示),以确定迄今为止在载体401上制造的晶片中的半导体结构的电性能是否达到期望。然而,由于缓冲层403未被图案化,因此在测试期间,在第一载体401上展开的未图案化的缓冲层403可以与电导体516的全部或至少大部分经由第一再分布结构404、导电柱416和第二再分布结构503电连接。因此,在测试期间从电导体516施加的测试信号易于由于信号干扰而产生误差。相反,在根据本公开的实施例中,缓冲层203(图2b、图3a)被图案化,从而形成图案化的缓冲层208(图2c、图3b),这有助于界定随后形成的用于外部连接的电导体的位置。此外,第一介电层pa1在测试之前保持未图

案化。未图案化的第一介电层pa1电隔离图案化的缓冲层208以有助于测试。

70.然后,在图4j中,修整晶片的边缘(如表示动作的箭头所示)以去除过量的封装材料,以有助于随后的结合工艺。参考图4k,粘合层518形成在第二再分布结构503的表面503s上,覆盖第二半导体装置412和电导体516。接着,将具有第二释放膜502的第二载体501结合到粘合层518上。

71.参考图4l,在第二载体501与第二释放膜502结合之后,通过剥离工艺去除第一载体401和第一释放膜402,暴露缓冲层403。之后,在蚀刻工艺中去除缓冲层403,暴露第一再分布结构404的导电层404m1。接下来,参考图4m,将电导体526安装在导电层404m1上以为第一再分布结构404提供电连接。

72.参考图4n,提供了封装装置530。封装装置530包括一或多个第三半导体装置413和再分布结构580。第三半导体装置413被密封在封装层582中。再分布结构580设置在封装层582和电导体526之间,为半导体装置413提供电连接。参考图4o,然后将底部填充材料437施加在第一再分布结构404和封装装置530之间。

73.随后,参考图4p,第二载体501与第二释放膜502一起通过剥离工艺去除。然后,也去除粘合层518,暴露电导体516和第二半导体装置412。接下来,执行分割工艺以将晶片切割成单独的装置单元。

74.图5a至5e是截面图,其各自绘示与参考图2a至2u所描述和绘示的方法相比,制造半导体封装结构的另一方法的一或多个阶段。由于图4i中对缓冲层403的测试此时可能失败,因此可以在稍后去除缓冲层403时进行测试。

75.再参考图4l,在第一载体401、第一释放膜402和随后的缓冲层403被去除之后,现在参考图5a,第三载体601与第三释放膜602一起借助于粘合层618被附接到第一再分布结构404。然后,如图5b所展示的,去除第二载体501、第二释放膜502及其相关联的粘合层518,暴露电导体516。如图5c所展示的,由于缓冲层403被去除并且电导体516被暴露,所以进行测试。

76.在测试之后,参考图5d,第四载体701与第四释放膜702一起借助于粘合层718被附接到再分布结构503的表面503s上。接下来,去除第三载体601、第三释放膜602及其相关联的粘合层618,暴露第一再分布结构404的导电层404m1。然后,参考图5e,将电导体526安装在导电层404m1上以为第一再分布结构404提供电连接。随后的工艺与参考图4n、4o和4p所描述和绘示的处理相似或相同,因此不再讨论。

77.为了延迟测试,与根据本公开的实施例中的方法相比,需要额外的第三载体601和第四载体701、额外的第三释放膜602和第四释放膜702、额外的粘合层618、粘合层718。此外,还需要额外的结合和剥离工艺。因此,参考图5a至5e描述和绘示的方法由于根据本公开在图2a至2u或图3a至3k中描述和绘示的方法而不是成本有效的。

78.如本文所用,术语“大约”、“基本上”、“基本”和“约”用于描述和说明小的变化。当与事件或情况结合使用时,该术语可以指其中事件或情况精确发生的情况以及其中事件或情况非常近似地发生的情况。另外,量、比率和其它数值有时在本文中以范围形式给出。应当理解,这样的范围格式是为了方便和简洁而使用的,并且应当被灵活地理解为包括明确指定为范围的界限的数值,而且还包括包含在该范围内的所有单独的数值或子范围,其中每个数值和子范围被视为已明确指定。

79.虽然已经参考本公开的具体实施例描述和绘示了本公开,但是这些描述和绘示不是限制性的。本领域内的技术人员应当理解,在不脱离由所附权利要求限定的本公开的真实精神和范围的情况下,可以进行各种改变并且可以替换等同物。附图不必按比例绘制。由于制造过程和公差,本公开中的工技再现与实际设备之间可能存在区别。可以存在没有具体示出的本公开的其它实施例。说明书和附图被认为是说明性的而不是限制性的。可以进行修改以使特定的情况、材料、物质组成、方法或过程适应本公开的目的、精神和范围。所有这些修改都在所附权利要求的范围内。虽然已经参考以特定顺序执行的特定操作描述了在此公开的方法,但是应当理解,在不脱离本公开的教导的情况下,这些操作可以被组合、细分或重新排序以形成等效方法。因此,除非在此特别指出,否则操作的顺序和分组不是对本公开的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1